又是一个熟悉的名词,PLL。

硬件准备

ADSP-EDU-BF533:BF533开发板

AD-HP530ICE:ADI DSP仿真器

软件准备

Visual DSP++软件

硬件链接

功能介绍

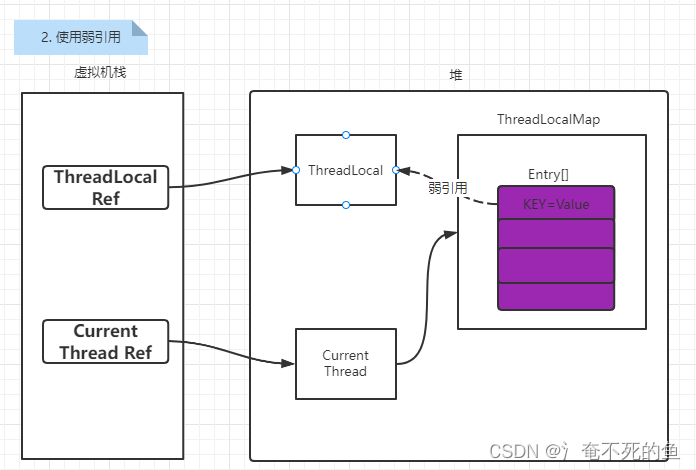

PLL(Phase Locked Loop)是 ADSP-BF53x 的内核和时钟设置的机制,叫做锁相环。通过 PLL 配置当前处理器工作的内核和系统时钟。

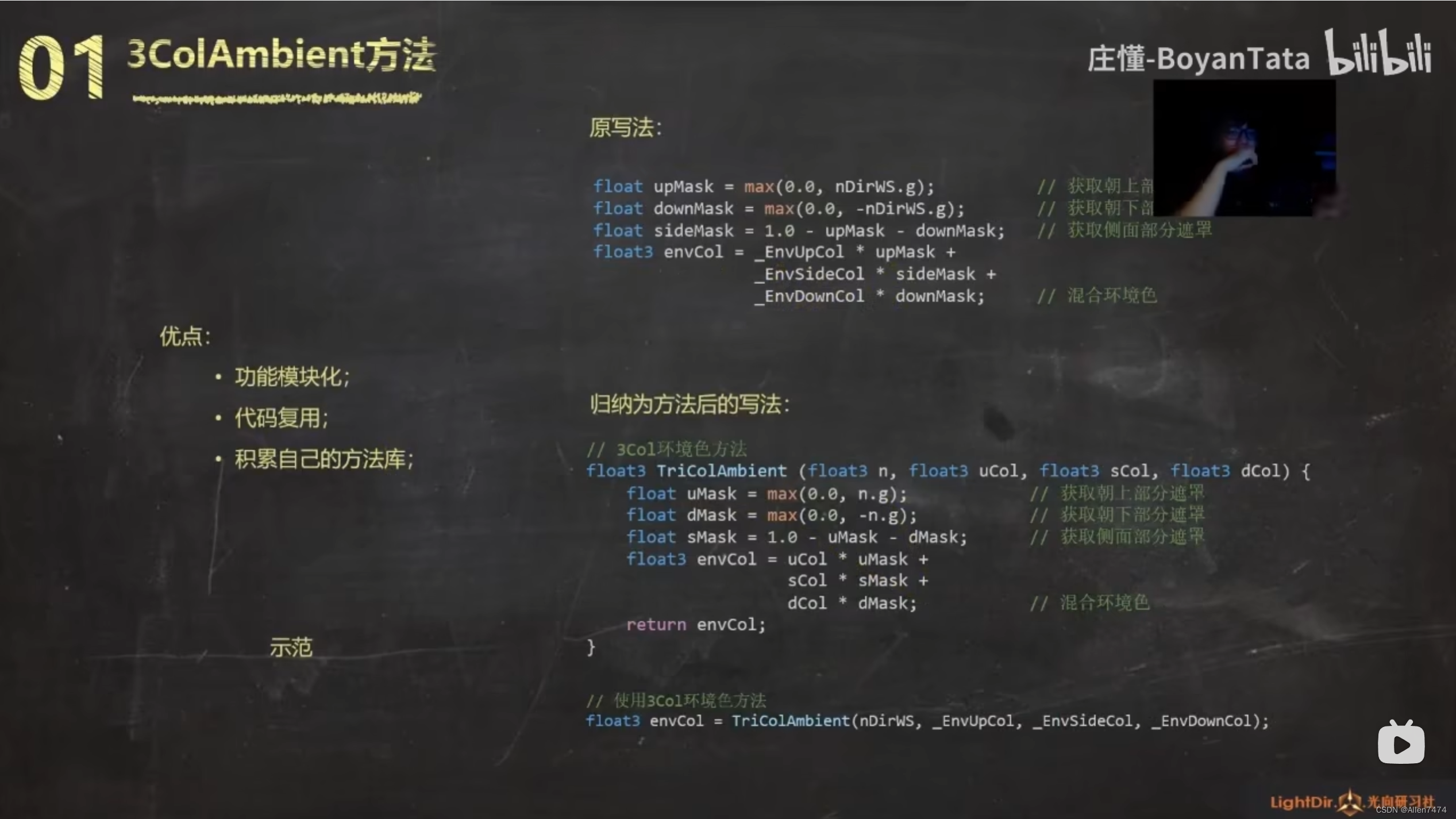

PLL 机制如图:

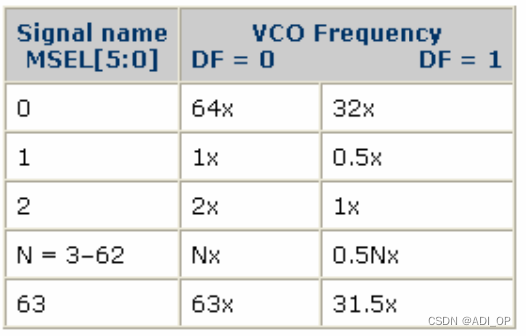

输入时钟送给 ADSP-BF533 后,通过 DF 设置是否对输入时钟分频,然后将根据 MSEL 的值对时钟进行倍频,倍频后将时钟送给 VCO,由 VCO 根据设置的分频系数,分出内核时钟和系统时钟。

MSEL 占用 6Bit,最大可设置 64 倍倍频。通常情况下,该倍频频率不要超过芯片允许的最大频率。

内核时钟分频系数占 2Bit,最大可设置 8 倍分频,当为 00 时,内核时钟等于 VCO 时钟。设置的内核时钟不要超过芯片允许的最高频率。

系统时钟分频系数占 4bit,最大进行 15 倍的分频。设置的系统时钟不要超过 133MHz。

寄存器说明

PLL_DIV:PLL 分频寄存器,设置系统时钟和内核时钟分频系数

PLL_CTL:PLL 控制寄存器,设置 VCO 倍频系数和一些控制开关

PLL_STAT:PLL 状态寄存器,获取芯片当前工作的状态

PLL_LOCKCNT:PLL 计数器,用于设置计数时钟

核心代码分析

*pPLL_DIV = pssel; //设置系统时钟分频系数,内核不做分频

asm(“ssync;”); //系统同步

new_PLL_CTL = (pmsel & 0x3f) << 9; //将 VCO 倍频系数移位至需设置的位置

*pSIC_IWR |= 0xffffffff; //将系统中断唤醒使能

if (new_PLL_CTL != *pPLL_CTL) //判断是否已经配置过倍频系数

{

*pPLL_CTL = new_PLL_CTL; //配置倍频系数

asm(“ssync;”); //系统同步

asm(“idle;”); //将处理器设置为空闲

}

注意:配置完 PLL 后,系统必须将系统设置为空闲后,系统再一次唤醒后,设置的值才会生效。

代码实现功能

代码实现了将内核时钟配置为 16 倍倍频,将系统时钟配置为 4 倍分频。板卡上输入时钟为 25MHz,所以 VCO时钟配置后为 25*16 =400MHz,内核时钟没有做分频,所以内核时钟等于 VCO 时钟,也为 400MHz,系统时钟为 400/3=100MHz。

运行代码后,处理器的内核时钟会运行在 400MHz,系统时钟运行在100MHz。

完整代码

#include <cdefBF533.h>

void Set_PLL(int pmsel,int pssel) //内核时钟 = 输入时钟pmsel; 系统时钟 = 输入时钟pmsel/pssel

{

int new_PLL_CTL;

*pPLL_DIV = pssel;

asm(“ssync;”);

new_PLL_CTL = (pmsel & 0x3f) << 9;

*pSIC_IWR |= 0xffffffff;

if (new_PLL_CTL != *pPLL_CTL)

{

*pPLL_CTL = new_PLL_CTL;

asm(“ssync;”);

asm(“idle;”);

}

}

int main()

{

Set_PLL(16,4); //内核时钟 = 2516 = 400MHz ; 系统时钟 = 2516/4 = 100MHz

}

![[附源码]Python计算机毕业设计Django在线项目管理](https://img-blog.csdnimg.cn/b82537c7679b4fcf8f5eca441af35ade.png)