目录

- 1、前言

- 2、我目前已有的SDI编解码方案

- 3、GS2971/GS2972芯片解读

- GS2971解读

- GS2972解读

- 4、详细设计方案

- 5、vivado工程1解读

- 硬件逻辑工程

- 软件SDK工程

- 6、vivado工程2解读

- 硬件逻辑工程

- 软件SDK工程

- 7、上板调试验证

- 8、福利:工程代码的获取

1、前言

FPGA实现SDI视频编解码目前有两种方案:

一是使用专用编解码芯片,比如典型的接收器GS2971,发送器GS2972,优点是简单,比如GS2971直接将SDI解码为并行的YCRCB,缺点是成本较高,可以百度一下GS2971的价格;

另一种方案是使用FPGA实现编解码,利用FPGA的GTP/GTX资源实现解串,优点是合理利用了FPGA资源,GTP/GTX资源不用白不用,缺点是操作难度大一些,对FPGA水平要求较高;我的主页有SDI专栏,里面包含了利用FPGA的GTP/GTX资源的部分工程源码;

本文详细描述了FPGA基于GS2971/GS2972收发SDI视频的实现设计方案,工程代码编译通过后上板调试验证,文章末尾有演示视频,可直接项目移植,适用于在校学生做毕业设计、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的数字成像和图像传输领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

本设计提供两套vivado工程;

一是GS2971解码SDI视频,经DDR图像缓存后由HDMI输出;SDI 1080P@30Hz帧视频输入;1080P@60Hz帧输出;

二是GS2971解码SDI视频,经DDR图像缓存后由GS2972编码SDI输出;SDI 1080P@30Hz帧视频输入;SDI 1080P@30Hz帧输出;

2、我目前已有的SDI编解码方案

我的博客主页开设有SDI视频专栏,里面全是FPGA编解码SDI的工程源码及博客介绍;既有基于GS2971/GS2972的SDI编解码,也有基于GTP/GTX资源的SDI编解码;专栏地址链接:https://blog.csdn.net/qq_41667729/category_12243350.html?spm=1001.2014.3001.5482

3、GS2971/GS2972芯片解读

GS2971解读

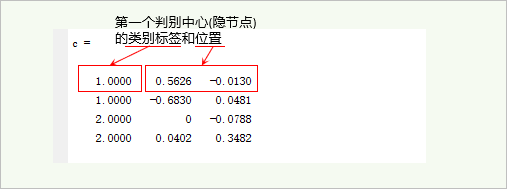

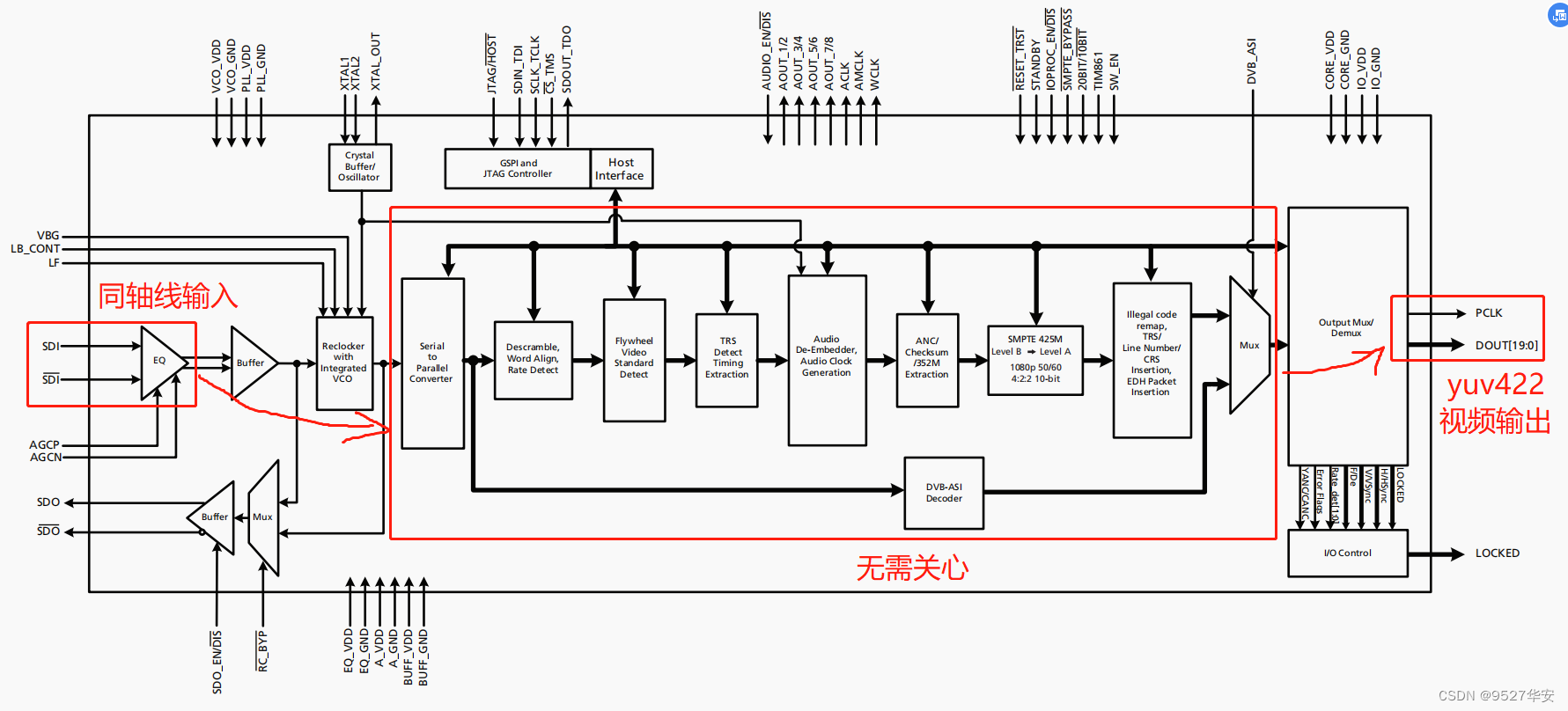

GS2971是SDI解码芯片,将输入的SDI视频解码为yuv422视频输出;GS2971数据手册框图如下:

GS2971数据手册共152页,但作为一名FPGA开发者而言,大多数都是废话,我们只需关心视频的输入与输出格式即可;

由上图可知,GS2971输入为SDI视频,输出为yuv422视频流;中间的解码和转换过程我们无需关心,这就是数字IC的魅力,将复杂的电路封装为专用IC,用户仅需读读手册即可傻瓜式使用;

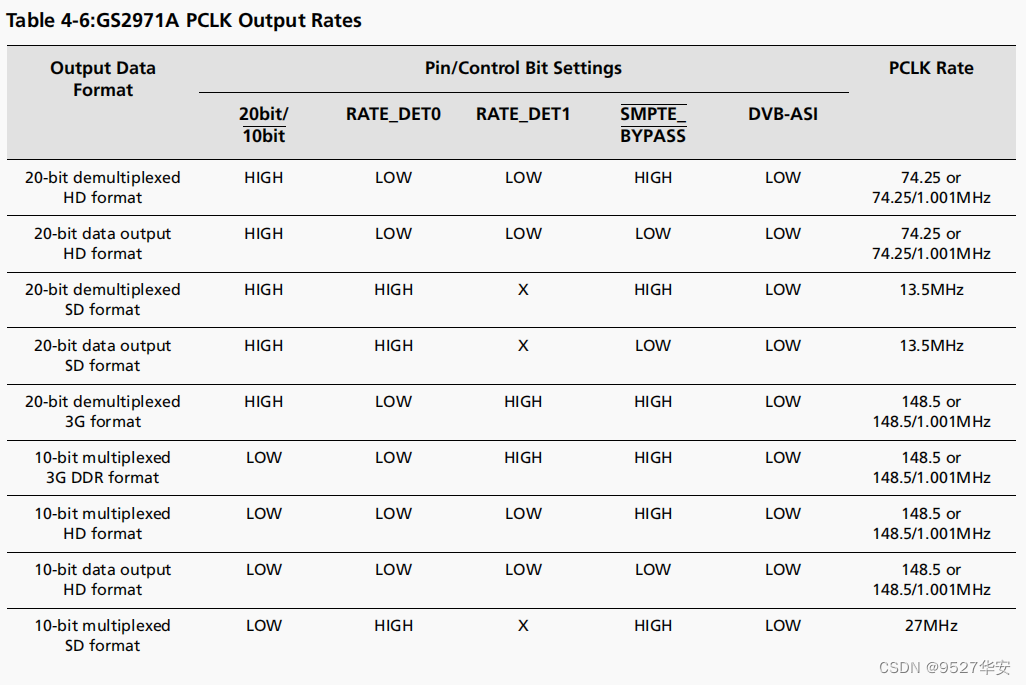

输出yuv422视频流属于VGA视频格式,有像素时钟PCLK,行同步信号HS,场同步信号VS,数据有效信号DE,20位像素数据DOUT;GS2971输出视频直接与输入的SDI视频速率关联,以3G-SDI为例,输入3G-SDI,输出视频像素时钟则为148.5M,具体见手册截图:

另外,GS2971不需要软件配置,电阻上下拉即可完成配置,这部分是画原理图的硬件工程师关心的事,不再多说;

GS2972解读

GS2972的作用正好与GS2971相反,是SDI编码芯片,将输入的yuv422视频编码为SDI视频输出;芯片一样不需要软件配置,所以这里就不多说了;

4、详细设计方案

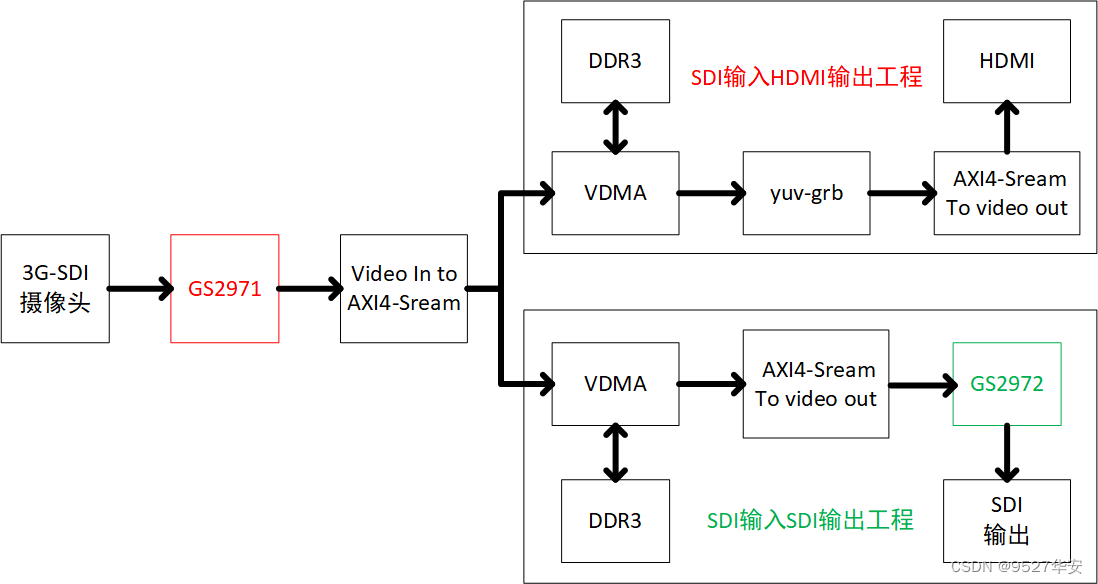

本设计提供了两套工程;

工程1:SDI输入,经GS2971解码后缓存DDR3,最后由HDMI输出;

工程2:SDI输入,经GS2971解码后缓存DDR3,最后由GS2971编码后SDI输出;

设计框图如下:两个工程一同画在框图中;

5、vivado工程1解读

硬件逻辑工程

开发板FPGA型号:Xilinx–xc7k325tffg676-2;

开发环境:Vivado2019.1;

输入:3G-SDI视频;

输出:HDMI,1080P;

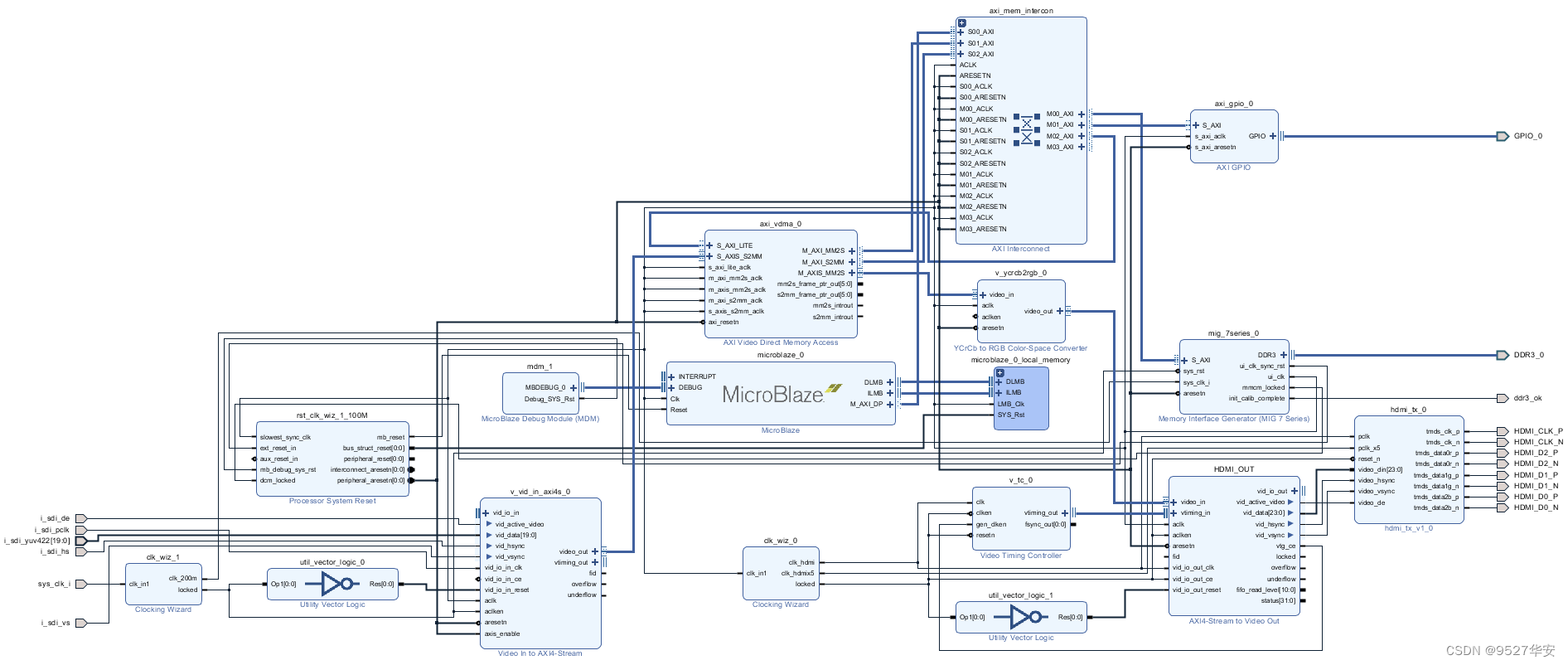

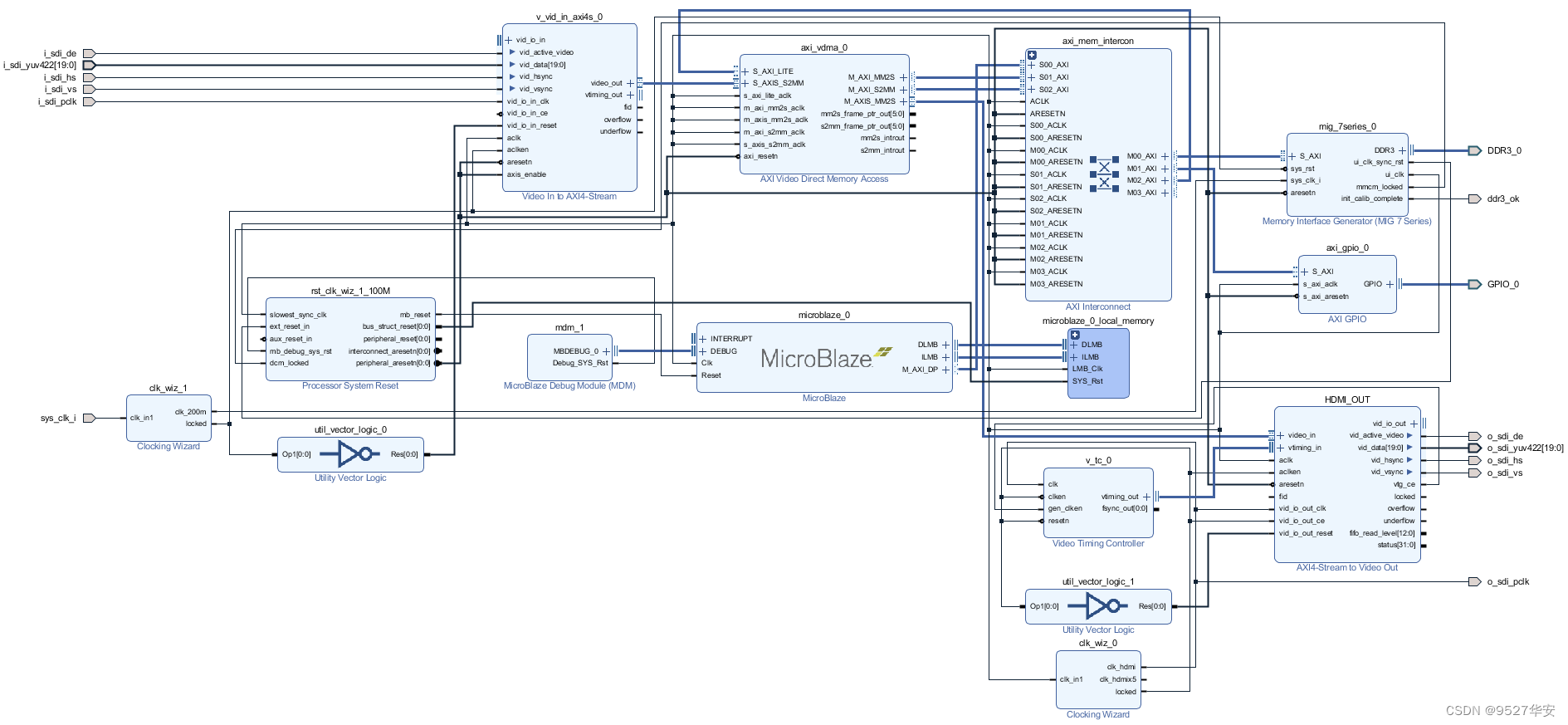

工程Block Design如下:

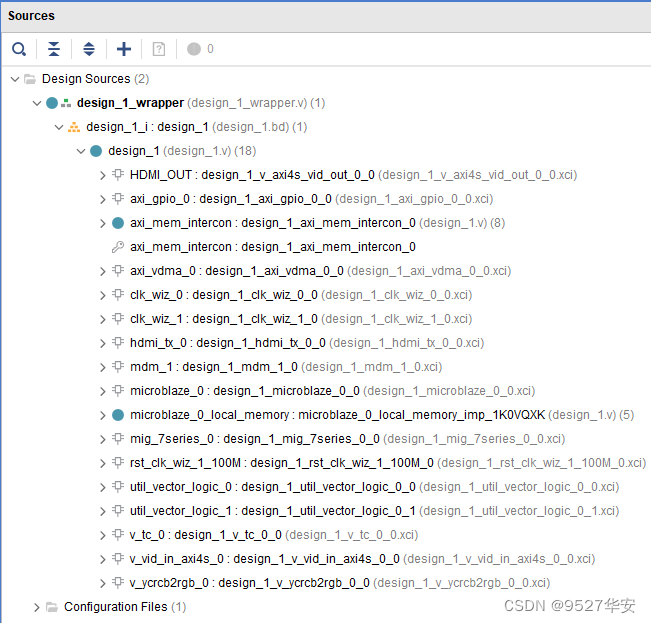

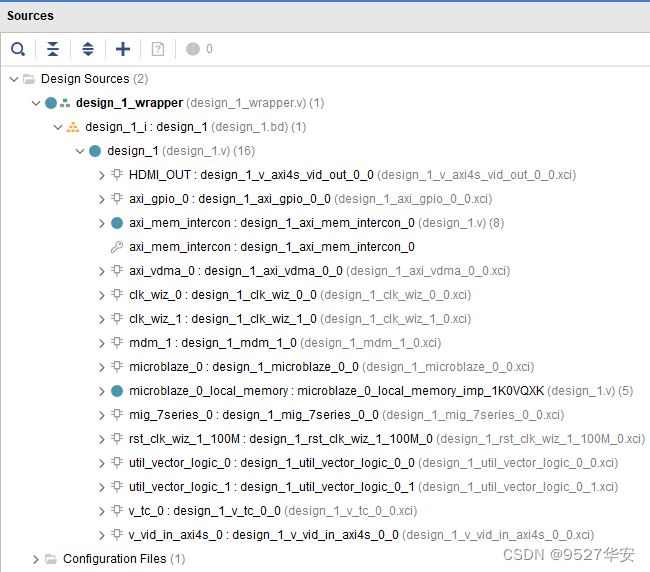

工程代码架构如下:

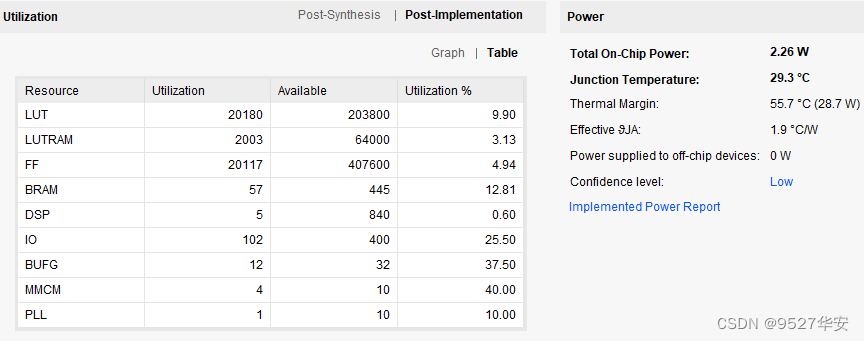

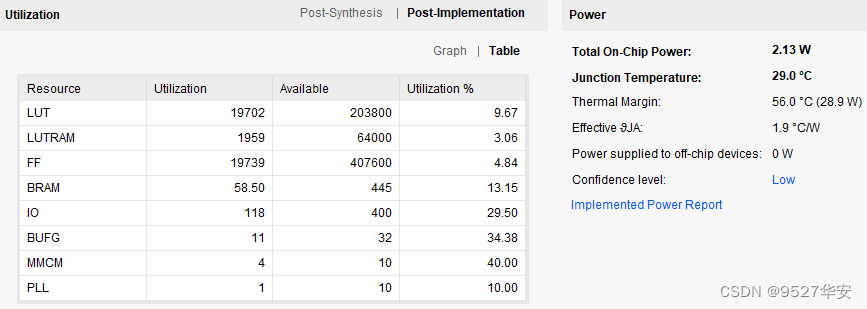

资源消耗和功耗预估如下:

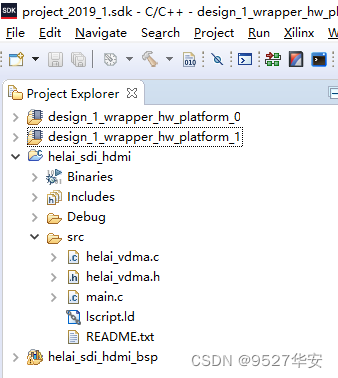

软件SDK工程

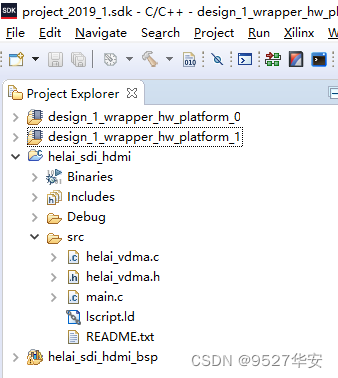

软件SDK工程如下:只做了VDMA的配置;

主函数如下:

#include <stdio.h>

#include "xgpio.h"

#include "unistd.h"

#include "helai_vdma.h"

XGpio_Config *XGpioCfg;

XGpio led_gpio;

#define AXI_GPIO_DEVICE_ID XPAR_GPIO_0_DEVICE_ID

int main(){

XGpioCfg = XGpio_LookupConfig(AXI_GPIO_DEVICE_ID);

XGpio_CfgInitialize(&led_gpio, XGpioCfg, XGpioCfg->BaseAddress);

XGpio_SetDataDirection(&led_gpio, 1, 0); //output

XGpio_DiscreteWrite(&led_gpio, 1, 0);

helai_vdma();

while(1){

usleep(500000);

XGpio_DiscreteWrite(&led_gpio, 1, 1);

usleep(500000);

XGpio_DiscreteWrite(&led_gpio, 1, 0);

}

}

6、vivado工程2解读

硬件逻辑工程

开发板FPGA型号:Xilinx–xc7k325tffg676-2;

开发环境:Vivado2019.1;

输入:3G-SDI视频;

输出:3G-SDI视频;

工程Block Design如下:

工程代码架构如下:

资源消耗和功耗预估如下:

软件SDK工程

软件SDK工程如下:只做了VDMA的配置;

主函数如下:

#include <stdio.h>

#include "xgpio.h"

#include "unistd.h"

#include "helai_vdma.h"

XGpio_Config *XGpioCfg;

XGpio led_gpio;

#define AXI_GPIO_DEVICE_ID XPAR_GPIO_0_DEVICE_ID

int main(){

XGpioCfg = XGpio_LookupConfig(AXI_GPIO_DEVICE_ID);

XGpio_CfgInitialize(&led_gpio, XGpioCfg, XGpioCfg->BaseAddress);

XGpio_SetDataDirection(&led_gpio, 1, 0); //output

XGpio_DiscreteWrite(&led_gpio, 1, 0);

helai_vdma();

while(1){

usleep(500000);

XGpio_DiscreteWrite(&led_gpio, 1, 1);

usleep(500000);

XGpio_DiscreteWrite(&led_gpio, 1, 0);

}

}

7、上板调试验证

以工程1为例,SDI进,HDMI输出效果如下:

8、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下: