摘要:之前的文章对aurora、chip2chip以及Ethernet这三个IP都进行介绍、仿真和使用说明。但是在实际使用中一定没有那么简单,在复杂联合使用的情况下,肯定会碰到各种各样的问题。此系列文章主要说明如何解决联合使用情况下碰到的一系列问题。

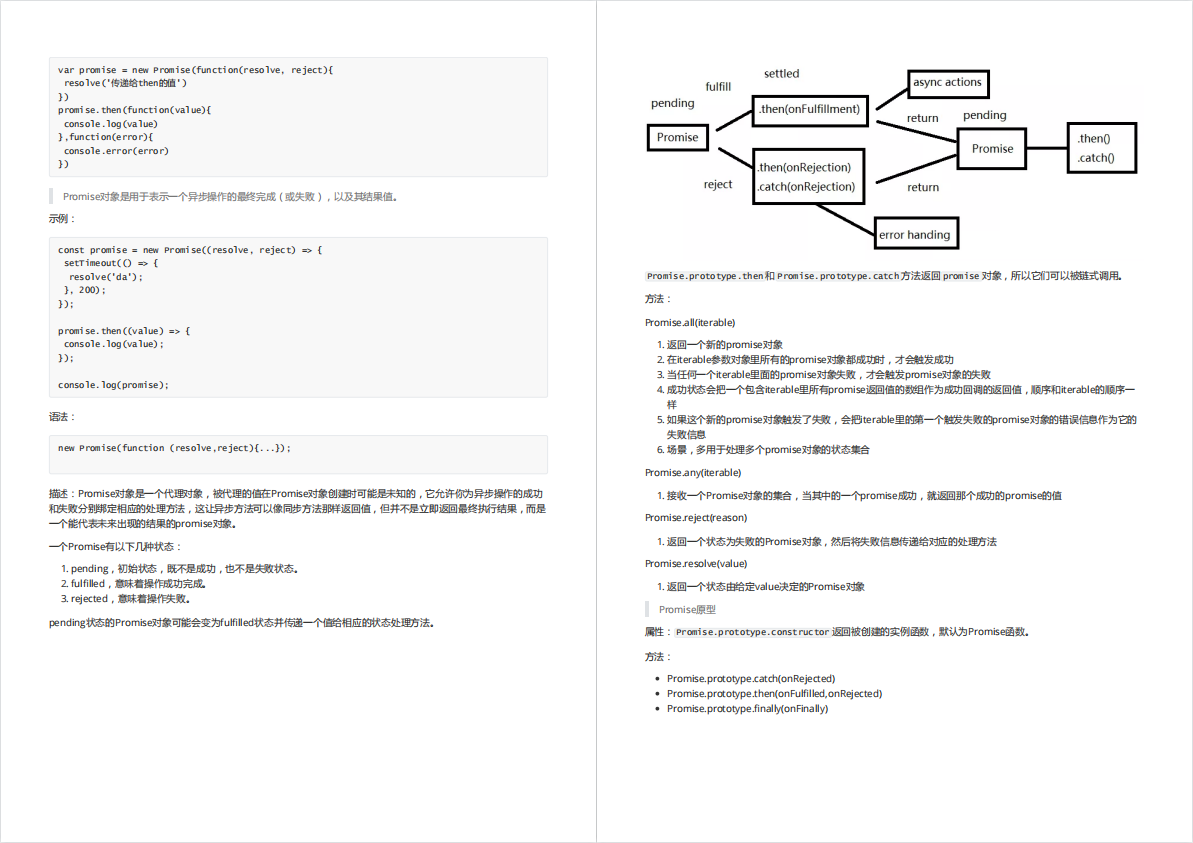

使用场景:

在只有一对gt差分时钟的情况下,让aurora、chip2chip和Ethernet三个ip共用一个gt时钟。

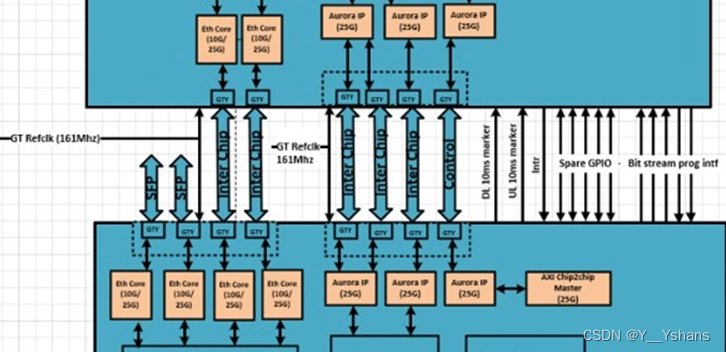

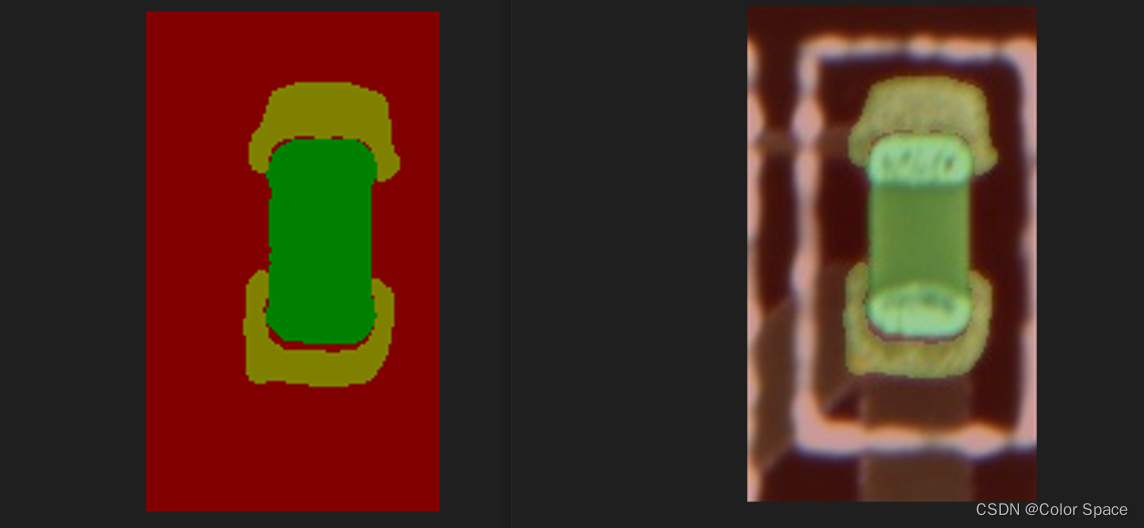

如图所示,这里有六个serdes和两个SFP。KU3P在上方,ZU67在下方。

这里不能简单的理解为zu67需要四个Ethernet、三个aurora、一个chip2chip。如果这样子去做工程需要多出很多工作量。并且Xilinx的IP里面提供了Lane的选择,可以简化工程。后文也会提到。

同时也需要验证两块板子的aurora通信、chip2chip通信以及以太网回环测试。

难点:vivado工具不支持简单的连线共用,必须修改代码。

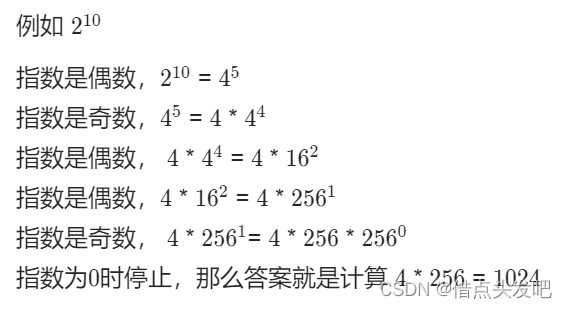

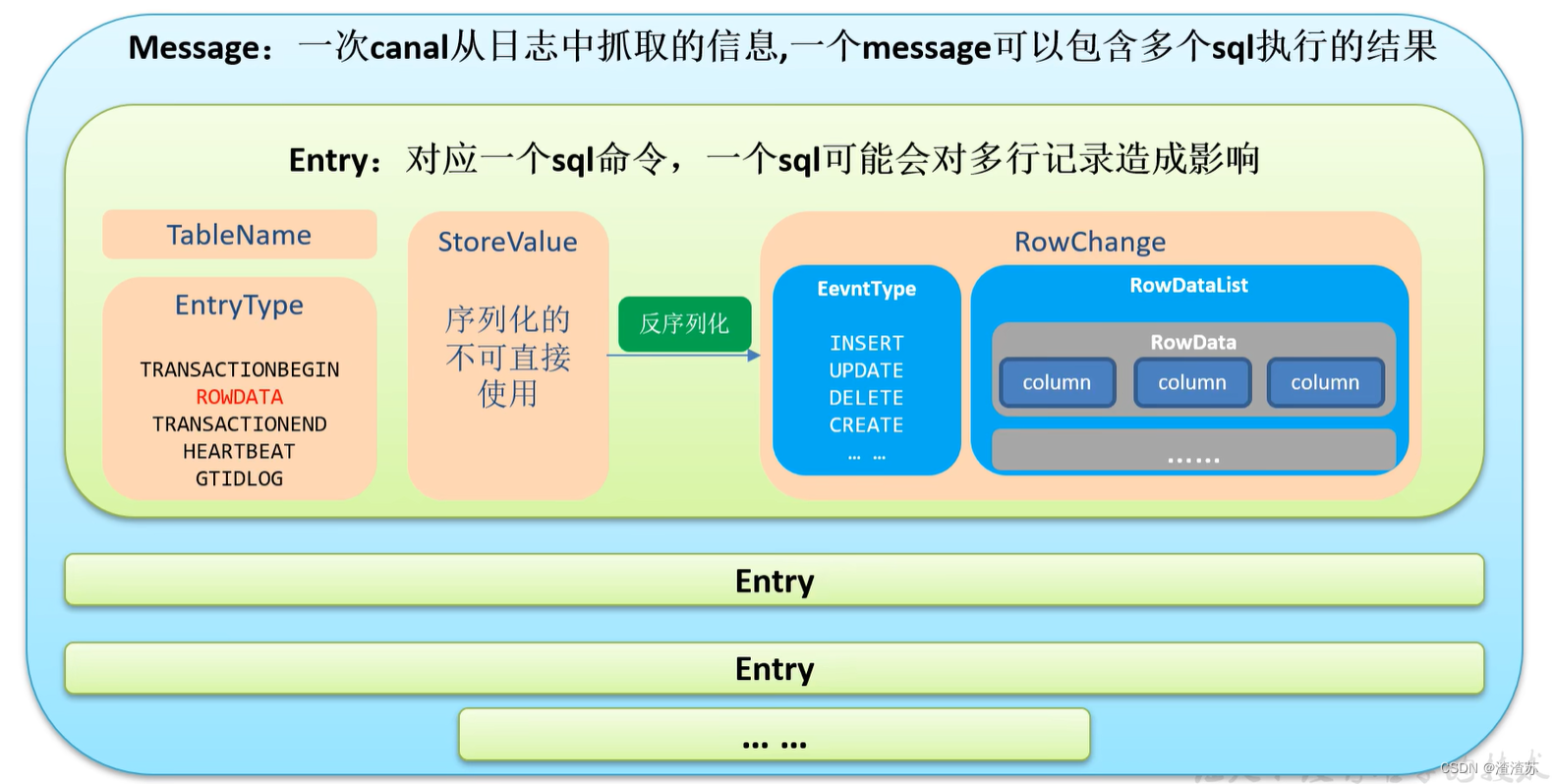

1. Chip2chip IP

physical layer configuration options里面需要注意一下:

phy type和pyh width都是根据硬件来的,硬件的pin脚多的话,可以用select io。如果没有那么多pin脚,只有serdes,那只能用Aurora的协议了。

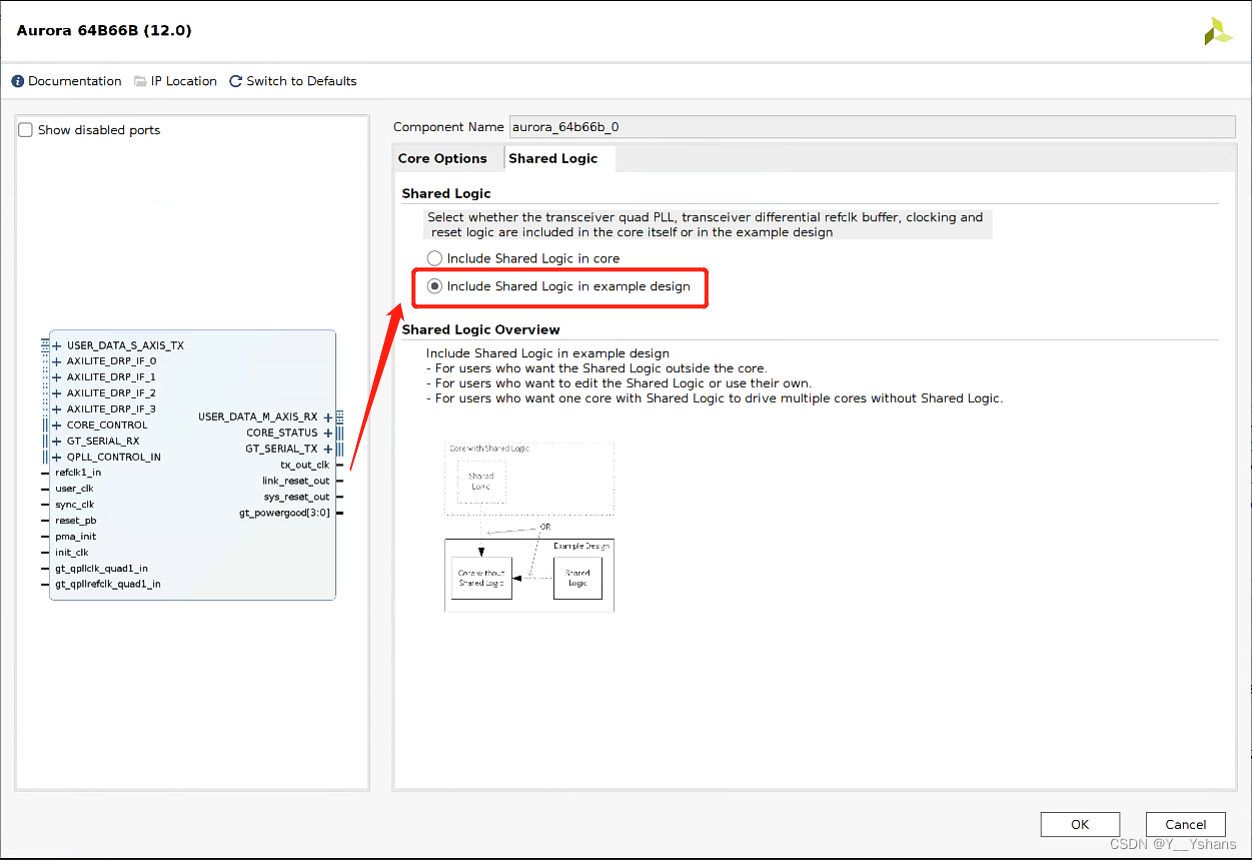

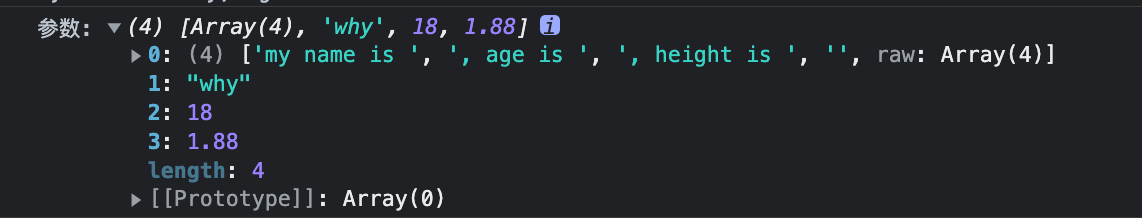

2. Aurora IP

这个选项表示把整个GT全部剥离出来,我在实际中是勾选了这个选项的。现在想想,没有这个必要,其实只需要将qpll的时钟剥离出来就行了,并不需要将整个GT剥离出来。不过如果未来有可能需要对GT进行一些更改的话,那还是建议将GT整个剥离出来。

同时Lanes的数量也是需要注意的,按照使用场景里面的要求,有四个sedes需要用到Aurora,所以Lanes这里选择4。

做GT或者QPLL的剥离,主要是为了让几个IP能够共享一对GT差分时钟。

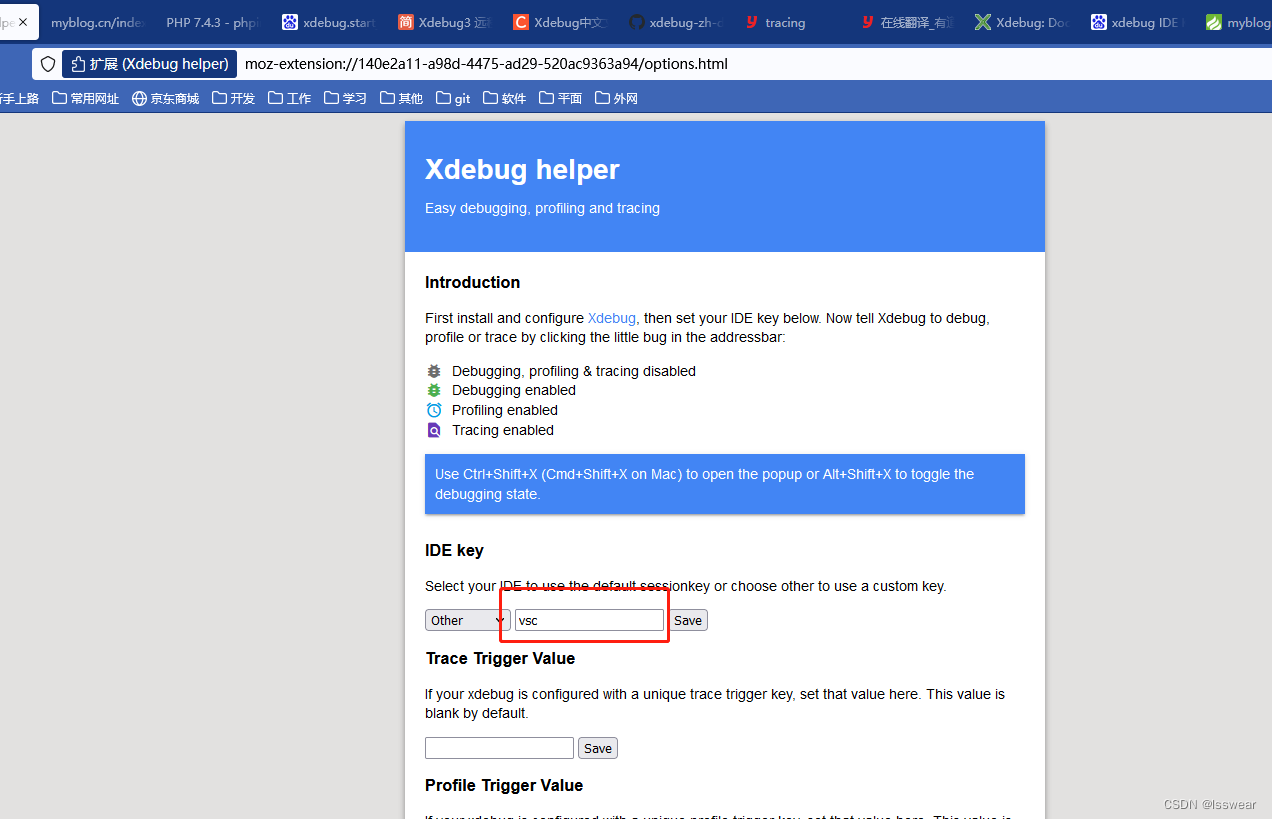

3. Ethernet IP

同理,Ethernet IP也是可以将GT或QPLL剥离出来的。

根据使用场景,有两个sfp口、两个serdes口都需要用到Ethernet ip。实际实现,我用两个以太网ip,每一个ip的lanes设置成2。GT selection设置成X0Y1,Lane-0X需要设置成X0Y5、X0Y6、X0Y7、X0Y8。

4. 错误方法演示

上面IP设置完成之后,需要将gt时钟连上三个ip。

我在实际中遇到的困难如下:

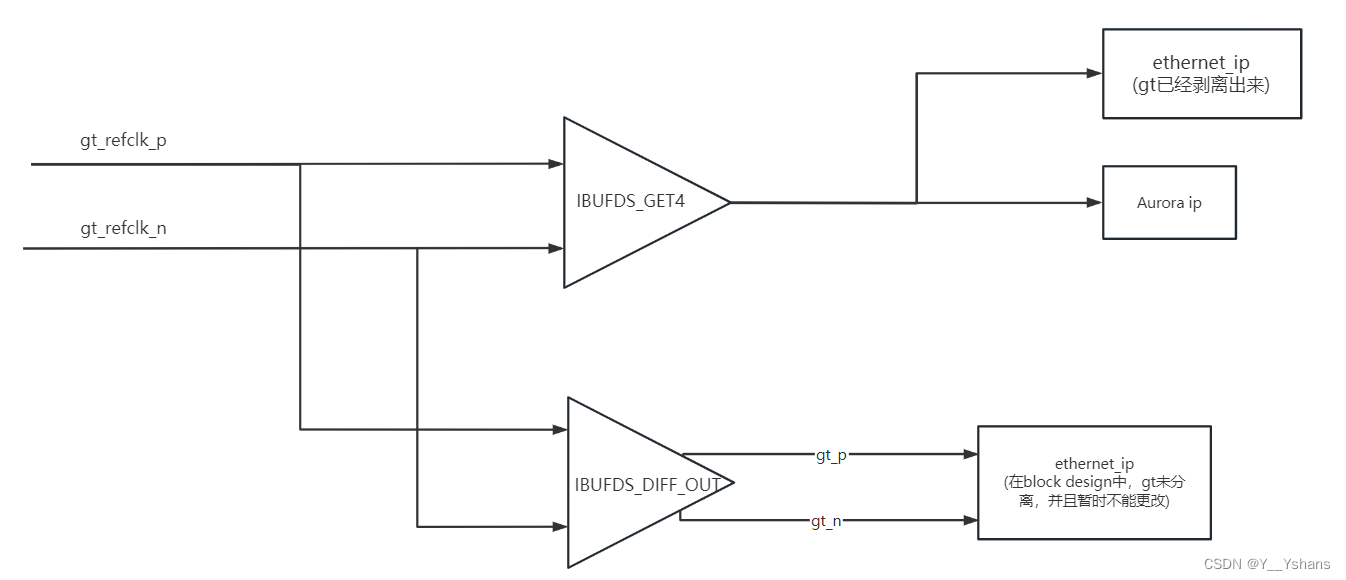

现在需要将三个ip共用一对GT时钟,一个Ethernet IP,一个Ethernet IP(这个IP在block design中),一个aurora IP。现在还有一个以太网ip存在于blockdesign中,这个ip的gt和core在设置中并没有分离,并且我们暂时没有办法改动这部分。所以aurora需要gt时钟,在block design中的以太网同样需要gt时钟,现在只有一对gt时钟。在不改动block design里的Ethernet ip的情况下,有什么好的办法可以让三个IP共同使用一对gt时钟。

我尝试过两种方式连接:

第一种连接方式如下:

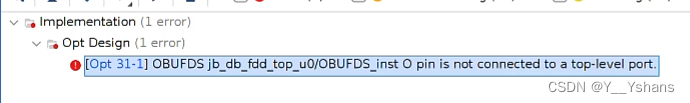

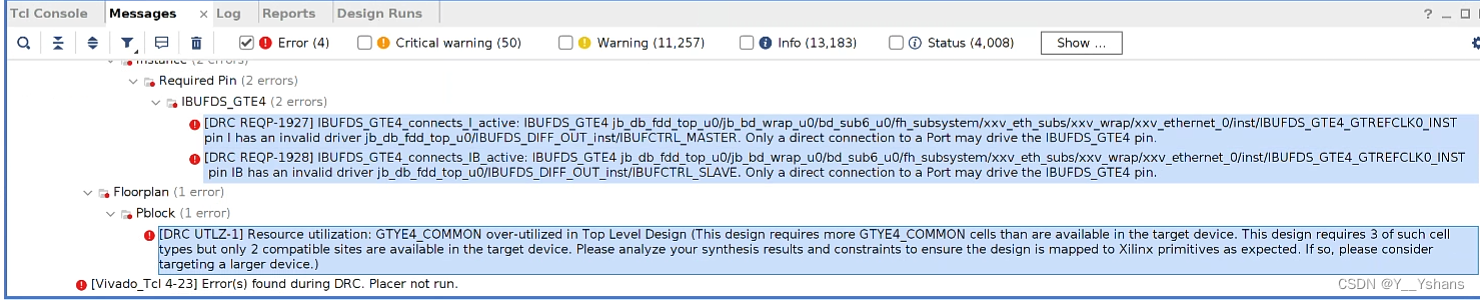

会有如下报错:

原因:OBUFDS的出口一定是要FPGA的,不能再连接其它模块了

第二种连接方式如下:

会有如下报错:

原因:IBUFDS_DIFF_OUT是HPIO专用的原语,不能和GT特有的IBUFDS_GTE连接的

总结

这一篇记录一下当时的一些错误解决方案。下一篇会讲述正确的解决方案以及在实际实现以及在实现过程中遇到的其它的问题。

参考文章:

支持关键字搜索

![[Vulnhub] DC-6](https://img-blog.csdnimg.cn/3f4bd925960e4cde9ab0af95b3b94f58.png)