概述

SPD1179 是旋智针对汽车应用推出的一颗高度集成的片上系统(SOC) 微控制器,内置 32

位高性能 ARMCortex-M4F 内核,最高 100MHz 的软件可编程时钟频率, 32KB SRAM, 128KB 嵌入式 FLASH, 1KB 基于 12KB FLASH 软件模拟的 EEPROM,丰富的增强型 I/O 和外设资源。此外还提供了 13 位 ADC, 1 路差分和 1 路单端可编程增益运放, 4 个增强型 PWM 模块, 3 个通用32 位定时器以及 2 个 UART(硬件支持 LIN) 、 2 个 SPI、 1 个 I2C 和 1 个 CAN 等通信接口。

SPD1179 采用 48 脚或 56 脚的可润湿侧翼 QFN 封装, 支持 5.5V~40V 单电源供电, 内部集

成电源管理模块, 支持睡眠模式和停止模式以降低功耗, 集成了级联式电荷泵和电流型三相桥

预驱,也集成了 LIN 收发器,所支持的工作结温为-40 ~ +150 ℃。 它能驱动有刷、无刷电机,

有集成度高、可靠性高、器件成本低等优点。

SPD1179 是汽车电子领域电机控制应用的理想平台,已被广泛应用于车窗、 天窗控制、 座

椅、 电滑门、 雨刮、 后视镜、 尾门、 激光雷达、 油泵、 水泵、 热管理、 空调压缩机、 鼓风机、电子风扇、 风门等。 这份文档集中讨论 SPD1179 在电路设计中经常遇到的问题,并且推荐一些实用电路;并对电路做了详细的分析。

SPD1179 应用推荐电路--内部驱动

电源电路

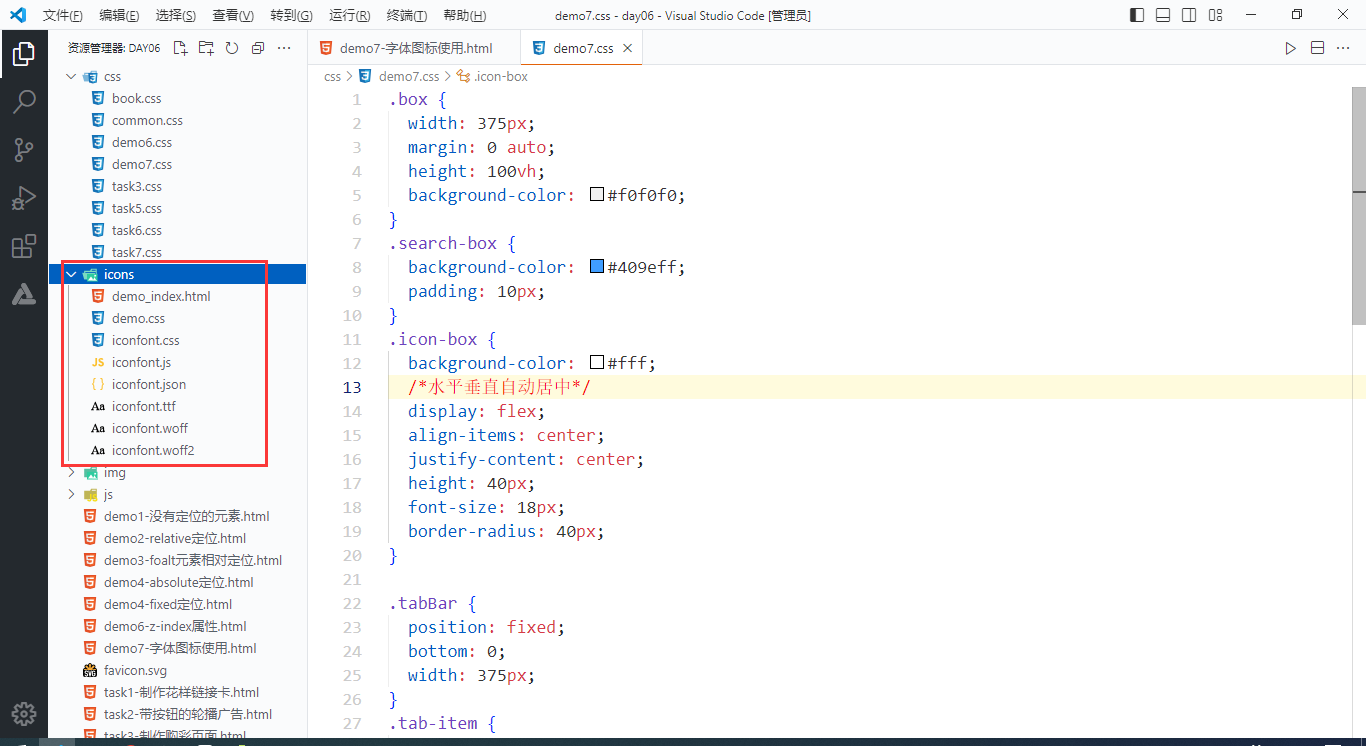

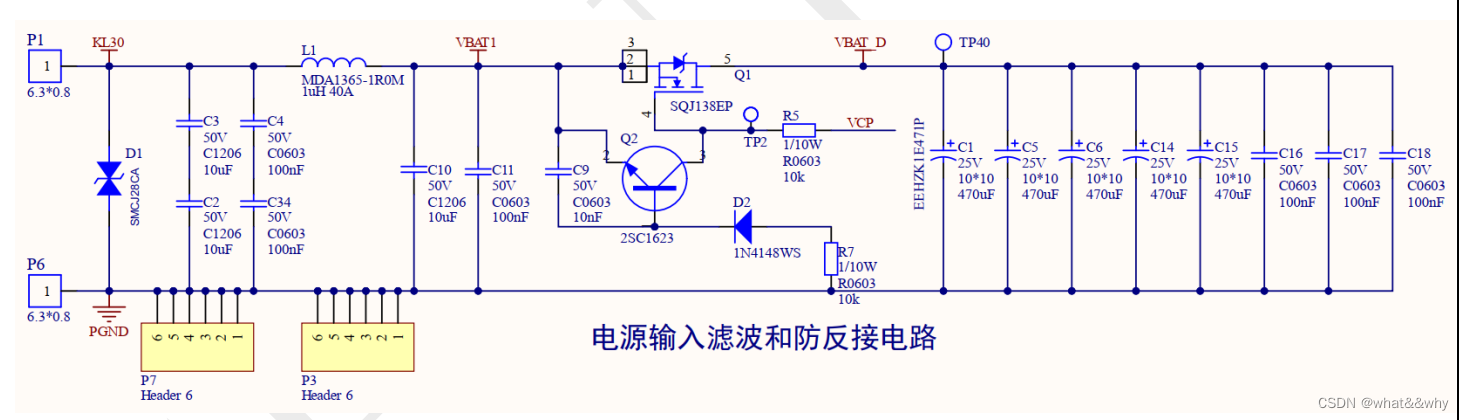

SPD1179 电源输入滤波和高边防反接电路

如图 所示为 SPD1179 推荐的电源端口输入滤波电路和高边防反接电路,利用输入功率电感在电源线入口处做一组 CLC 滤波,将滤波器放在靠近端口能够最大程度的将电源线上输入 PCB 板的噪声和从 PCB 板输出到电源线的噪声进行滤波。

| 注意: | KL30 输入端口的电容最好用两个电容串联,因为电源线上可能会有一些高的瞬态 电压尖峰,在输入端口可能会形成高电压,以免产生电容过压击穿的风险。 |

VBAT1 通过一个独立的防反接二极管供给芯片的 VBAT 供电。VBAT1 后面接主功率防反接 NOMS, VBAT_D 是三相桥的母线电压,放置了大容量电解电容, 提供电机运行三相电流。 防反接的 NMOS 的 G 极直接利用 VCP 的电压串联 10k 电阻做驱动。防反接 NOMS 的 GS 之间增加了一个 NPN 三极管 Q2,这个三极管在输入电源输出反接的时候(GND 接 12V, KL30 接 0V), R4 到 D2 再到 Q2 BE 就会形成 NPN 的 IB 导通电流, 此时 Q2就会导通, 就会将高边防反 NOMS 的 GS 电压会被钳位在 0.3V 左右,确保防反 NOMS 可靠关

断。电源输入正常的时候, NPN 三极管 Q2 截止,对高边防反接电路无影响。

过压保护

SPD1179 禁止在 28V 以上的电压下驱动三相桥,输出大功率。 建议的系统工作电压范围为

5.5V-16V, 实际系统的软件过压保护点建议可设置在 16.2V-24V,母线电压的软件检测一般都有

滞后性, 实际最终停止运行时的母线电压会高于软件设置的母线电压, 所以建议设置一个允许

条件下的最低的过电压保护值。硬件上可以实施的系统母线过压保护策略为:

可以在母线电压(VBAT_D) 上增加一个电阻分压电路,输入到芯片的一个 ADC 端口,然

后通过芯片内部的比较器实现精确快速的母线过压保护功能,保护响应时间可以小于 1us。需

要注意的是这个电阻分压电路始终连接在母线上, 需要增加一个高边开关控制,在系统进入睡

眠模式后切断此分压电路,降低系统的静态功耗。

软件需要配置如下两种母线过压保护策略:

1、芯片内部集成了 VBAT 电压的过欠压保护(BOD)功能,需要在软件中使能,并配置合

理的过欠压阈值。建议过压阈值设置在 16.2V-24V,过压之后停止三相桥输出。

2、三相桥母线电压 VBAT_D 通过一个 RC 滤波器连接到了芯片的 VBATM 端口, VBATM 端

口内部集成了分压电路,可以通过 ADC 直接检测此电压,也就是测量了 VBAT_D 母线电压的大

小。建议软件在 PWM 中断周期内读取 VBAT_D 母线电压的大小,并设置过压阈值在 16.2V-24V,过压之后停止三相桥输出,这个软件过压保护最快的响应时间是一个 PWM 周期。请参考软件支持包(SDK)中的 PWM demo 程序,在 PWM 中断里轮询检查 VBATM 电压实现母线过压保

护功能。

| 注意: | 在系统运行的时候, 首先需要通过软件配置 VBAT 过欠压保护功能。然后可以在 PWM 周期内查询 VBATM 的电压,进行母线电压过欠压保护。最后还可以通过在母 线上增加一个带高边开关的电阻分压电路接到芯片的 ADC 口,进行内部比较器过 欠压保护功能,电路请参考最新的 DEMO 原理图。 |

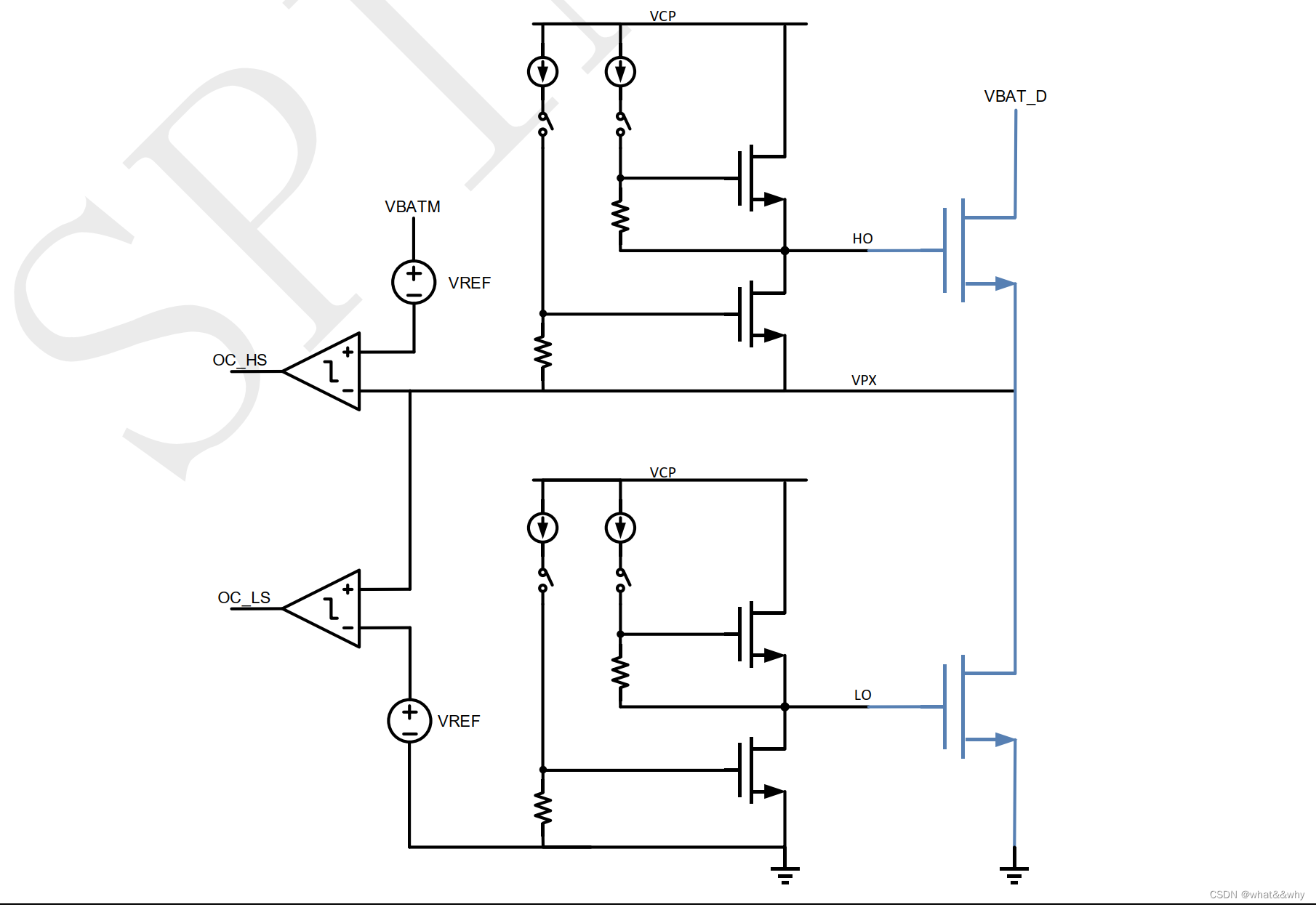

上桥的 D 极电压检测点是芯片 VBATM 引脚, S 极电压检测点是每相对应的 VPX 引脚。下

桥的 D 极电压检测点是芯片对应的 VPX 引脚, S 极电压检测点是芯片的 GND。

可配置的过压阈值为 0.15V-2.4V,共 16 档,每个档位电压增加 0.15V。有两种内部可以配

置的滤波时间, t_blank 和 t_filter 滤波时间, t_blank 的含义是指在三相桥任何 MOSFET 处于开

关状态的时候,这个时候会有一些开关噪声产生,容易引起 Vds 误触发,设置 t_blank 时间就

会在 MOSFET 动作的时候对 Vds 检测进行一段时间的屏蔽。 t_filter 滤波时间就是当检测到 Vds

故障触发之后,持续检测到 t_filter 时间的 Vds 过压信号之后,就会输出真正的 Vds 故障信号。

t_blank 和 t_filter 滤波时间均有 350ns, 750ns, 1550ns 和 3150ns 四个档位选择。更详细的保

护功能描述请参考《RC-034-2308001_SPD1179_技术参考手册》。

| 注意: | 下桥 MOSFET Vds 保护由于是比较 VPX 和芯片 GND 之间的电压,这就会包含采样 电阻和功率走线的电压,所以下桥 MOSFET Vds 保护误差会较大,一般情况下会禁 用下桥 Vds 保护功能,下桥短路保护可以使用采样电阻比较器过流保护 |

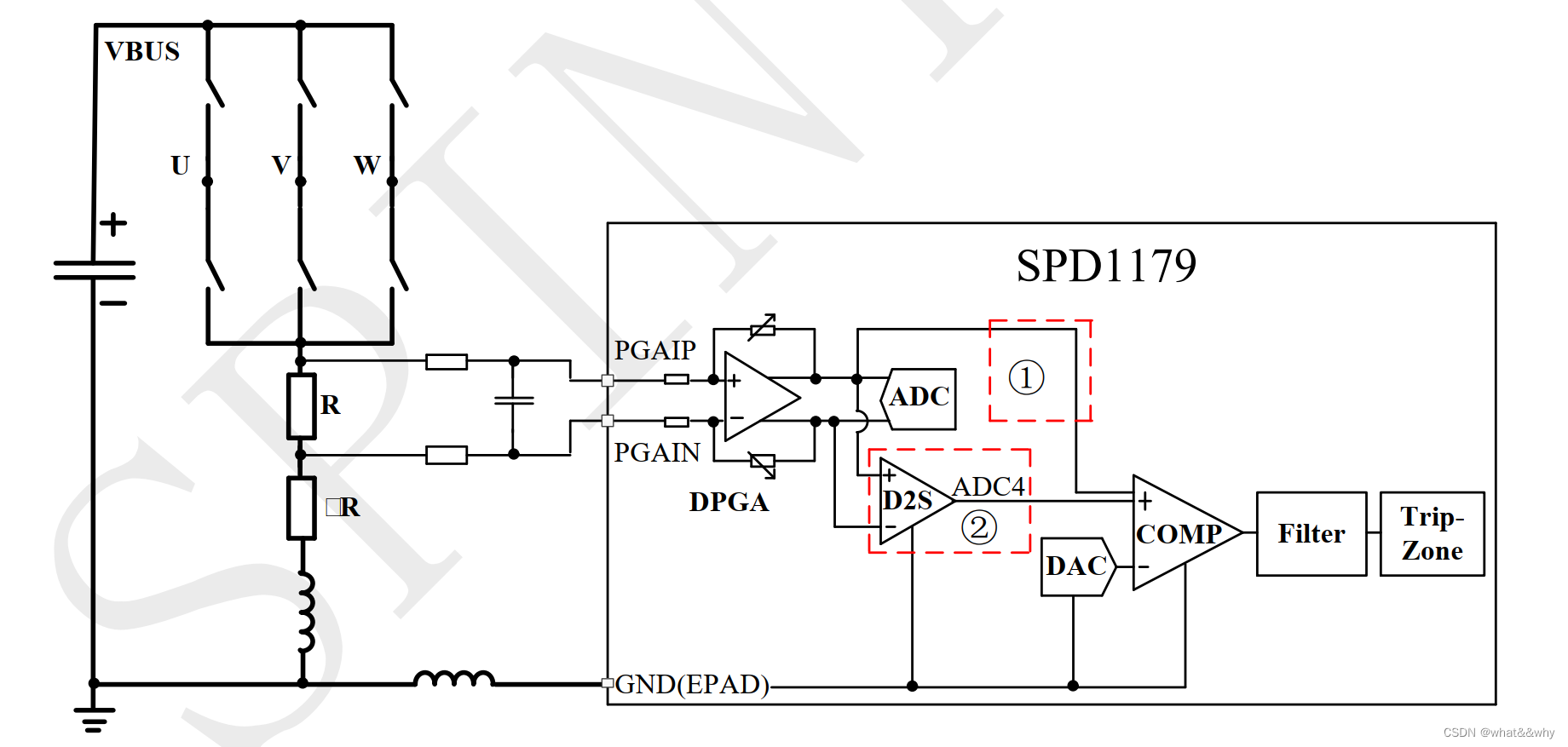

采样电阻硬件比较器过流保护

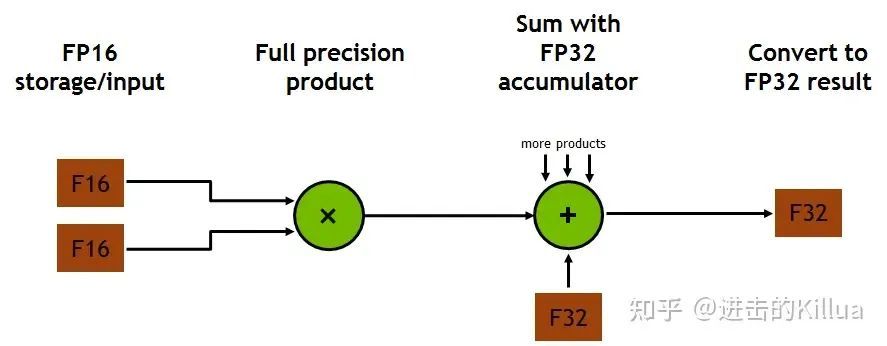

SPD1179 差分电流采样放大器(DPGA)可以在芯片内部利用 D2S 模块、

DAC 模块和比较器模块配置采样电阻短路过流保护功能,通过可配置的比较器滤波时间,可以

在 1us 以内响应采样电阻过流事件, 进而可以切断三相桥输出,保护功率电路不受损坏。

内部比较器过流保护有两种配置方法。

1. 将 PGAIP 经过单端放大之后的输出信号配置到比较器的正端, 因为取的是采样电阻正

极电压,是一个单端信号, 就包含了采样电阻负极产生的共模电压,就会使过流阈值

产生偏差。在采样电阻值比较大的场合,如 5 毫欧,那么采样电阻负极产生的共模电

压的影响较小,保护阈值的偏差就会较小。但是在采样电阻为 0.5 毫欧甚至更小的时

候,采样电阻负极产生的共模电压信号就会严重影响保护阈值的设置,这时候就需要

设置更大的保护点或者更长的滤波时间,才能得到想要的过流保护点。

2. 利用 SPD1179 芯片内部集成的 D2S 缓冲器,将 DPGA 的差分输出电压利用 D2S 缓冲器

做减法之后,得到真实的采样电阻两端的电压信号,然后送到比较器的正端,进行过

流比较, D2S 缓冲器的输出就消除了采样电阻下端地和芯片地之间共模电压引起的误

差, 就会得到更精准的过流保护点。

详细的 PGAIP 单端输出结果和 D2S 缓冲器输出 电压结 果 公式请 参 考《 RC-034-

2308001_SPD1179_技术参考手册》

| 注意: | 使能 D2S 缓冲器,然后将 ADC4 配置到比较器上之后, 就会占用 ADC4 引脚,请确 认 ADC4 引脚悬空,不能在用作其他功能。 |

除了上述 1 和 2 两种配置方法中描述的共模电压误差会对比较器过流阈值设置产生影响。

采样电阻由于焊接之后的电阻值偏差、 内部 VDD3/2 基准电压偏差、 PGA 放大误差和比较器失

调电压、 DAC 输出电压的偏差都会影响过流保护点的设置,这些偏差可以统称为静态偏差,静

态偏差可以在芯片上电初始化的时候做一个零位校准,因为此时采样电阻上的电流为零,将比

较器过流功能配置好之后,通过调整 DAC 的输出结果,不断的逼近(通过寄存器检查比较器输

出结果) 此时的比较器正端电压值(零电流值),软件可采用二分法去逼近,当得到和比较器

正端一致的 DAC 值的时候,就把这个 DAC 的值当做基准电压,在这个基准电压基础上去设置

过流点,将会增加保护点的设置精确度。

为了提高采样电阻过流比较的准确度,在 PCB 布局的时候需要注意的就是最好将母线电

容的地、采样电阻的地和芯片的地一点共地在一起。

VDD5EXT 的打开方法

VDD5EXT 的作用是为外部传感器电路提供电源,由高压模块中的 DVDD5EXT LDO 产生,该

功能默认关闭。若用户需要使用 VDD5EXT 电源, 则需要在程序中进行如下操作:

1、 开启高压模块;

2、 写使能高压模块中的控制寄存器;

3、 使能 DVDD5EXT LDO。

参考代码如下:

| Example Code |

| /* HV Init */ HV_Init(&u16PREDRIID); /* HV parameter write enable */ EPWR_WriteRegister(HV_REG_CTLKEY, KEY_USER_REG); /* Enable VDD5EXT */ EPWR_WriteRegisterField(HV_REG_PMUCTL, PMUCTL_VDD5EXTEN_Msk, PMUCTL_VDD5EXTEN_ENABLE); |

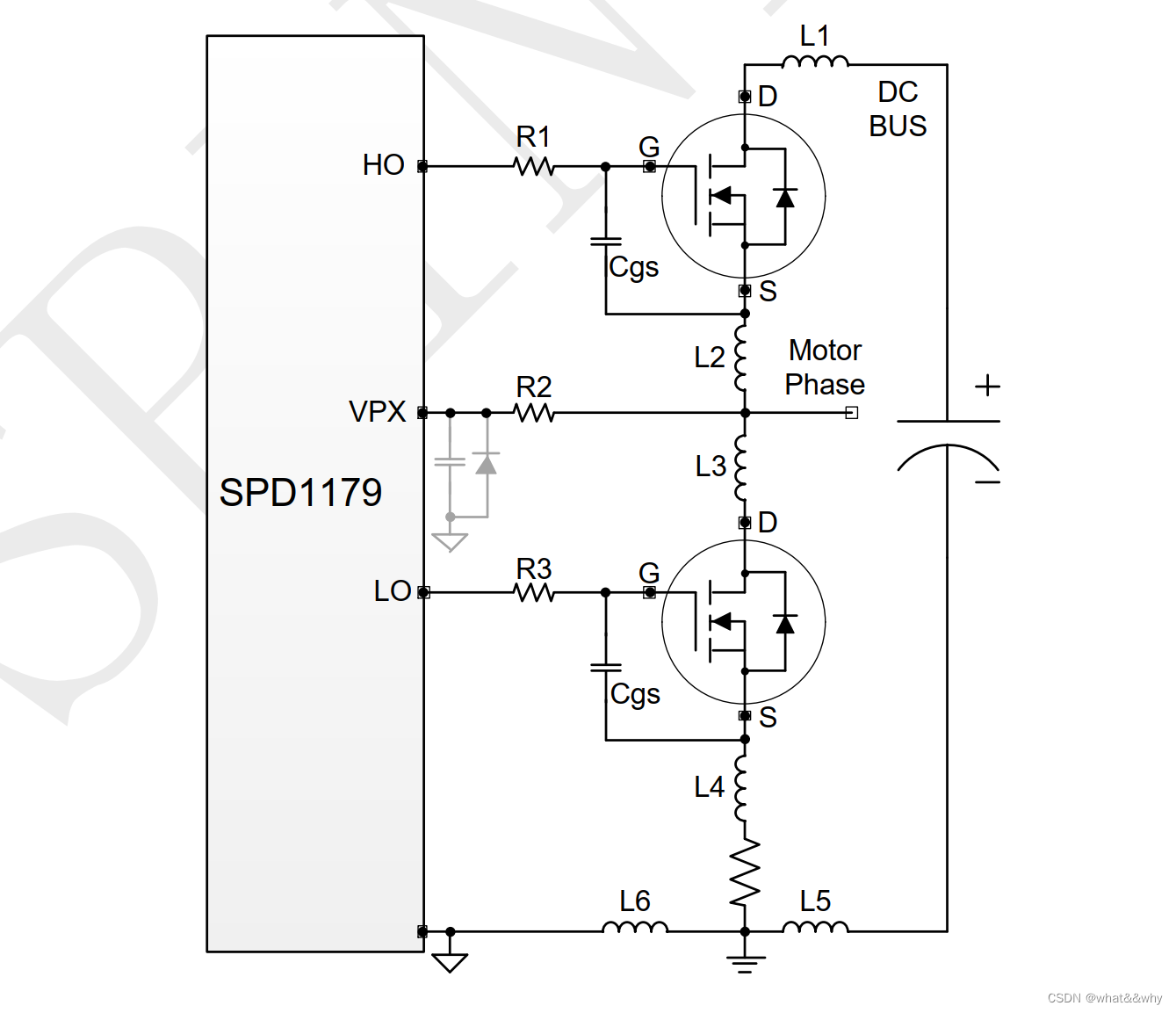

预驱芯片引脚承受负压的原理与规避措施

三相桥应用中的寄生电感效应分布示意图, 正是由于这些寄生电感的存在,当 MOSFET 开关高速切换的过程中,会在这些寄生电感上产生高的 di/dt,高的 di/dt会在这些寄生电感上形成高的瞬态电压尖峰, 这些瞬态电压尖峰斜率高达 1-10kV/us,甚至更高,脉冲电压幅值高达±1-20V,持续时间会达到 100ns 级别,

MOSFET 的驱动电压波形,其次瞬态尖峰电压(共模电压)传递到预驱芯片的引脚端,如果超

过了芯片规定的范围值就会影响驱动芯片的功能甚至对芯片内部器件造成损坏。 这在大功率应

用,或者由于结构限制 PCB 功率部分走线很长或者回路较大,功率回路寄生电感较大的应用需

要特别注意。

如下图所示,寄生电感 L1 是由上桥 MOSFET D 极内部寄生电感和上桥 MOSFET D 极到母线

电容正极这一段 PCB 功率走线寄生电感组成的。 寄生电感 L2 是由于上桥 MOSFET S 极内部寄

生电感和上桥 MOSFET S 极到电机连接端子 PCB 走线寄生电感组成的。 同理寄生电感 L3 是由

下桥 MOSFET D 极内部寄生电感和下桥 D 极到电机连接端子的 PCB 走线所组成的。寄生电感

L4是由下桥MOSFET S极内部寄生电感和下桥MOSFET S极到采样电阻上端的PCB走线所组成。

寄生电感 L5 是采样电阻下端到母线电容负极的 PCB 功率走线的寄生电感。

下桥 MOSFET S 极由于寄生电感在高 di/dt 的时候形成的震荡负压会通过下桥 GS 之间的电

容传递到芯片的下桥驱动输出级 LO 引脚,如果此负压太大,将会损坏芯片的 LO 引脚。所以推

荐在 LO 输出增加驱动电阻 R3,可以降低芯片 LO 引脚承受的瞬态负压, R3 推荐值范围是 10R-

51R。

电机连接端子处和上桥 MOSFET S 极由于寄生电感在高的 di/dt 的时候形成的震荡负压会

传递到芯片的 HO 和 VPX 引脚, 如果有过高的负压,那么可以在 HO 和 VPX 的输出增加驱动电

阻进行抑制, R1 推荐值范围是 10R-51R, R2 可以根据测试情况放置 10R 左右。 也可以在 VPX

靠近芯片端增加小容量稳压电容(如 470pF) 和对芯片地的开关二极管进行负压钳位。

寄生电感产生的震荡电压也会影响 MOSFET 的 GS 开关波形,导致 MOSFET 开关过程异常,

这需要在实际产品中进行测试确认。

降低寄生电感的最有效的方法就是在 PCB 设计的时候尽量降低 MOSFET S 极和相中点的

PCB 功率走线的长度。 同时降低功率 MOSFET 的开关速度,降低回路中的 di/dt。

其他电机控制电路---外部驱动

控制电路的参数选择

推荐电源输入滤波电路

1)15v降压电路

开发板需要三个电压等级,为15v,5v,3.3v。因为供电电压默认是24v,所以需要对其做降压处理。

第一个是24v降压到15v的电路图。15v的电压等级主要用在驱动模块。

这里使用了2个供电接口。这边选择一个进行供电即可。

C5C6C7是对母线电流进行滤波的三个电容。

D1是防止反流的二极管,电流只能通过从左向右流向开发板上。如果接反了可以对开发板进行保护。D1的型号是SS310,10表示的是100v耐压,3表示耐流是3A。

在这里使用了的开关电源芯片进行降压。通过查阅数据手册,这个降压芯片是1A 150KHz 80v的降压芯片。它是可以调节输出电压的芯片,它可以通过R9和R11两个电阻分压来进行输出电压的调节。

电压的输出与L1和D2关系比较大。D2是反馈的二极管,一般使用的是肖特基二极管。L1是输出的滤波电感。需要注意的是如果这个电感选择太大,可能会降低这个芯片的工作效率;如果选择太小,则电压输出的纹波会比较大,不利于后面的控制。

2)5v降压电路

这里也是选用,这是一个固定的降压芯片,是不可调的。也就是你输入之后,输出就是直接就是5v。L2和D3的作用和15v降压电路是一样的。

3)3.3v降压电路

这里使用的是3.3v的降压芯片。这是比较常用的。这是一个线性电源芯片,虽然效率不如前面两个开关电源芯片高,但是线性电源输出的电流纹波是比较小的。3.3对mcu进行供电。

二.信号采集模块

1)编码器采样

这个电路是5v的供电,R60R63R65是进行限流的操作,C45C46C47是对输出的信号进行简要的滤波。也就是一个简单的RC滤波电路。

2)霍尔采样

也是5v的供电电压。但是霍尔信号的输出值是1.几伏,不利于芯片的采集和对信号的处理,所以这里还使用了3.3v对输出的信号进行上拉,使其输出的是3.3v矩形波的信号。右边就是简单的RC滤波电路。

过零点和三相电压采样

主要用于采集过零点反电动势的电压信号。因为无感方波的控制,过零点信号要比霍尔信号要超前30度左右。因为超前所以在处理无感方波的时候需要对其进行一个延迟的处理。延迟到霍尔信号和过零点信号是一样的。

三相电压uvw由逆变模块过来,由于输出的电压比较高,所以需要对其进行分压处理。R68R71R74是对中性点进行模拟。

分压之后就能输出三个相电压UVW。

我们可以通过下面的公式来进行计算板子的耐压值。所以板子支持电机输入的最大电压是88.55v,而板子支持的最大供电电压是75v。

输出的三相电压和中性点电压到过零点采样电路进行比较。这边有一个比较器,R61和C43构成一个RC滤波电路,然后过零点信号输入到mcu里面。

电流采样

这部分电路是对逆变模块采样的电流进行放大的电路,选用的芯片时高带宽高速的放大芯片。

3.3v进来经过分压电路,分出了1.65v,然后进入了电压跟随器,输出的也是1.65v。这是因为mcu只能采样到正电压,负电压是识别不了的,也会损坏mcu。

因为输入进来的波形是正弦,电压有正有负,所以我们需要把波形进行升压,整体往上抬升1.65v。当我们抬到1.65v的时候,全部的电压都可以采样到了。

另一部分电路由于是正向差分放大的电路,可能会有共膜的干扰。所以中间有一个C3电容,就是为了滤除共模干扰。然后输出端接的是RC滤波。

我们可以通过下面的公式计算出放大的电流倍数。由于逆变模块流过的最大电流是10A,

逆变模块

这里是全桥的逆变电路,实例使用的mos,是540s,这个mos的耐压是100v,耐流是33A。下面的R49R50R51是输出电压的0.01欧1w的采样电阻。

我们可以通过下面功率计算公式来计算流过的电流。可以得出最大的电流是10A的电流。

驱动模块

六路的PWM波是芯片输出的,芯片输出的最大幅值就是3.3v,但是这个电压是不足以驱动逆变模块的N沟道的mos管的。所以需要一个驱动桥对电压进行升压处理,输出的信号就能对mos管的栅极进行驱动。

D4D7D10使用的也是肖特基二极管。它的耐压不高,但是速度特别快。

C19C21C30是10uF的自举电容。

这个驱动桥芯片选用。

右边输出部分还有一个反并联的肖特基二极管D5,因为mos也是有寄生电容,如果不放掉的话会影响mos管的开关速度,这边通过100欧来进行放电的话会比较慢,所以反并联一个二极管没有阻抗直接放掉了。可以提高mos的反应速度。

MCU

DAC在主板的编码器的下面,是两个小的铜环,示波器接这里可以检测到想看的波形。

晶振是给MCU提供基频的,

JTAG是下载端口,支持ST_LINK和J_link的。程序都是默认根据J_link进行匹配的。因为J_link的速度比较快,比较好用。

然后是10k的电位器,在板子中是蓝色的。

除此之外还有7针0.96的oled接口,

母线电压检测电路,最大支持的电压是88v

这里使用的是232串口,因为STM32的单片机默认支持的是232。

![正点原子[第二期]Linux之ARM(MX6U)裸机篇学习笔记-14-主频和时钟配置](https://img-blog.csdnimg.cn/direct/bf7a1beff5b24b219d6877d398a2cb0a.png)