前言:

本文是根据哔哩哔哩网站上“正点原子[第二期]Linux之ARM(MX6U)裸机篇”视频的学习笔记,在这里会记录下正点原子 I.MX6ULL 开发板的配套视频教程所作的实验和学习笔记内容。本文大量引用了正点原子教学视频和链接中的内容。

引用:

正点原子IMX6U仓库 (GuangzhouXingyi) - Gitee.com

《【正点原子】I.MX6U嵌入式Linux驱动开发指南V1.5.2.pdf》

正点原子资料下载中心 — 正点原子资料下载中心 1.0.0 文档

正文:

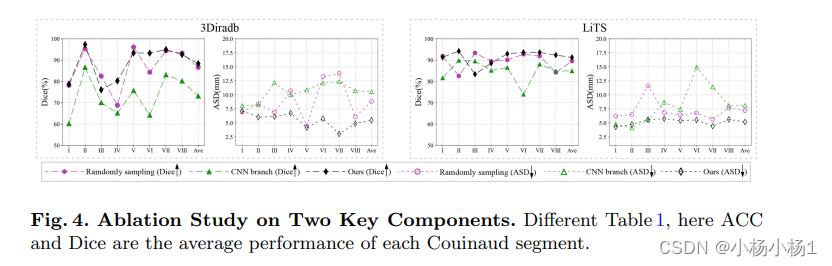

本文是 “正点原子[第二期]Linux之ARM(MX6U)裸机篇--第14.1, 14.2, 14.3 讲” 的读书笔记。第14讲主要是介绍I.MX6U处理器的主频和系统时钟配置。本节将参考正点原子的视频教程第14讲和配套的正点原子开发指南文档进行学习。

0. I.MX6U系统时钟总体介绍

在前几章的时延中我们都没有涉及到I.MX6U的时钟和主频的配置操作,全部使用默认的配置,默认配置I.MX6U上电启动芯片内部 boot ROM 会把处理器工作频率设置为 396MHz。但是 I.MX6U 系列标准的工作频率为 528MHz,有些型号甚至可以工作到696MHz。本章我们就学习I.MX6U的系统时钟,学习如何配置I.MX6U的系统时钟和其他的外设时钟,使其工作在 528MHz,其它的外设时钟都工作在NXP推荐的频率。

1. I.MX6U时钟系统详解

I.MX6U的系统主频为528MHz,有些型号伸着可以跑到696MHz,但是默认情况下内部 boot rom 会讲 I.MX6U 的主频设置为 396MHz,这个我们在 9.2 小节已经讲过了。我们在使用 I.MX6U 的时候肯定要发挥它的最大性能,那么主频肯定要设置到528MHz(其它型号可以设置的更高,比如696MHz),其它的外设时钟也要设置到NXP推荐的值。I.MX6U的系统时钟在I.MX6ULL/I.MX6UL 参考手册》的第 10 章“Chapter 10 Clock and Power Management”和第18 章“Chapter 18 Clock Controller Module (CCM)”这两章有详细的讲解。

1.1 系统时钟的来源

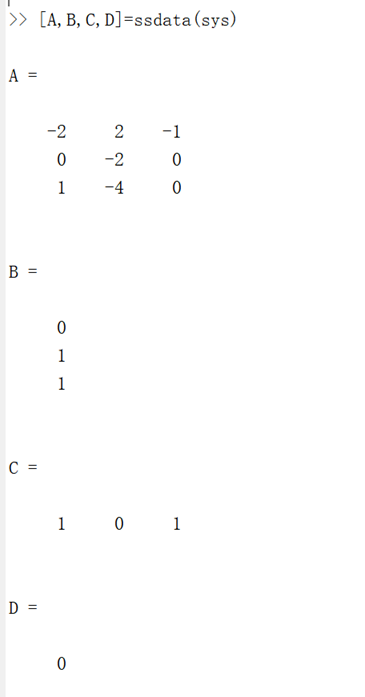

打开I.MX6U ALPHA/Mini 核心开发板原理图,开发板时钟如图 16.1.1.1 所示

从图 16.1.1.1 可以看出 I.MX6U ALPHA/Mini 开发板的系统时钟来源于两部分:32.768KHz和24MHz的晶振,其中 32.768KHz是I.MX6U的RTC时钟源,24MHz晶振是I.MX6U内核和其他外设的时钟源,也是我们重点要分析的。

1.2 7路PLL时钟源

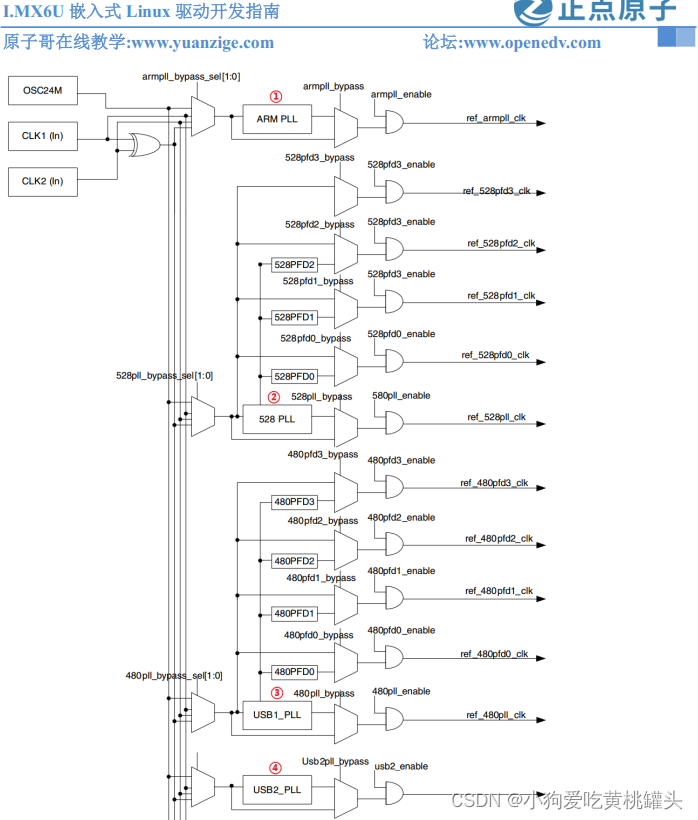

I.MX6U的外设有很多,不同的外设时钟源不同,NXP将这些外设的时钟源做了分组,一共有7组,这7组时钟源都是从 24MHz 晶振 PLL 而来的,因此也叫做7组PLL,这7组PLL结构图如 图 16.1.1.2 所示:

图 16.1.1.2 展示了7个PLL的关系,我们依次来看一下这7个PLL的都是什么做什么用的?

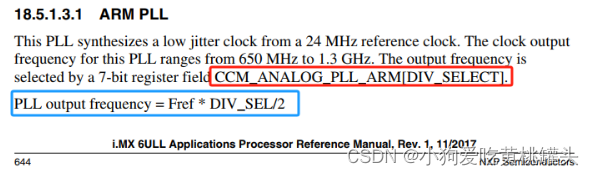

- 1. ARM PLL (PLL1) ,此路PLL是同ARM内核使用的,ARM内核时钟就是由此PLL生成的,此PLL通过编程的方式最高可倍频到1.3GHz。

- 2. 528_PLL(PLL2),此路PLL也叫做 System_PLL,此路PLL是固定的22倍频,不可编程修改。因此,此路PLL时钟=24MHz*22=528MHz,这也是为什么此PLL叫做 528_PLL 的原因。此PLL分出4路PFD(相位分数分频器),分别为 PLL2_PFD0~PLL2_PFD3,这4路PFD和528_PLL共同作为其它很多外设的根时钟源。通常528_PLL和这4路PFD是 I.MX6U 内部系统总线的时钟源,比如内部处理器逻辑单元,DDR接口,NAND/NOR接口等等。

- 3. USB1_PLL(PLL3),此路PLL主要用于USBPHY,此PLL也有四路PFD,为 PLL3_PFD0~PLL3_PFD3,USB1_PHY 是固定的20倍频,因此USB1_PLL=24MHz*20=480MHz。USB1_PLL虽然主要用于USB1PHY,但是和其他四路PFD同样也可以用作其他外设的时钟源。

- 4. USB2_PLL(PLL7),看名字就知道此路PLL是给 USB2PHY使用的。同样的,此路PLL固定位20倍频,因此也是480MHz。

- 5.ENET_PLL(PLL6),此路PLL固定位20+5/6倍频,因此 ENET_PLL=24MHz*(20+5/6)=500MHz。此路PLL用于生成网络所需的时钟,可以在此PLL的基础上生成25/50/100/125MHz网络时钟。

- 6. VIDEO_PLL(PLL5),此路PLL用于显示相关外设,比如LCD,此路PLL的倍频可以调整,PLL的输出范围在 650MHz~1300MHz。此路PLL在最终输出的时候还可以进行分频,可选1/2/4/8/16分频。

- 7. AUDIO_PLL(PLL4),此路PLL用于音频相关的外设,此路PLL的倍频可以调整,PLL的输出范围同样也是650MHz-1300MHz,此路PLL在最终输出的时候也可以进行分频,可选1/2/4分频。

1.3 时钟树简介

在上一小节讲解了7路PLL,I.MX6U的所有外设时钟源都是从这7路PLL和有些PLL的PFD而来的,这些外设舅舅如何选择PLL或者PFD的?这就要借助《IMX6ULL 参考手册》里的时钟树了,在“Chapter 18 Clock Controller Module (CCM)”的 18.3 小节给出了 I.MX6U详细的时钟树图,如图 16.1.3.1 所示:

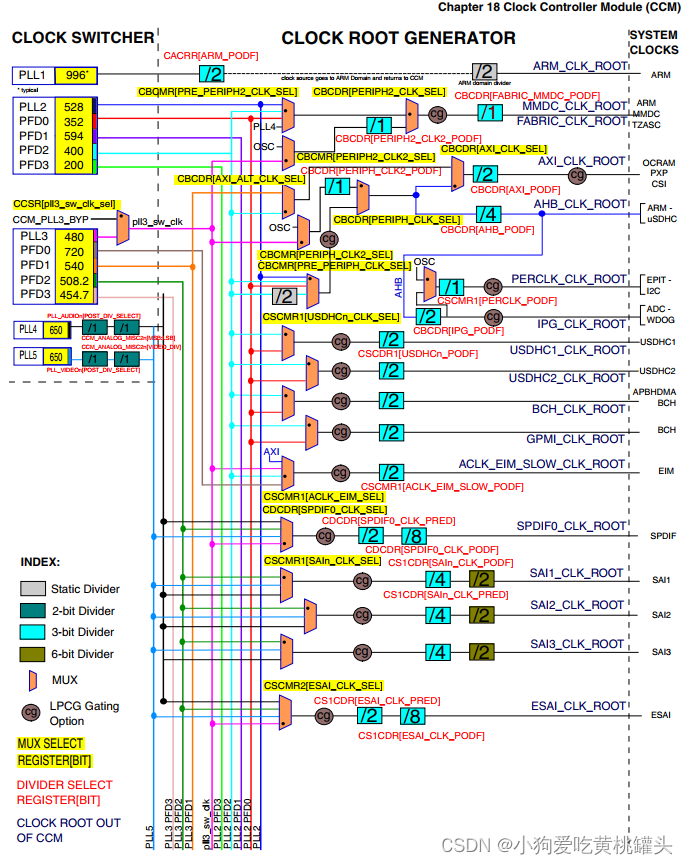

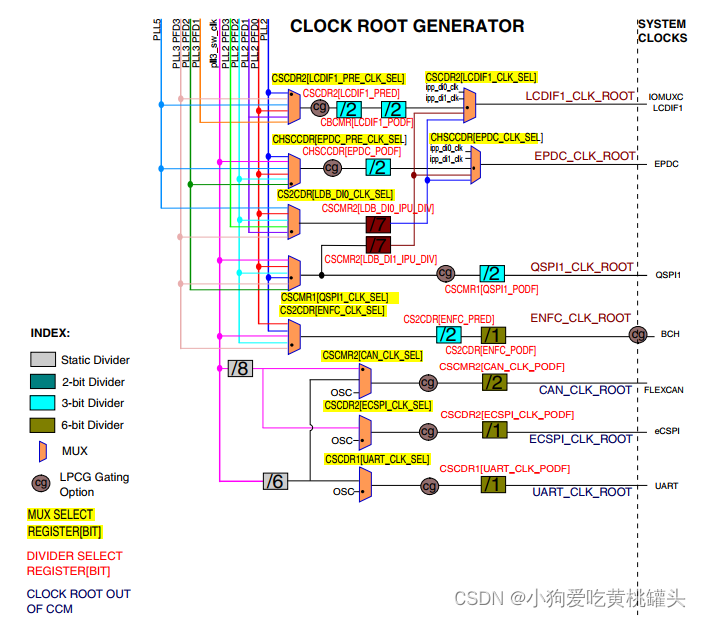

在图16.3.1中一共有三部分:CLOCK_SWITCHER,CLOCK ROOT GENERATOR 和 SYSTEM CLOCKS。其中左边的 CLOCK_SWITCHER 就是我们上一小节讲解的那7路PLL和8路PFD,右边的 SYSTEM CLOCK 就是芯片外设,中间的 CLOCK ROOT GENERATOR 是最复杂的,这一部分就像“月老”一样,给左边的 CLOCK_SWITCHER 和 右边的 SYSTEM CLOCKS 进行牵线搭桥。外设的时钟源有多路可以选择的,CLOCK ROOT GENERATOR 就扶着从7路PLL和8路PFD中选择合适的时钟源给外设使用。具体操作肯定是设置相应的寄存器,我们以EASI这个外设为例,EASI的时钟图如 16.1.3.2 所示:

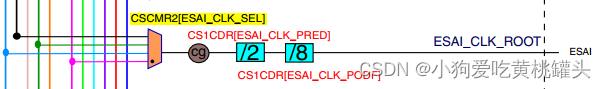

在图 16.1.3.2 中我们分为了3部分,这3部分如下:

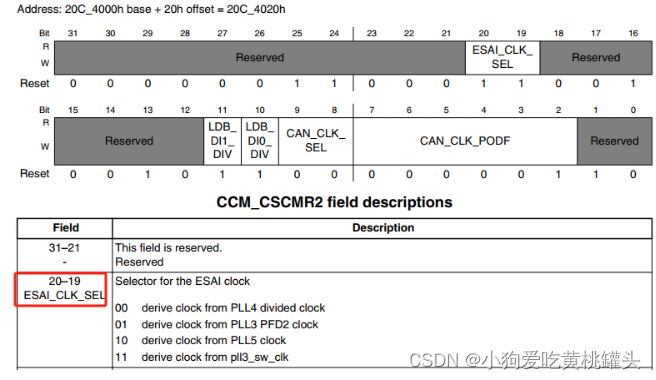

- 此部分是时钟选择源,ESAI有4个可选的时钟源:PLL5, PLL5, PLL3_PFD2 和 pll3_sw_clk。具体选择哪一路作为ESAI的时钟源是有寄存器 CCM->CSMR2 的 EASI_CLK_SEL 位来决定的,用户可以自由配置,配置如图 16.1.3.3 所示

- 此部分作为ESAI时钟的前级分频器,分频值由 CS1CDR的ESAI_CLK_PRED来确定,可以设置1~8分频,假如现在 PLL4=650MHz,我们选在PLL4作为ESAI时钟,前级分频器选择2分频,那么此时的时钟就是 650/2 = 325MHz

- 此部分又是一个分频器,对2中输入的时钟进一步分频,分频值由寄存器 CS1CDR 的 ESAI_CLK_PODF 来决定,可以设置1~8分频。假如我们设置为8分频的话,经过此分频器以后的时钟就是 325/8=40.625MHz。因此最终进入到 ESAI外设的时钟就是 40.625MHz。

上面我们以外设EASI为例讲解了如何根据图 16.1.3.1 来设置外设的时钟频率,其它的外设基本类似,大家可以自行分析一下其他的外设。关于外设时钟配置的内容全部都在《I.MX6ULL 参考手册》的第 18 章。

1.4 内核时钟设置

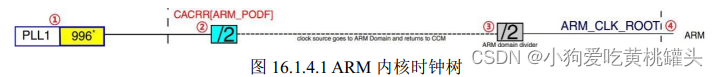

I.MX6U的系统故事中再前面几节已经分析的差不多了,现在就可以开始设置相应的时钟频率了。先从处理器主频开始,我们将 I.MX6U 的主频设置为 528MHz,根据根据图 16.1.3.2 的时钟树可以看到ARM 内核时钟如图 16.1.4.1 所示:

图 16.1.4.1 中各部分如下

- 内核时钟来源于PLL1,假设此时PLL1为960MHz。

- 通过寄存器 CCM_CACRR 的 ARM_PODF 位对PLL1进行分频,可选择1/2/4/8分频,假如我们选择了2分频,那么经过分频以后的时钟频率就是 996/2=498MHz。

- 大家不要被次数的2分频给骗了,此处没有进行2分频(我就被这个 2 分频骗了好久,主频一直配置不正确!)。

- 经过第2步的分频之后的498MHz就是ARM的内核时钟,也就是I.MX6U的主频。

经过上面的几步分析可知,假如我们要设置内核主频为528MHz,那么PLL1可以设置为 1056MHz,寄存器CCM_CACRR的 ARM_PODF 位设置为2。同理,如果要将主频设置为696Mhz,那么主频PLL1就可是设置696Mhz,CCM_CACRR的 ARM_PODF 位设置为1。

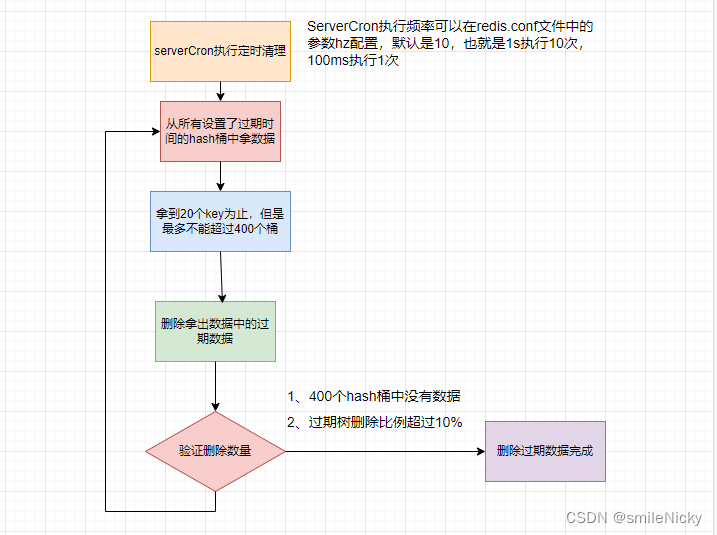

现在问题很清晰了

- 寄存器CCM_CACRR的 ARM_PODF 位很好设置

- PLL1的频率可以通过 CCM_ANALOG_PLL_ARMn 来设置。

接下来详细的看一下CCM_CACRR和CCM_ANALOG_PLL_ARMn这两个寄存器,CCM_CACRR如下图所示: