目录

- 1、前言

- 2、我这儿已有的 FPGA USB 通信方案

- 3、CY7C68013A芯片解读和硬件设计

- FX2 简介

- SlaveFIFO模式及其配置

- 4、工程详细设计方案

- 输入测试图片的处理

- PC上位机发送测试图片

- 图像接收与缓存

- 图像输出显示

- 5、vivado工程1--LCD输出显示

- 6、vivado工程1--LCD输出显示

- 7、上板调试验证

- 8、福利:工程代码的获取

1、前言

目前USB2.0的实现方案很多,但就简单好用的角度而言,Cypress公司的CY7C68013A应该是最佳方案,因为它内部集成了8051 CPU 并封装为FIFO接口,电路设计简单,操作时序简单,软件驱动简单,官方甚至提供了包括FPGA驱动在内的丰富的驱动源码和测试软件;

本设计用FPGA驱动Cypress公司的CY7C68013A芯片实现USB2.0 图片发送试验,使用SlaveFIFO模式通信,我们提供CY7C68013A的配置固件及其源码,一般固件源码不需要修改,直接通过官方工具下载即可,官方工具我们也一并提供,并放在资料包里了;基于 SlaveFIFO 接口的图片发送试验,能够实现 PC 通过 FX2 向 FPGA 图片,FPGA接收图片后将图片缓存至DDR3后读出送显示器显示,我们提供了2套vivado工程,一套是LCD显示屏显示接收的图片,另一套是HDMI显示屏显示接收的图片;代码编译通过后上板调试验证,可直接项目移植,适用于在校学生做毕业设计、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的USB2.0通信和图像传输领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式以及上板调试的演示视频放在了文章末尾,请耐心看到最后;

2、我这儿已有的 FPGA USB 通信方案

我这儿现有的FPGA基于 CY7C68013A 的 USB3.0通信方案,主要有数据回环测试,图片收发测试,视频收发测试,视频收发基于OV5640摄像头完成;感兴趣的可以去我的USB2.0通信专栏阅读,专栏地址如下:

点击直接前往专栏

此外,我这儿还有的FPGA基于FT601和FT602的USB3.0通信方案,主要有简单的测速方案、图像传输方案,图像传输方案包括简单的彩条传输采集、OV5640摄像头传输采集、HDMI视频采集,HDMI视频采集抓拍、USB3.0 UVC视频等等,所有工方案均包括FPGA工程和QT上位机源码;感兴趣的可以去我的FT601 USB3.0通信专栏阅读,专栏地址如下:

点击直接前往专栏

3、CY7C68013A芯片解读和硬件设计

FX2 简介

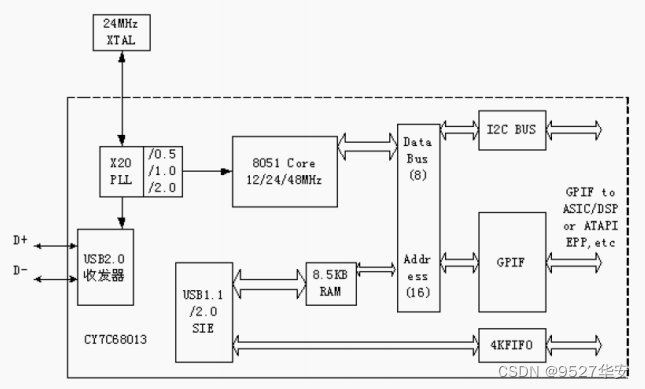

Cypress 公司的 EZ-USB FX2 是世界上第一款集成 USB2.0 的微处理器,它集成了USB2.0 收发器、SIE(串行接口引擎)、增强的 8051 微控制器和可编程的外围接口。FX2 这种独创性结构可使数据传输率达到480MBit/s。在FX2中,智能SIE可以硬件处理许多USB1.1和 USB2.0 协议,从而减少了开发时间和确保了 USB 的兼容性。该器件具有如下特性:

1:内嵌 480MBit/s 的收发器,锁相环 PLL,串行接口引擎 SIE——集成了整个 USB 2.0 协

议的物理层。

2:内嵌可工作在 48MHz 的增强型 8051,该 8051 控制器具有以下特征:

(1)具有 256Byte 的寄存器空间,两个串口,三个定时器,两个数据指针。

(2)四个机器周期(工作在 48MHz 下时为 83.3ns)即组成一个指令周期。

(3)特殊功能寄存器(包括 I/O 口控制寄存器)可高速访问。

(4)应用 USB 向量中断,具有极短的 ISR 响应时间。

(5) 只用作 USB 事务管理,控制,不参与数据传输,较好地解决了 USB 高速模式的

带宽问题。

3:“软配置”——USB 固件可由 USB 总线下载,片上不需集成 ROM。

4:拥有四个 FIFO 接口,可工作在内部或外部时钟下。端点和 FIFO 接口的应用使外部逻

辑和 USB 总线可高速连接。

5:一种单片 USB 2.0 外设解决方案,不需要外部的协议物理层,FX2 把所有的功能集成

在一个芯片上。

典型的 FX2 控制器,比如CY7C68013A的内部结构图如下:

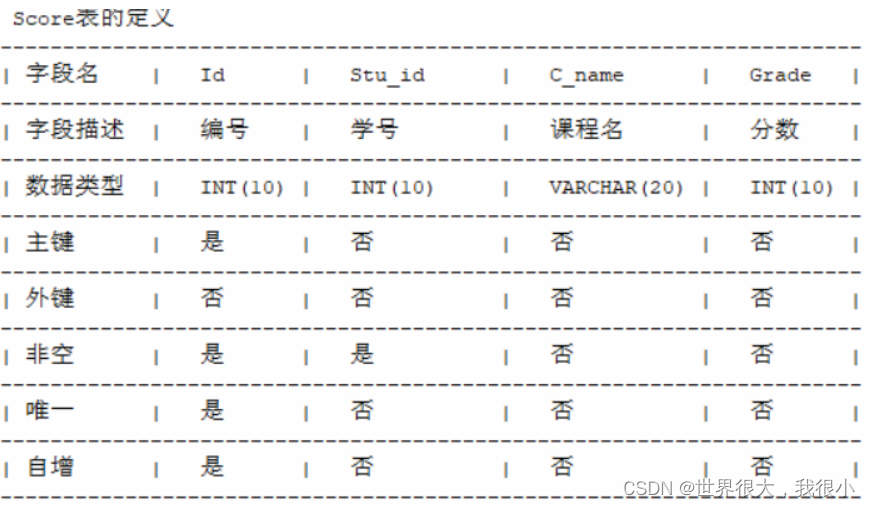

SlaveFIFO模式及其配置

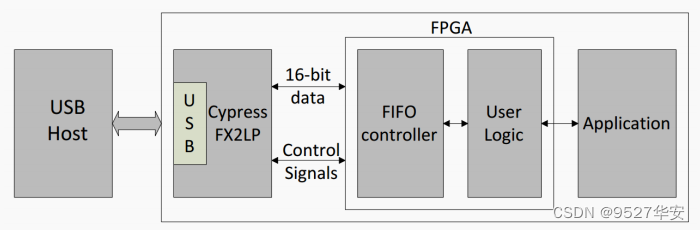

FX2-FPGA 接口为基于 FPGA 的应用执行高速度的 USB 连接事项,如数据采集、工业控制和监控以及图像处理提供了非常简单易用的接口。FX2 在SlaveFIFO模式下运行, FPGA 作为主设备使用。

SlaveFIFO:在该模式下,连接至 FX2 的外部系统能够生成读和写控制信号,因此,它能作为 FX2 的主设备使用。在基于 FPGA 的应用中,FX2 一般被配置为SlaveFIFO模式。下图为 FX2 使用从设备 FIFO 接口与外部 FPGA 连接时的系统框图。

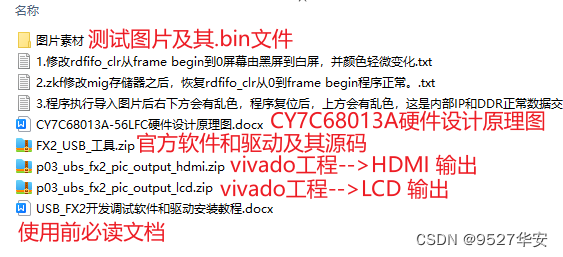

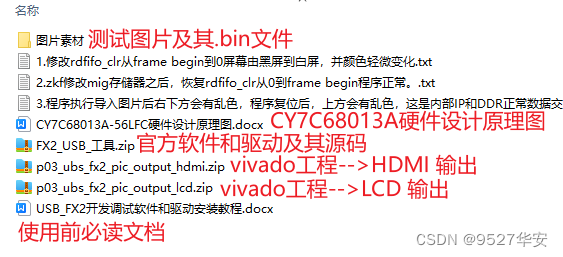

在这种方式下,FX2 内嵌的 8051 固件的功能只是配置 Slave FIFO 相关的寄存器以及控制 FX2 何时工作在 Slave FIFO 模式下。一旦 8051 固件将相关的寄存器配置完毕,且使自身工作在 Slave FIFO 模式下后,外部逻辑(如 FPGA)即可按照 Slave FIFO 的传输时序,高速与主机进行通讯,而在通讯过程中不需要 8051 固件的参与。SlaveFIFO模式的配置需要安装CY7C68013A官方提供的一整套工具下载相关固件完成,这一套东西我已打包,并专门写了一个工具安装、驱动安装、工具使用、固件下载的文档,也一并放在了资料包里,如下:

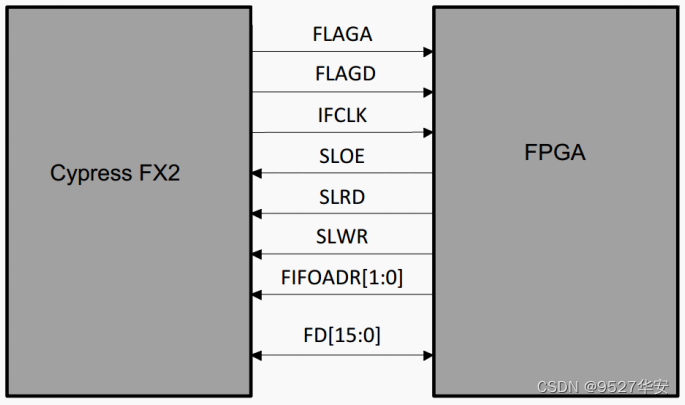

下图为 SlaveFIFO模式下 FX2 与 FPGA 连接示意图。

具体信号管脚说明如下。

对于 IFCLK 信号,属于一个方向可配置的信号,既可以由 FX2 输出,连接到外部器件如FPGA,也可以配置为输入,接收来自外部器件的时钟信号,在本例中,将 IFCLK 配置为输出,即由 FX2 输出给 FPGA,作为数据和控制信号的同步时钟。

4、工程详细设计方案

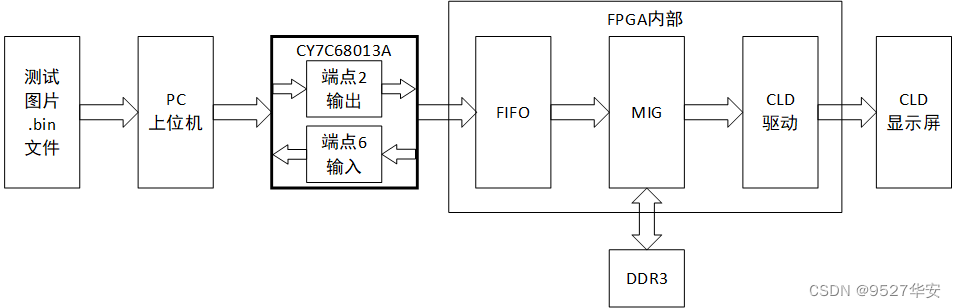

工程1:LCD 输出显示的详细设计方案如下:

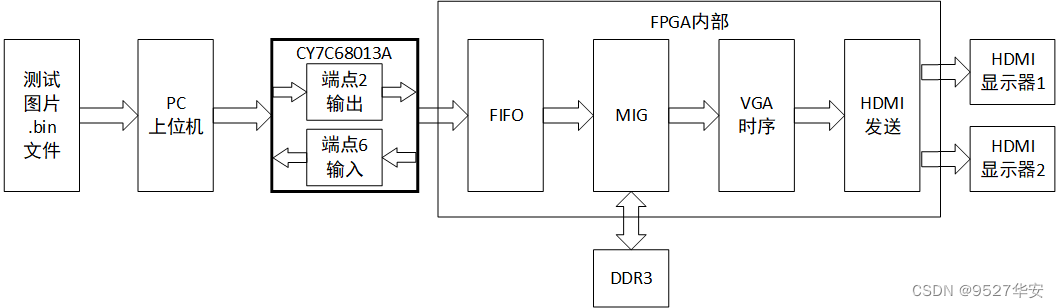

工程2:HDMI 输出显示的详细设计方案如下:

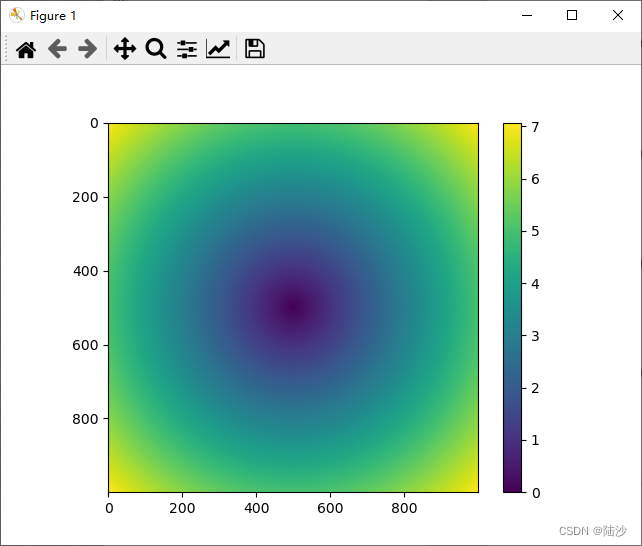

输入测试图片的处理

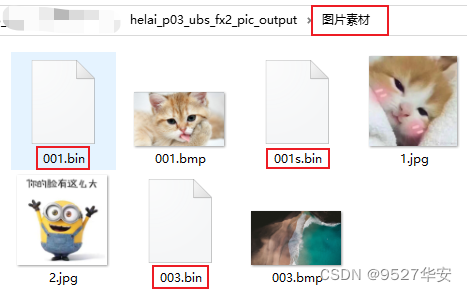

输入测试图片要求为.bin文件,你可以通过脚本或者工具将图片转为.bin文件,我提供的资料包里已经为你提供好了,如下:

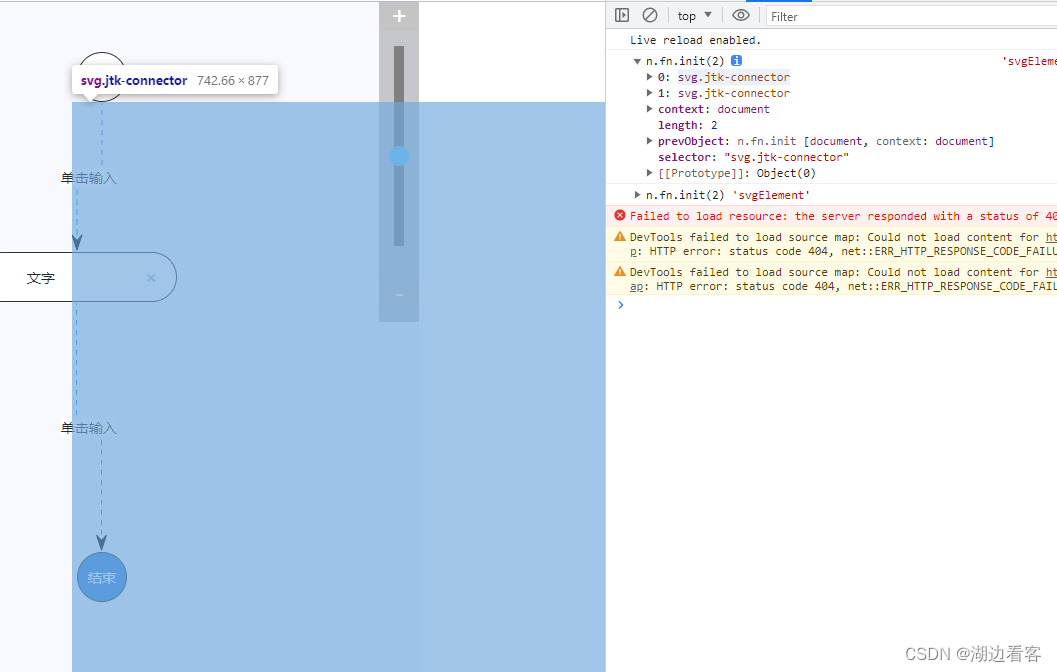

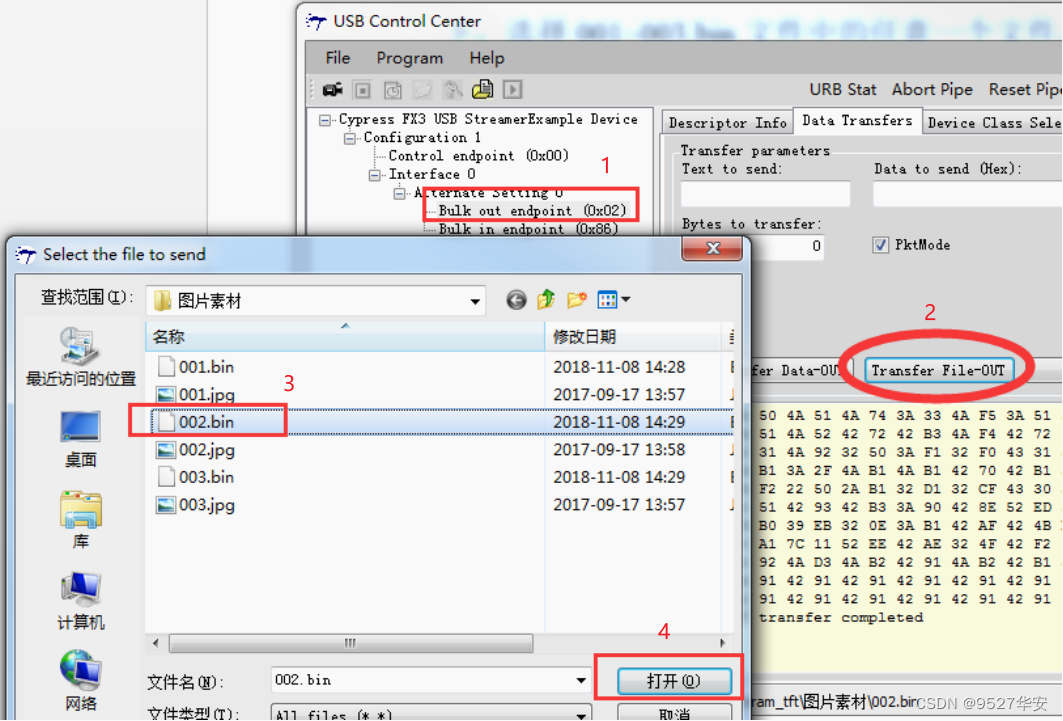

PC上位机发送测试图片

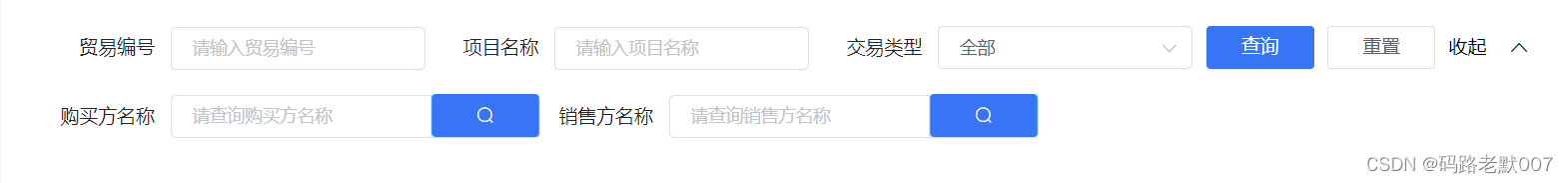

打开Cypress官方软件,按照下图中 1 2 3 4的顺序加载.bin文件的图片,即可完成PC上位机发送图片给FPGA的过程;

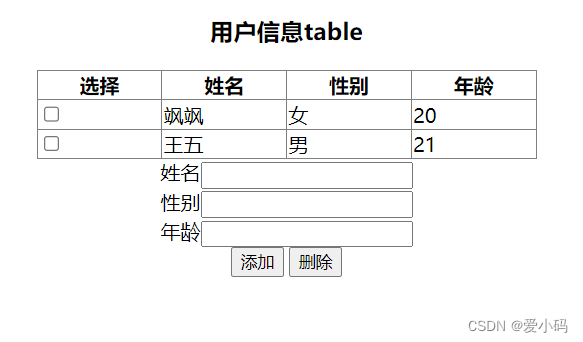

图像接收与缓存

调用一个 FIFO 实现数据图片数据的跨时钟处理,然后将图像数据缓存进DDR3中,然后再读出送显示设备显示;这里的DDR3缓存调用了 MIG IP核,MIG的用户接口为AXI4-FULL,所以图像缓存部分手写了一个AXI4主机及其控制模块实现数据读写;详情请参考源代码;

图像输出显示

我们提供了2套vivado工程,一套是LCD显示屏显示接收的图片,另一套是HDMI显示屏显示接收的图片;二者的分辨率均配置为 800x480,手写了 LCD 驱动和 HDMI 发送模块,详情请参考源代码;

5、vivado工程1–LCD输出显示

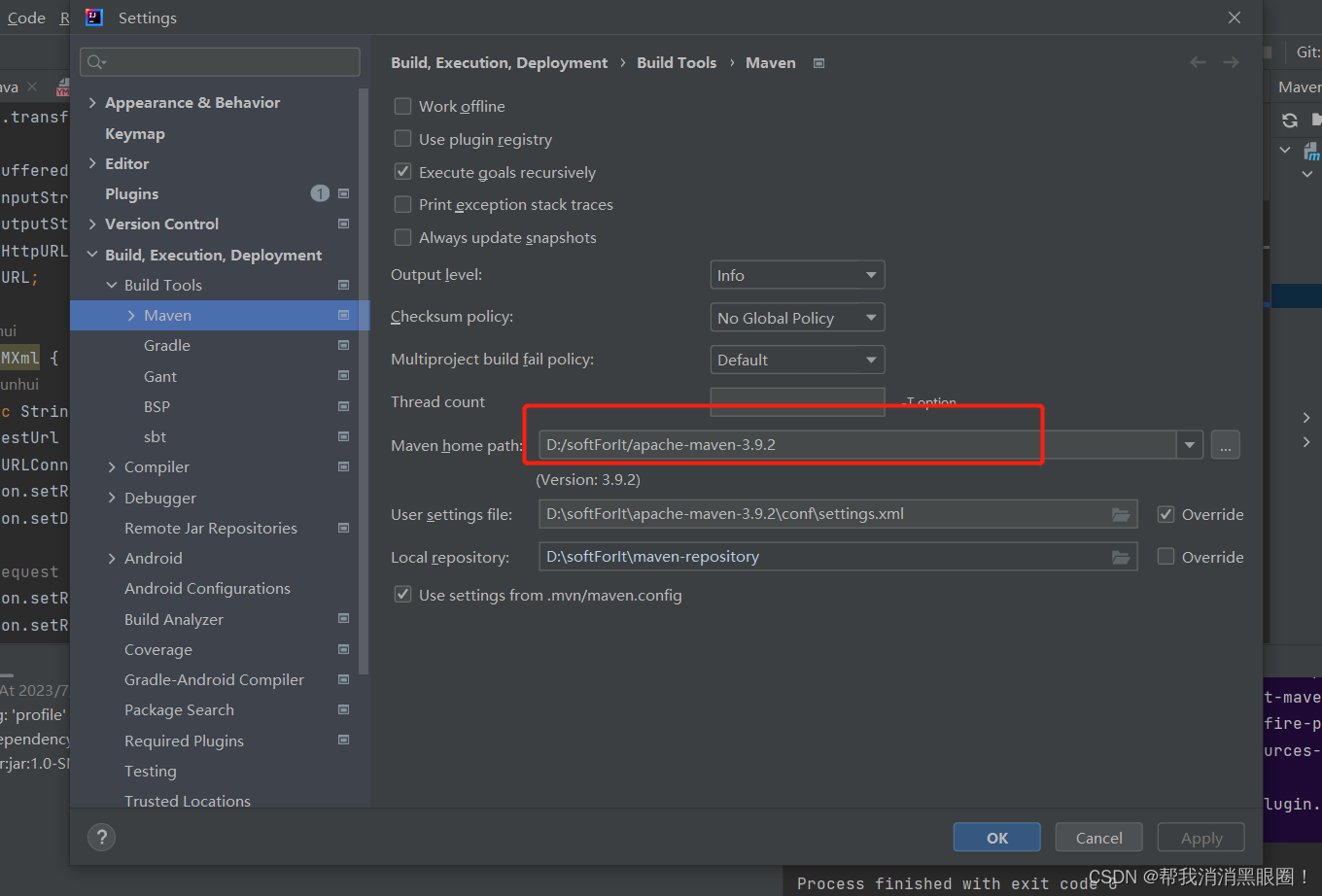

开发板FPGA型号:Xilinx-XC7A35T-2FGG484C-2;

开发环境:vivado2019.1;

输入:图片;

输出:LCD显示屏;

应用:USB2.0接口图片发送;

工程代码架构如下:

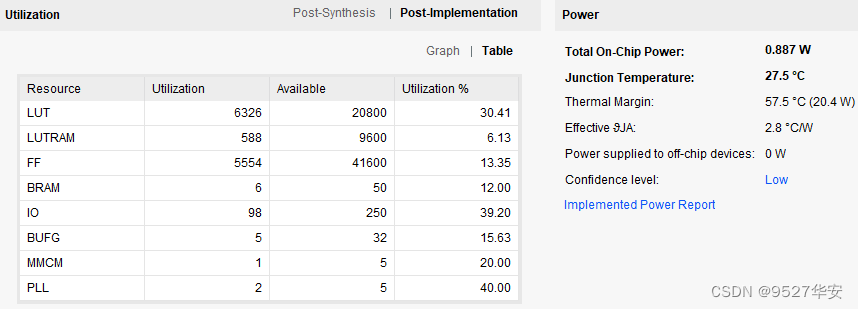

综合编译完成后的FPGA资源消耗和功耗预估如下:

6、vivado工程1–LCD输出显示

开发板FPGA型号:Xilinx-XC7A35T-2FGG484C-2;

开发环境:vivado2019.1;

输入:图片;

输出:HDMI 显示屏;

应用:USB2.0接口图片发送;

工程代码架构如下:

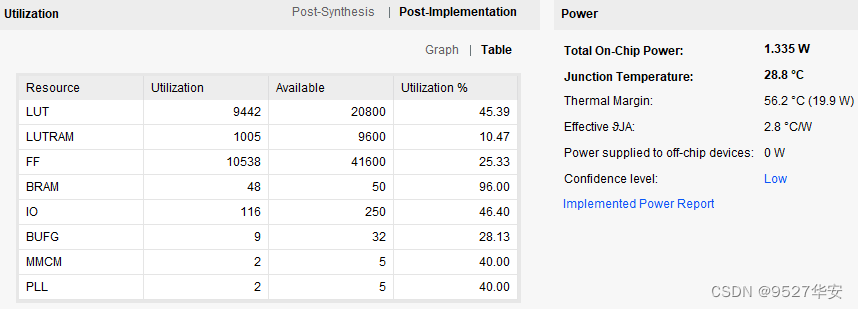

综合编译完成后的FPGA资源消耗和功耗预估如下:

7、上板调试验证

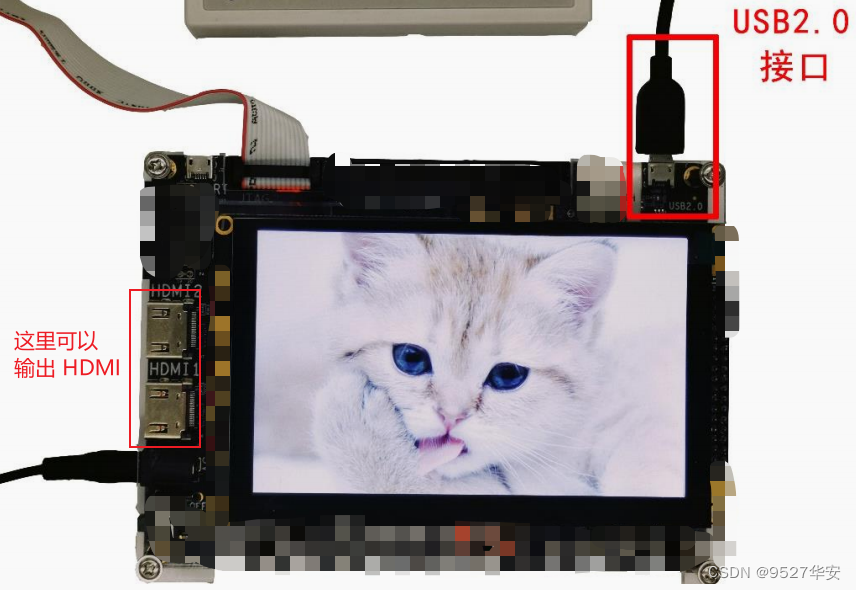

先给板子上电,然后下载CY7C68013A固件,固件一般只需下载一次即可,因为CY7C68013A的原理图设计一般都会外挂一颗e2prom;下载FPGA bit流,打开上位机软件发送图片,这里仅展示 LCD 显示屏输出效果,如下:

8、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式1:私,或者文章末尾的V名片。

网盘资料如下: