目录

一、属性简介

二、示例

2.1 工程说明

2.2 工程代码

2.3 生效确认

一、属性简介

ASYNC_REG属性的作用对象为寄存器,寄存器添加该属性后,即表明寄存器的数据输入口D接收的是来自异步时钟触发器的数据或是该寄存器在一个同步链中属于同步寄存器。ASYNC_REG更多的是使用在异步跨时钟域中。

在Vivado综合的过程中,对于添加了ASYNC_REG属性的寄存器,会将该属性放置到网表的前面,这也能保证网表不会被优化掉,在后面的流程中将正确地对网表进行处理。

ASYNEC_REG的值为布尔型,即只能为TRUE或FALSE,默认值为FALSE,

代码文件使用模板: (* ASYNC_REG="true" *) reg sync_regs;

XDC使用模板:set_property ASYNC_REG TRUE [get_cells sync_regs]

二、示例

2.1 工程说明

设计工程中有三个寄存器reg1,reg2,Q,reg2和Q具有相同的时钟,reg1和reg2时钟来源不同,reg1的输出到reg2,reg2输出到Q,即reg1->reg2->Q,对reg2和Q设置ASYNC_REG。

2.2 工程代码

module async_reg(src_clk,des_clk,ce,d,Q);

input src_clk, des_clk,ce,d;

output Q;

reg reg1;

(*ASYNC_REG="true"*)reg Q,reg2; //添加ASYNC_REG属性

always@(posedge src_clk)

begin

if(!ce)

reg1<=0;

else

reg1<=d;

end

always@(posedge des_clk)

begin

if(!ce)

reg2<=0;

else

reg2<=reg1;

end

always@(posedge des_clk)

begin

if(!ce)

Q<=0;

else

Q<=reg2;

end

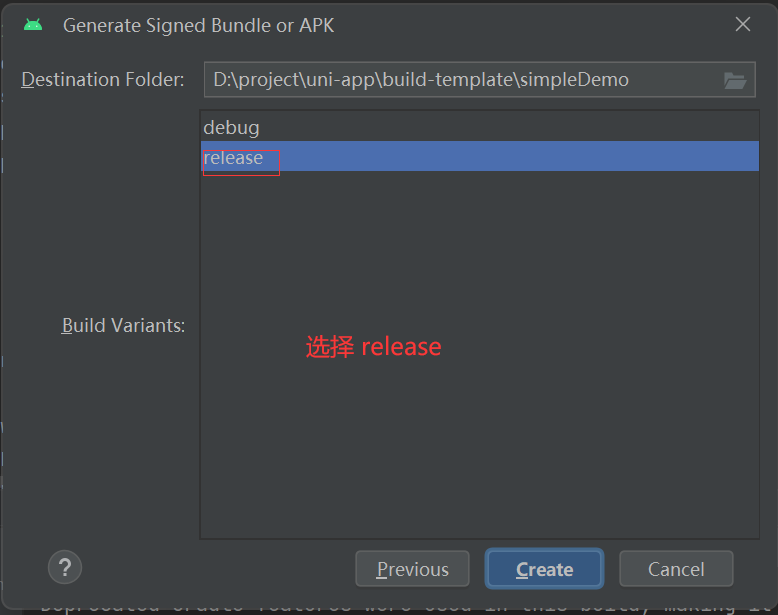

endmodule 2.3 生效确认

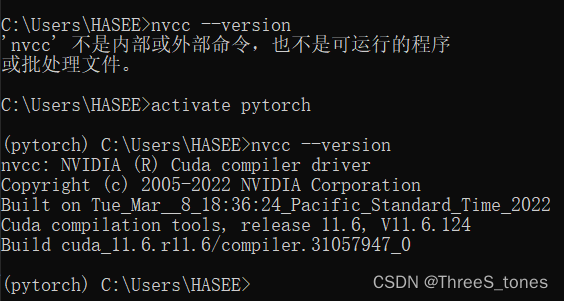

在TCL console中使用tcl命令验证属性是否标记,执行如下两条命令

set register [get_cells -hierarchical -filter "REF_NAME==FDRE"] //获取所有的寄存器

get_property ASYNC_REG $register //获取具有属性ASYNC_REG的寄存器,

结果如下图,第一条命令执行后得到三个寄存器Q_reg reg1_reg reg2_reg,

第二条命令执行后可知只有第1、3个寄存器Q_reg,reg2_reg具有属性ASYNC_REG,符合设计要求。