ARM Cortex-R52 GIC:Generic Interrupt Controller

前言:名词解释

| 英文缩写 | 英文全称(中文释义) |

|---|---|

| GIC | general interrupt controller |

| ITS | Interrupt Translation Service:用来解析中断 |

| SPI | Shared Peripheral Interrupts |

| PPI | Private peripheral interrupt |

| SGI | Software-generated interrupt |

| IRI | interrupt routing infrastructure |

| LPI | Locality-Specific Peripheral Interrupts:用来支持消息中断 |

| PE | Processing element. Abstract machine |

| HPPI | Highest Priority Pending Interrupt |

1.关于GIC

1.1 GIC Overview

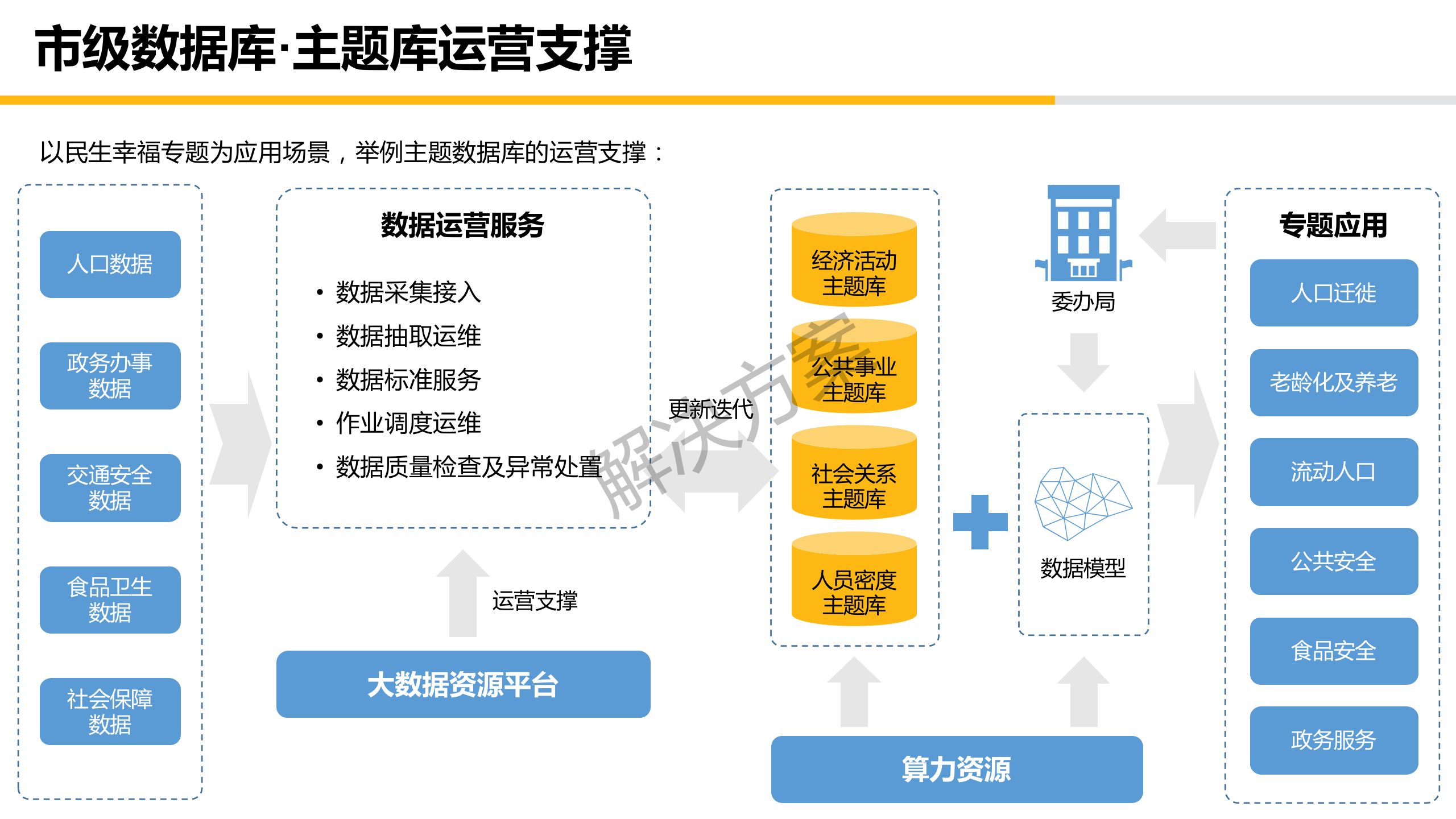

ARM的中断控制器被称为GIC(Generic Interrupt Controller),GIC是支持和管理系统中断的资源的模块。它支持中断优先级、中断路由到CPU或输出端口、中断抢占和中断虚拟化等功能。

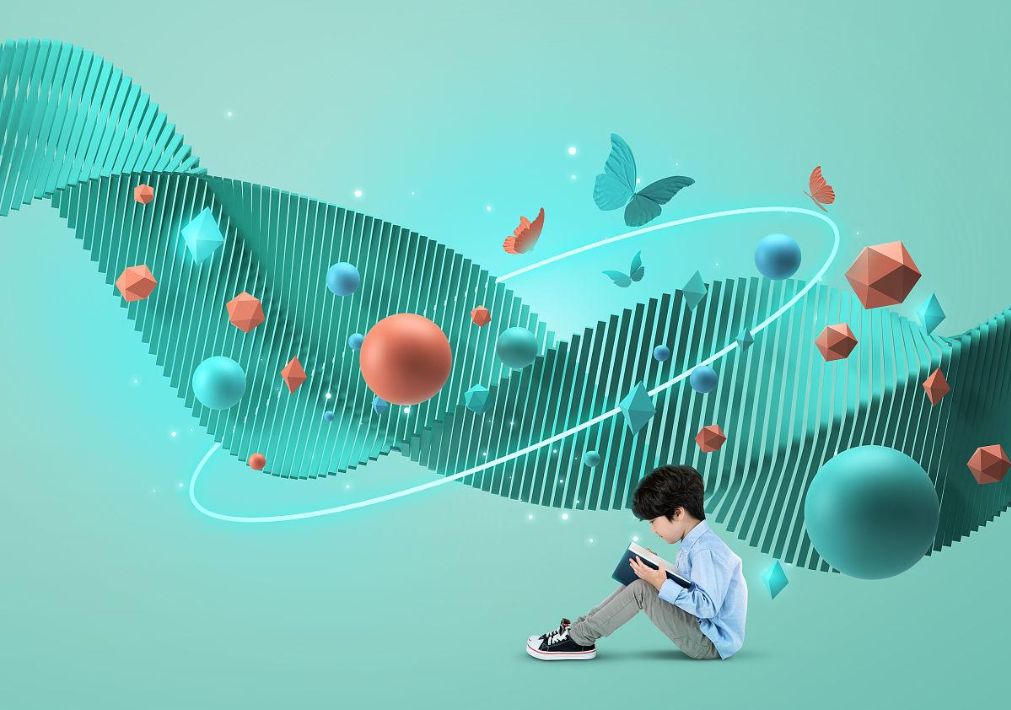

中断控制器是中断源(外设)和CPU之间的桥梁;

中断控制器是中断源(外设)和CPU之间的桥梁;

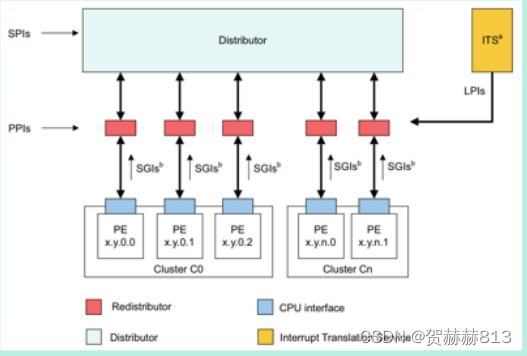

下图是使用GIC管理中断的模型图:

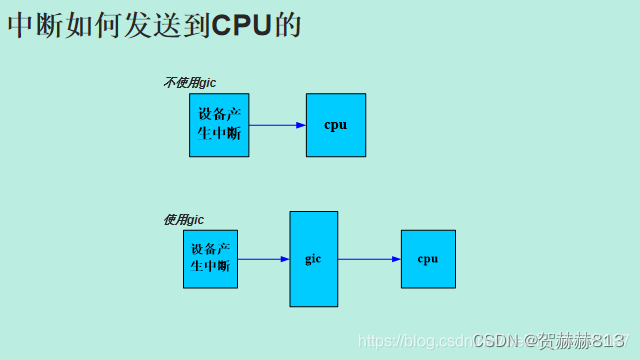

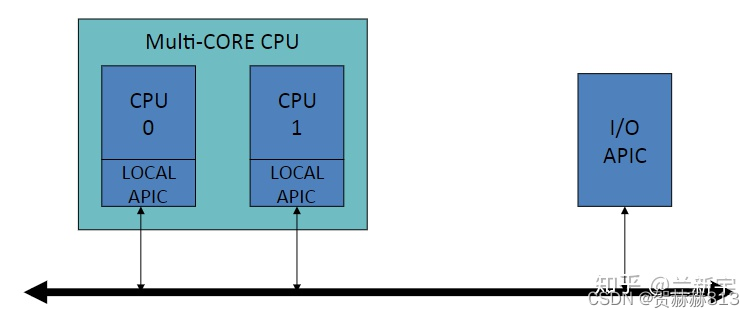

1.2 GIC 架构背景

在多核时代中,中断控制器被分成两个部分可以更好地支持和管理多处理器系统中的中断。其中一部分是连接外设中断源的I/O APIC,由所有CPU共享。I/O APIC可以通过向指定的CPU发送中断消息实现并发中断处理。另一部分是Local APIC,与每个CPU对应,用于控制本地处理器的中断。它可以在单个处理器上快速响应和处理中断请求,在多处理器环境中也可以把中断请求发送到其他处理器或者操作系统内核来协调处理,从而提高中断处理的效率。

总之,随着多处理器技术的不断发展,中断控制器变得越来越复杂,但也使得系统更加灵活和高效。

1.3 ARM R52 GIC-v3架构

1.3.1 overView

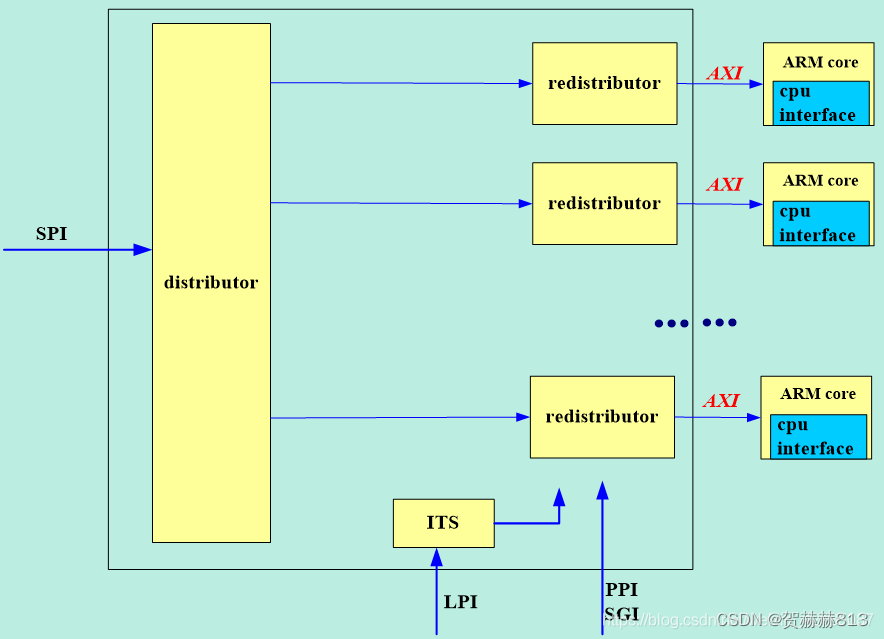

Cortex-R52处理器采用了ARM公司推出的GIC V3架构,这是一种高度灵活和可扩展的中断控制器架构,特别适用于多核处理器系统。GIC V3架构包括一个内部的GIC分配器(Distributer),每个核还包含一个GIC重分配器(Redistributor)。

Distributer接收外设(SPI)和核心(PPI)的有线中断。 GIC分配器仲裁路由到每个核心的中断以确定最高优先级挂起中断(HPPI),然后将其传递给GIC CPU界面。 来自核的激活,去激活和软件生成的中断通过GIC CPU接口传递以更新GIC分配器的状态。 GIC分配器包含内存映射的配置和状态寄存器。 GIC分配器包含每个中断目标一个再分配器。 再分配器主要负责包含PPI和SGI的寄存器。

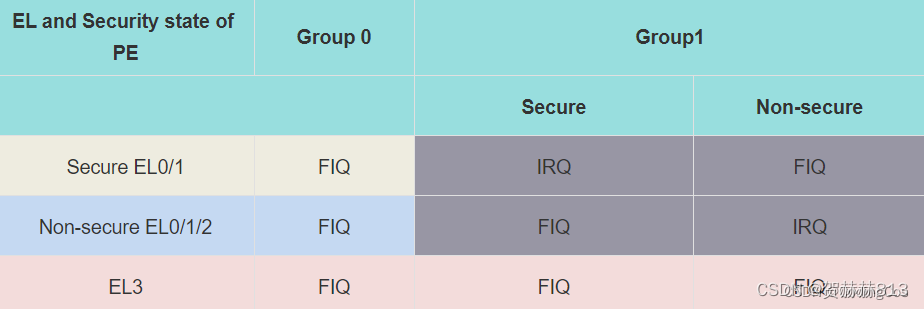

GIC CPU接口包括处理物理中断的部分和处理虚拟中断的部分。 GIC CPU接口包含可作为系统寄存器访问的配置和状态寄存器。 中断被配置为Group 0中断或Group 1中断。 Group 0中断使用FIQ发出信号,而Group 1中断使用IRQ发出信号。

GIC CPU接口处理物理中断的部分从GIC分配器接收HPPI。 它执行抢占计算并向核心发出FIQ或IRQ信号。 来自核心的激活,去激活和软件生成的中断通过CPU接口传回到分配器。 GIC CPU接口处理虚拟中断的部分最多可以包含四个虚拟中断,其中优先级最高的用于向核心生成虚拟FIQ或虚拟IRQ。

distributor: SPI中断的管理,将中断发送给redistributor;

redistributor: PPI,SGI,LPI中断的管理,将中断发送给cpu interface;

cpu interface: 传输中断给 core;

cpu interface 是实现在 core 内部的,distributor,redistributor,ITS是实现在gic内部的.

1.3.2 V3功能升级

相对于V2,V3升级的主要功能包含:

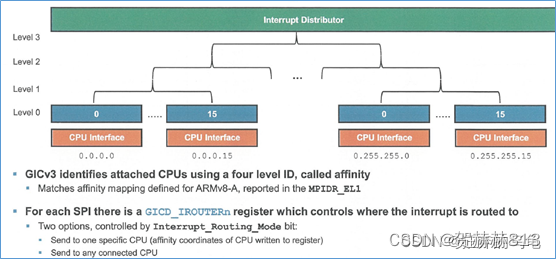

- 使用属性层次(affinity hierarchies),来对core进行标识,

使gic支持更多的core - 将cpu interface独立出来,用户可以将其设计在core内部

- 增加redistributor组件,用来连接distributor和cpu

interface - 增加了LPI,使用ITS来解析

- 对于cpu interface的寄存器,增加系统寄存器访问方式

1.3.3 功能描述

GIC Distributer类似于传统计算机系统中的I/O APIC,它负责将来自各种中断源的中断请求转发给相应的Redistributor,并根据CPU的配置和优先级设置进行派发。与传统的I/O APIC不同的是,GIC Distributer还支持像处理器间直接消息传递(Inter-Processor Interrupt,IPI)这样的特殊中断类型,可以通过GIC协议灵活地配置和管理各种中断源。

GIC Redistributor类似于传统计算机系统中的Local APIC,它负责为每个CPU接收并处理来自Distributer派发的中断请求,以及发送处理器间直接消息传递(IPI)的请求。GIC Redistributor可以访问Distributer的寄存器和内存映射区域,以获取有关中断状态和优先级的信息,并根据这些信息向处理器发送中断或IPI请求。此外,GIC Redistributor还支持处理器仲裁,以确保同一时间只有一个CPU处理具有相同优先级的中断。

启用和禁用 SGI 和 PPI;

(2)设置 SGI 和 PPI 的优先级;

(3)将每个 PPI 设置为电平触发或边缘触发;

(4)将每个 SGI 和 PPI 分配给中断组;

(5)控制 SGI 和 PPI 的状态;

(6)内存中数据结构的基址控制,支持 LPI 的相关中断属性和挂起状态;

(7)电源管理支持。

1.3.3.3 CPU interface详述

CPU interface详述

CPU interface 这个 block 主要用于和 process 进行接口。

该block的主要功能包括:

(1)enable 或者 disable CPU interface 向连接的 CPU assert 中断事件。对于ARM,CPU interface block 和 CPU 之间的中断信号线是 nIRQCPU 和 nFIQCPU。如果disable了中断,那么即便是 Distributor 分发了一个中断事件到CPU interface,但是也不会 assert 指定的 nIRQ 或者 nFIQ 通知 processor。

(2)ackowledging中断。processor 会向 CPU interface block 应答中断(应答当前优先级最高的那个中断),中断一旦被应答,Distributor 就会把该中断的状态从 pending 状态 修改成 active 或者 pending and active(这是和该 interrupt source 的信号有关,例如如果是电平中断并且保持了该 asserted 电平,那么就是pending and active)。processor ack了中断之后,CPU interface就会deassert nIRQCPU和nFIQCPU信号线。

(3)中断处理完毕的通知。当 interrupt handler 处理完了一个中断的时候,会向写 CPU interface 的寄存器从而通知 GIC CPU 已经处理完该中断。做这个动作一方面是通知 Distributor 将中断状态修改为 deactive,另外一方面,CPU interface 会priority drop,从而允许其他的 pending 的 interrupt 向 CPU 提交;

(4)设定priority mask。通过priority mask,可以 mask 掉一些优先级比较低的中断,这些中断不会通知到CPU;

(5)设定preemption的策略;

(6)在多个中断事件同时到来的时候,选择一个优先级最高的通知 processor

注意:GICv3架构的cpu interface从gic内部剥离,实现在PE的内部。并且将cpu interface的寄存器,提供了系统寄存器访问方式,从而实现中断的快速响应。

1.4 GIC-V3和ARM核的连接

1.5对于core的标识

GICv3中,对于core的标识,使用了属性层次的方式,来进行标识,从而可以支持更多的core。

2.GIC 一些概念

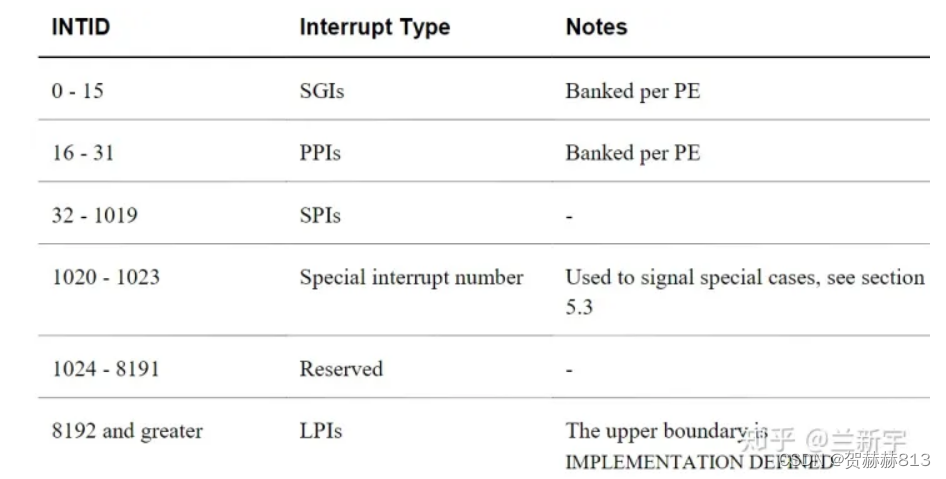

2.1中断编号

GIC中断源的编号从0开始,0到15是SGI(Software Generated Interrupt),所谓"software generated"。

编号16到31是PPI(Private Peripheral Interrupt),所谓"private",是指这个中断为CPU私有/专用。

与专有的PPI相对应的就是所有CPU全局共享的SPI(Shared Peripheral Interrupt),编号从32到1020。

2.2 中断分类

2.2.1 Private Peripheral Interrupts (PPIs)

PPI(Private Peripheral Interrupts,私有外设中断)是由特定于单个核心的外设产生的有线中断。每个核心具有16个PPI,INTID16-INTID31。输出接口不支持PPI。没有被分配使用的PPI将作为Cortex-R52处理器顶层的额外中断输入提供。配置未分配的PPI可以选择上升沿触发或低电平触发。

那什么中断会有这种特性呢?

比如通用定时器中断啊,温度传感器中断之类的。

2.2.2 Shared Peripheral Interrupts (SPIs)

SPI是一种由特定于单个核心的外设产生的有线中断,可以被通过软件配置路由到一个特定的核。每个Cortex-R52处理器都具有960个可配置的SPI,这些SPI作为处理器的顶层输入信号提供给其他组件使用。

那么如何确定哪些SPI被分配给哪个核心?

在每个核心中,通过低延迟硬件将32个唯一的SPI路由到该核心,而其他所有核心则使用常规延迟硬件将同样的SPI路由到它们。对于每个核心而言,INTID(32x+32)到INTID(32x+63)的SPI被视为低延迟(其中x = 0、1、2或3),即它们具有更快的响应时间和更高的优先级,可以更快地从硬件设备接收并处理SPI中断请求。

最后,每个SPI都可以配置为上升沿触发或高电平触发,并且通过编程相应的SPI路由信息来实现。SPI[0]对应于INTID32,而SPI[30]对应于INTID991。

2.2.3 Software Generated Interrupts (SGIs)

指由 CPU 直接写对应的寄存器触发中断,因而这种中断不是由硬件产生的,而是由软件主动产生的。这种特殊的中断主要用于核间通信。当处理器需要中断应用程序执行时,可以使用SGI生成中断信号。SGI的数量有限,每个CPU核只能生成16个SGI,每个SGI都有一个独特的编号(INTID0-INTID15)。SGI是边沿触发中断,在生成SGI时,SGI信号会从低电平跳变到高电平,然后维持高电平状态,直到中断服务程序将其清除为止。这些属性使SGI非常适合进行异步通信和同步协议的实现,并可用于更好地支持多处理器系统。

SGI (Software Generated Interrupt) 和 PPI (Private Peripheral Interrupt) 都是 ARM 处理器中的中断信号。每个 CPU 核都有自己的 SGI 或 PPI 中断,不同核的同种类型中断共享相同的编号。因此,它们都采用了 “banked” 形式的中断源,即每个 CPU 核都可以接收到来自同一种类型中断的信号,但是在处理中断时会根据中断编号进行区分和处理。其中,SGI 是由软件触发的中断,用于处理特定的事件或情况。PPI 则是专门为外围设备设计的中断,用于处理与外设相关的事件或情况。这些中断信号都有各自的优先级,并按照优先级高低被处理。这种中断机制可以使系统在出现多个异步事件时能够快速响应并作出正确的处理。

2.2.4 LPI: Locality-Specific Peripheral Interrupts

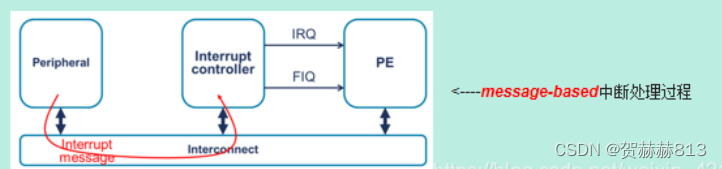

在gicv3中,引入了一种新的中断类型。message based interrupts,消息中断

外设,不在通过专用中断线,向gic发送中断,而是写gic的寄存器,来发送中断

这样的一个好处是,可以减少中断线的个数;为了支持消息中断;gicv3,增加了LPl;来支持消息中断。并且为他分配了特别多的中断号,从8192开始到16777216

注意:R52虽使用的是V3架构,但是不支持LPI

2.3 中断分组

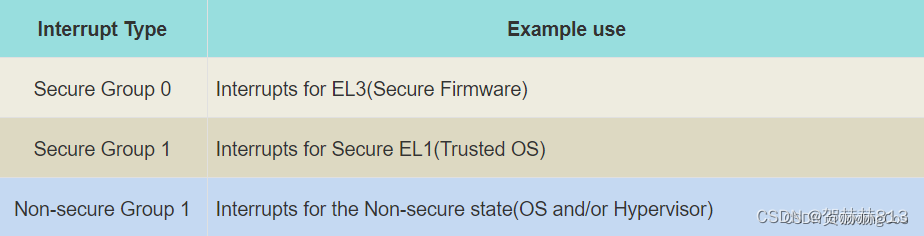

在 GICv3 中断控制器中,对中断进行了分组:Group0、Secure Group1、Non-secure Group1。

2.4 中断标记

当一个中断进来的时候,cpu interface 会根据中断的 分组类型 和当前 PE 的 security 状态 来决定是标记为 IRQ 还是 FIQ。

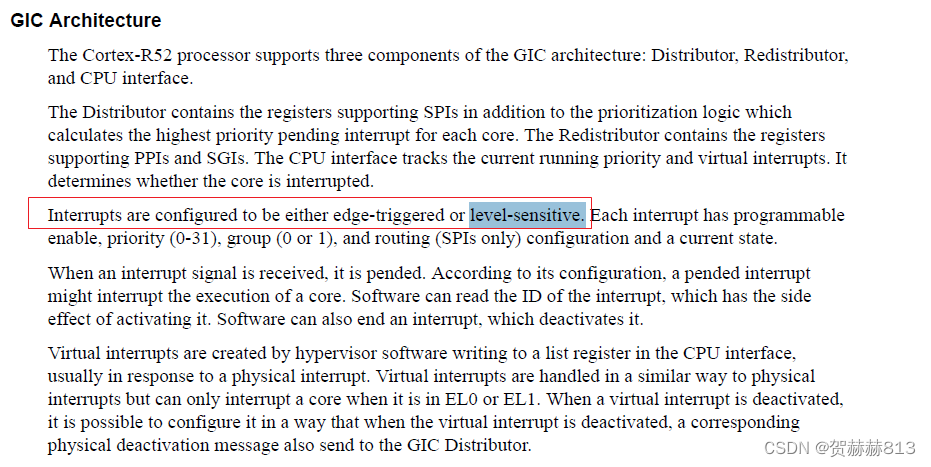

2.5 中断触发方式

◾edge-triggered: 边沿触发,当中断源产生一个边沿,中断有效

◾level-sensitive:电平触发,当中断源为指定电平,中断有效

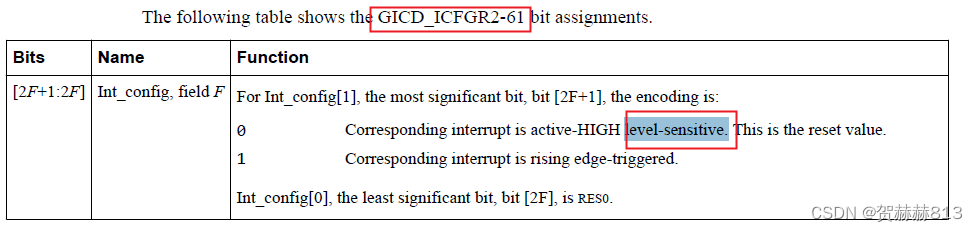

R52可以通过寄存器配置

例如:

例如:

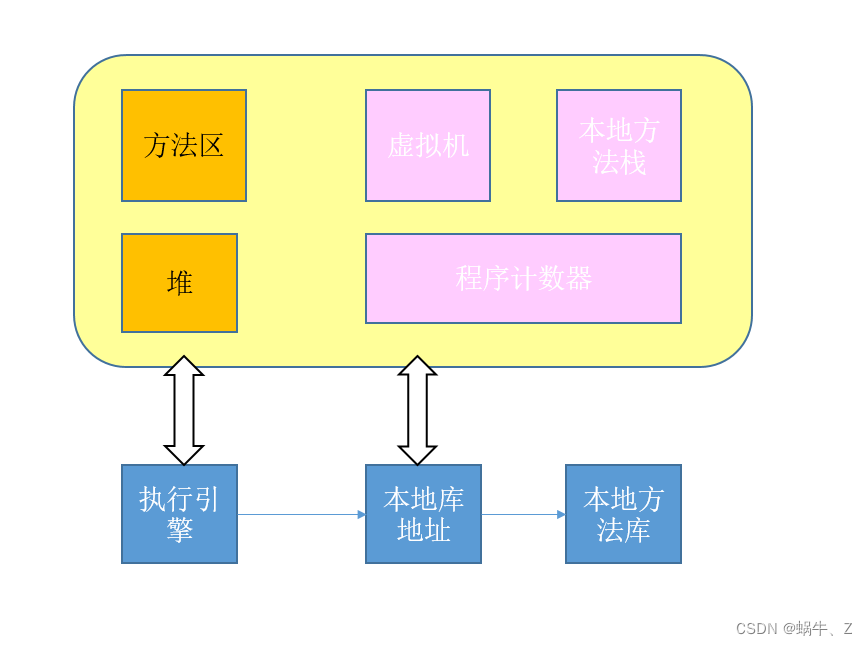

3.CPU核访问GIC寄存器的方式

ARM CORE访问GIC的方式包括以下两种:

- Memory-mapped寄存器方式:GIC Distributor和CPU接口中的控制和状态寄存器都映射到物理地址空间。当CORE需要读写相关的GIC寄存器时,直接通过对应的物理地址进行读写操作即可。

- CPU指令方式(系统寄存器方式):针对部分功能,GIC支持使用专门的体系结构扩展指令来进行访问。在ARMv7-A架构中,提供了MRC(Move from register to coprocessor)和MCR(Move register to coprocessor)两个指令,用于向GIC写入或读取相应的控制和状态信息;而在ARMv8-A架构中,引入了MSR(Move to system register)和MRS(Move from system register)两个指令,这些指令不仅能够访问GIC,还可以对其他系统级寄存器进行访问。

GIC-V3的distribbutor/redistributor使用的memory-mapped方式;

ITS、CPU interface 既可以使用memory-mapped方式,也可以使用系统寄存器方式;

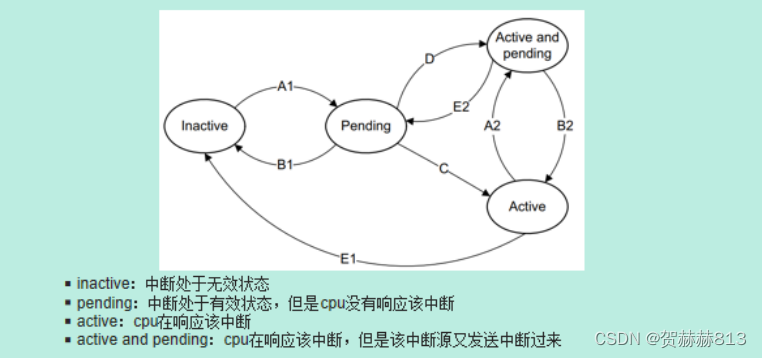

4.中断的状态转换

中断的优先级和可以被转发到的core列表都在Distributor中配置,Distributor确定可以传递到core的处于pending状态的最高优先级的中断, 然后转发到与该core相连的CPU interface。在CPU interface中,中断被依次发送给core,然后在core中会发生FIQ或者IRQ异常。

中断的优先级和可以被转发到的core列表都在Distributor中配置,Distributor确定可以传递到core的处于pending状态的最高优先级的中断, 然后转发到与该core相连的CPU interface。在CPU interface中,中断被依次发送给core,然后在core中会发生FIQ或者IRQ异常。

Core会执行异常处理器(exception handler),handler必须从CPU interface 寄存器中获取到该中断的ID号,然后开始处理中断源。当处理完成后,handler必须对CPU interface的寄存器(EOI)进行写入,以说明中断处理完成。

一个中断状态变化过程:

Inactive -> Pending:当中断被外设断言时

Pending -> Active:当中断处理器(handler)获知了当前中断

Active -> Inactive:handler处理完成了中断

在Distributor中有相关寄存器能显示不同中断ID的当前中断状态,GIC提供寄存器来控制SPI中断转发到哪些core。这种机制使操作系统能够在core之间进行共享和分发中断。

参考阅读:

https://blog.csdn.net/sinat_32960911/article/details/128083997

https://blog.csdn.net/weixin_42135087/article/details/107039588

https://zhuanlan.zhihu.com/p/85313527

https://zhuanlan.zhihu.com/p/90074320

https://zhuanlan.zhihu.com/p/85313527

https://blog.csdn.net/weixin_42135087/article/details/111713444

https://blog.csdn.net/yhb1047818384/article/details/86708769

https://blog.csdn.net/qijiuliushisan/article/details/112384636

https://zhuanlan.zhihu.com/p/443815543

https://blog.csdn.net/luolaihua2018/article/details/126859967

https://blog.csdn.net/weixin_42135087/article/details/107202458

https://zhuanlan.zhihu.com/p/90074320

Arm® Cortex®-R52 Processor Technical Reference Manual