CPU

功能

指令控制:取指、分析、执行

操作控制:一条指令的功能由若干操作信号组合实现

时间控制、数据加工、中断处理

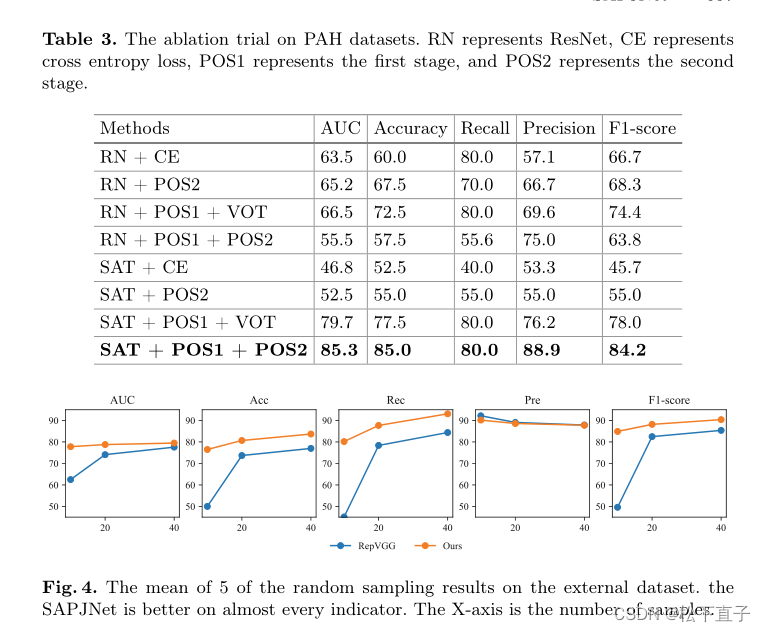

基本结构

运算器

ALU:算术/逻辑运算

暂存寄存器:暂存从主存读来的数据,透明

ACC:通用寄存器,暂存ALU的结果

X:存放操作数和各种地址信息,如堆栈指针SP指示栈顶地址

PSW:OF、SF、CF、ZF

移位器

计数器:控制乘除运算的操作步数

控制器

PC:指出下一条指令在主存中的存放地址

IR:存放当前正在执行的指令

指令译码器:对操作码字段译码,向控制器提供特定的操作信号

MAR

MDR

时序系统

微操作信号发生器:产生控制整个计算机系统所需的各种控制信号

透明的寄存器:MAR、MDR、IR

不透明的寄存器:X、PSW

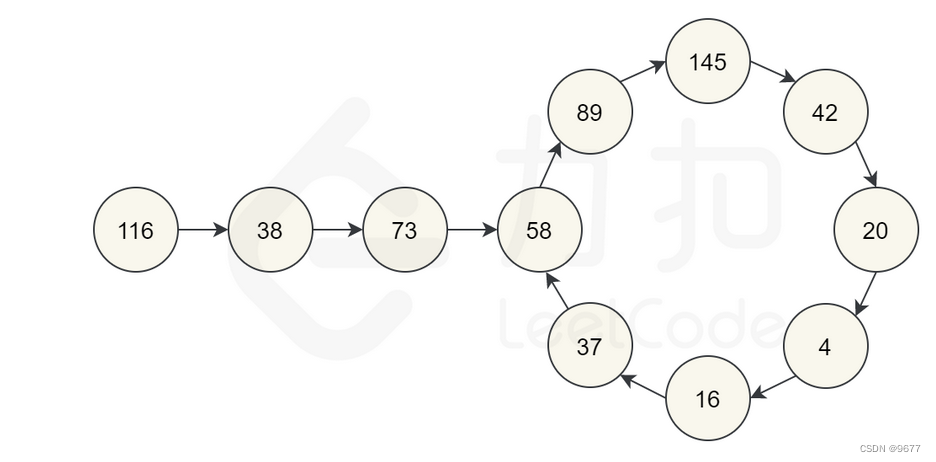

指令执行过程

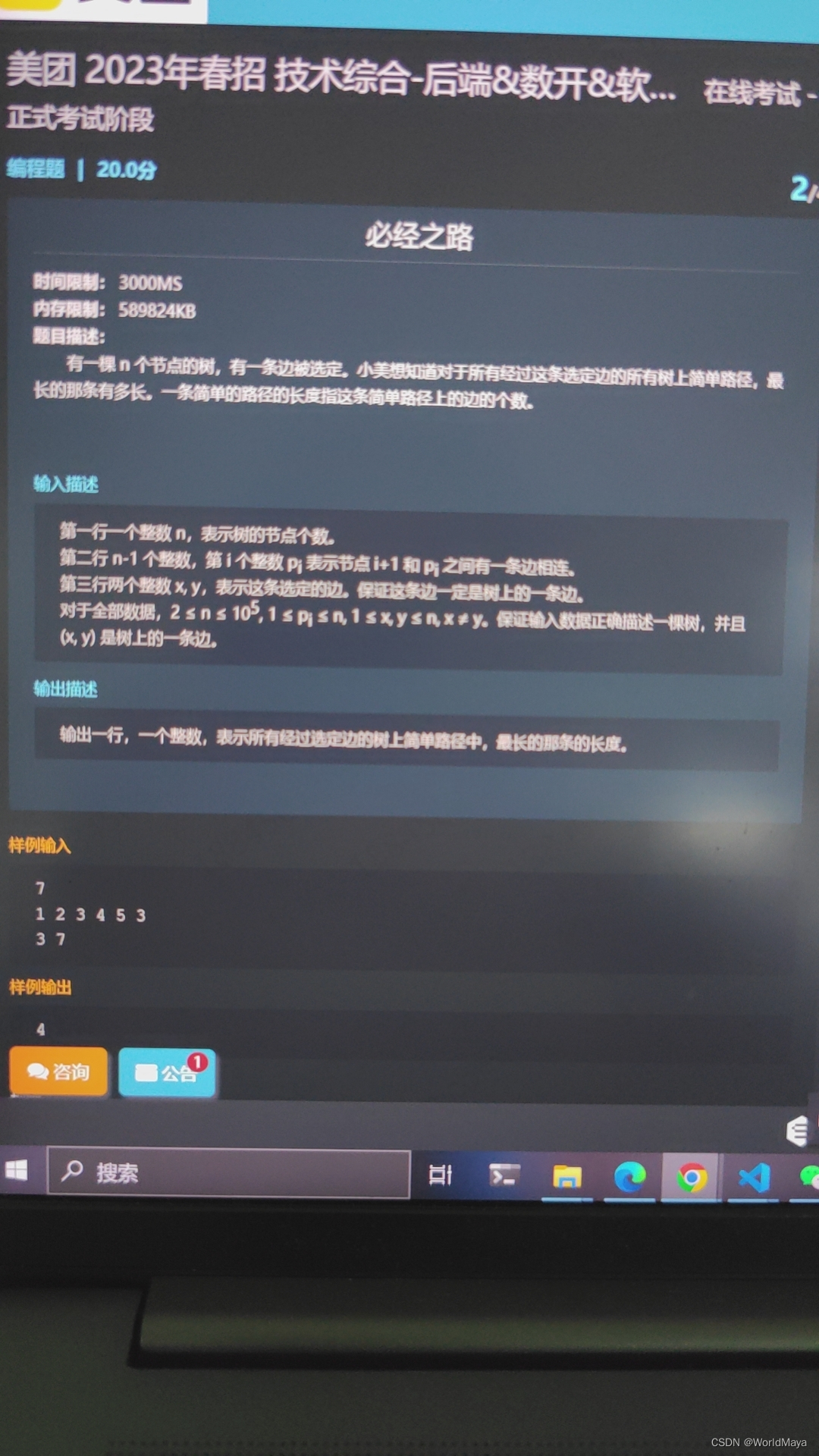

指令周期

指令周期:CPU从主存取出并执行一条指令的时间

指令周期常用若干机器周期表示

一个机器周期包含若干时钟周期(节拍、T周期、CPU操作的最基本单位)

机器周期可视为所有指令执行过程的一个基准时间

每个节拍的宽度对应一个时钟周期

上述4个周期都有CPU访存操作:

取指周期FE:取指令

间址周期IND:取有效地址

执行周期EX:取操作数

____没有统一的数据流

中断周期INT:保存程序断点

指令执行方案

单指令周期:所有指令选用相同的执行时间,串行执行

多指令周期:串行执行

流水线:并行执行

数据通路

数据通路:实现CPU内部的运算器与寄存器、寄存器与寄存器的数据交换

控制器

CU的输入信号来源:

标志:来自执行单元的反馈信息

微指令

异常和中断

定义

异常:CPU内部产生的意外事件,内中断,与正在执行的指令相关的同步事件

中断:CPU外部的设备向CPU发出的中断请求,外中断,与正在执行的指令无关的异步事件

分类

异常的分类:(按照发生原因和返回方式)

故障:引起故障的指令执行后、执行结束前被检测到的异常,如缺段缺页、非法操作码、除数为0

自陷Trap:预先安排的断点

终止:随机发生的使计算机无法继续执行的硬件故障

区别

(1)缺页、溢出等异常事件由特定指令在执行过程产生,中断不和任何指令关联,不阻止任何指令完成

(2)异常的检测由CPU自身完成,不必通过外部的某个信号通知CPU;CPU必须通过中断请求线获取中断源的信息,才能知道哪个设备发生了哪种中断

响应过程

从CPU检测到异常/中断,到调出相应的处理程序的过程

关中断 IF=0:禁止响应新的中断

保存断点和程序状态

识别异常和中断并转到相应的处理程序

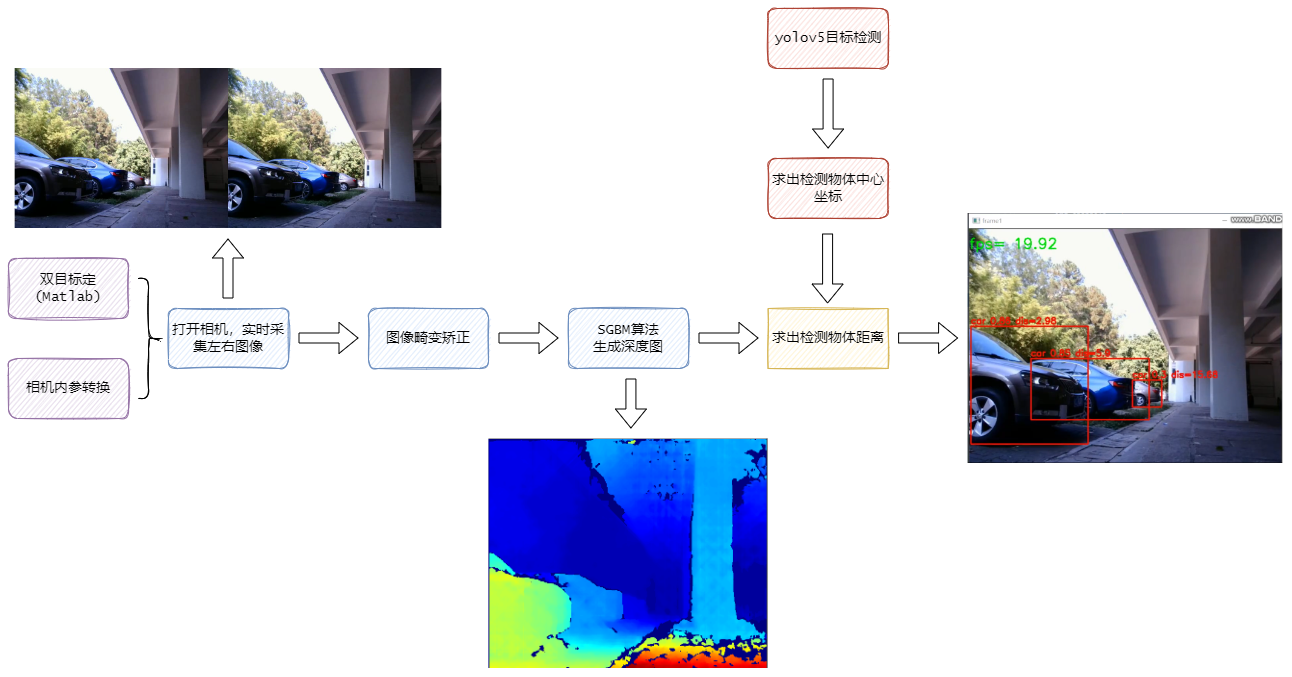

指令流水线

提高处理机的并行性

流水线技术:时间上,将一个任务分解成几个子阶段,在不同的功能部件执行

超标量处理机:空间上,一个处理机内设置多个执行相同任务的功能部件并行工作

冒险

结构冒险(资源冲突):多条指令在同一时刻争用同一硬件资源

数据冒险(数据冲突):下一条指令会用到当前指令计算出的结果

控制冒险(控制冲突):遇到改变指令执行顺序的情况,会改变PC值,造成断流

高级流水线技术

超标量流水线技术(动态多发射技术):每个时钟周期内可并发执行多条独立指令,以并行操作方式将两条或多条指令编译并执行。

超长指令字技术(静态多发射技术):由编译程序挖掘指令间潜在的并行性,组合成一条具有多个操作码字段的超长指令字

超流水线技术:功能段划分级数增多

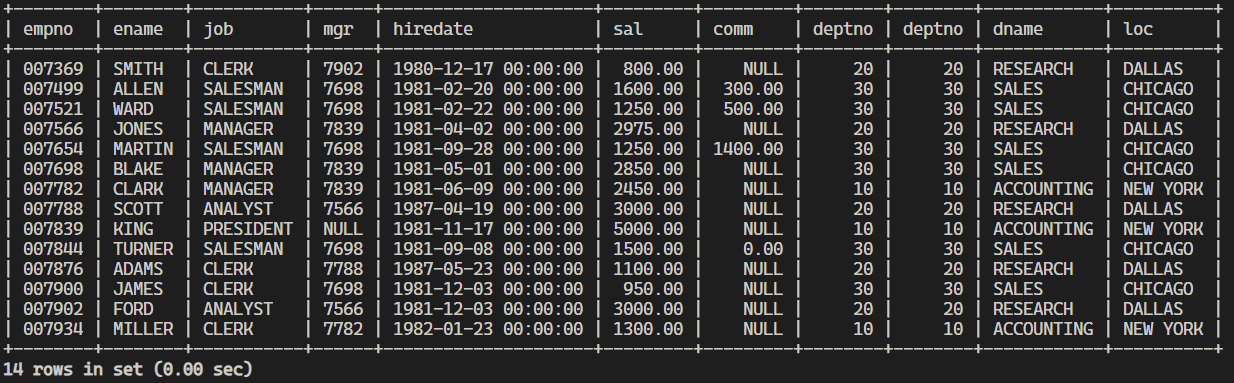

多处理器的基本概念

SISD、SIMD、MIMD

单指令流单数据流(SISD)结构:

传统的串行结构,一个处理器和一个存储器

单指令流多数据流(SIMD)结构:

数据级并行,一个指令控制部件和多个处理单元

多指令流多数据流(MIMD)结构

硬件多线程

细粒度多线程:多个线程轮流交叉执行指令,多个线程直接的指令不相关,可以乱序并行执行。处理器可以在每个时钟周期切换线程

粗粒度多线程:仅在一个线程出现较大开销的阻塞时,才切换线程。流水线阻塞时,清除阻塞的流水线,新线程的指令开始执行前需重载流水线

同时多线程SMT:指令级并行的同时实现线程级并行,超线程

![[HBZ分享] 小米手机如何解BL锁](https://img-blog.csdnimg.cn/7974185433104db192cc9f4f871078fb.png)