ZYNQ从架构上可以划分为两大模块,一个是PS(处理器系统),另一个是PL(可编程逻辑)

PS由APU、内存接口、IO外设、互连线4大模块组成。

1、APU(Application Processor Unit)应用处理单元

即PS【可编程逻辑里面最最核心的东西】,它由两个双核心的Cortex-ARM A9、一些缓存和存储组成。

APU里面有几个比较重要的部分:

一个是ACP,全名Accelerator Coherency Port,加速器一致端口,作用是允许从PL到CPU存储空间的一致性访问,

另外一个是DMA,全名直接存储访问,它支持多种传输模式:内存到内存,内存到外设,外设到内存,有8个通道

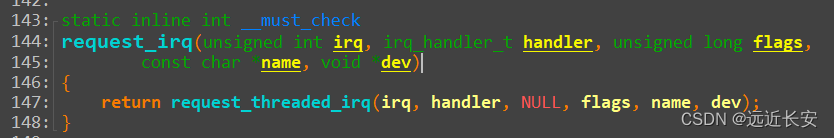

下一个是中断控制器,GIC,通用中断控制器

2、内存接口

Memory Interfaces,包括两部分:一个是动态内存控制器(dynamic memory controller),一个是静态内存控制器(static memory controller)

3、IO外设(I/O Peripherals)

USB 2.0 OTG、Ethernet、CAN、SD/SDIO、SPI、UART、I2C、118个GPIO bit

4、互连线

APU、IOP、和内存单元互相连接,并通过一个多层的AXI互连线与PL连接

PS接口

PS外部接口

PS外部接口使用一些不能被赋值为PL引脚的专用引脚,包括:

- 时钟、复位、启动模式和参考电压

- 54个专用的多路复用引脚,可以通过软件来配置使其连接到任意的内 部I/O外设或静态内存控制器

- 32bit或16bit的DDR2/DDR3内存

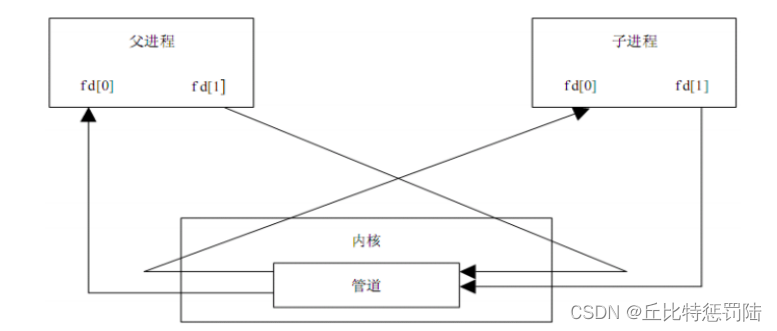

PS-PL接口

进行数据通信的AXI 接口

- 2个32-bit的AXI控制接口

- 2个32-bit的AXI从属接口

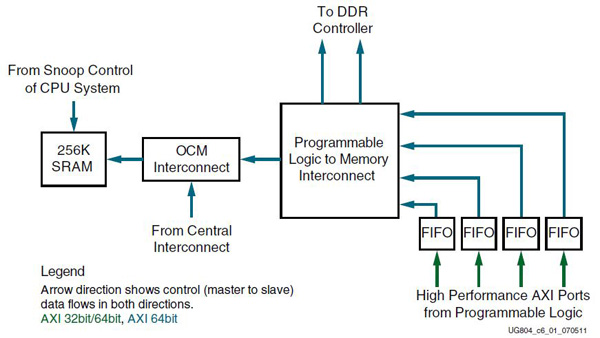

- 4个64/32-bit的AXI从属接口来直接访问DDR内存和OCM,这个端口被称为高性能AXI端口

- 1个64-bit的AXI从接口(ACP PORT)支持到CPU内存的一致性访问

DMA、中断、事件信号

EMIO允许未映射的访问PL I/O

时钟和复位

- 4个PS时钟输出到PL进行开始、停止控制

- 4个PS复位输出到PL

配置和其他

- 处理器配置访问端口(PCAP)支持完全和部分PL配置,以及安全的PS启动镜像加密和认证

- XADC接口

- JTAG接口

关于高性能AXI端口,结构图如图1所示:

可以看出,有两个连接到DDR控制器,另一个连接到多端口的片上存储

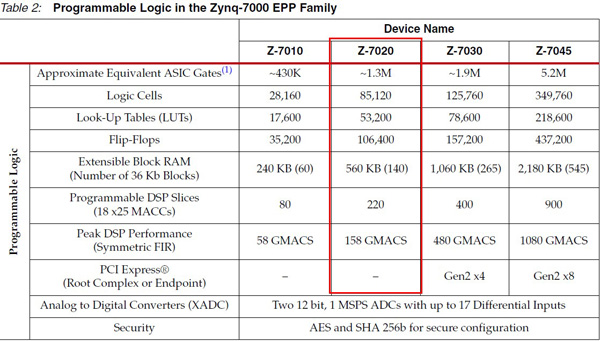

PL部分包含:

- 可配置逻辑块

- 36Kb块RAM

- DSP切片

- 可编程IO块

- XADC

- PL可配置模块

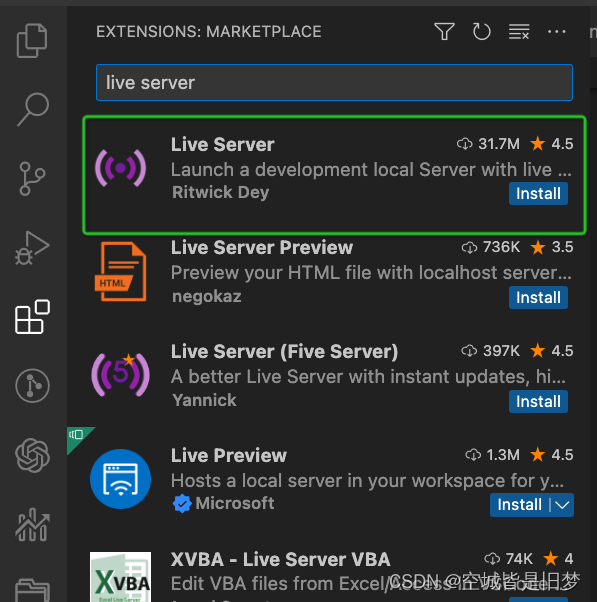

图2是详细的信息,红色矩形所示是zedboard的PL部分的详细参数

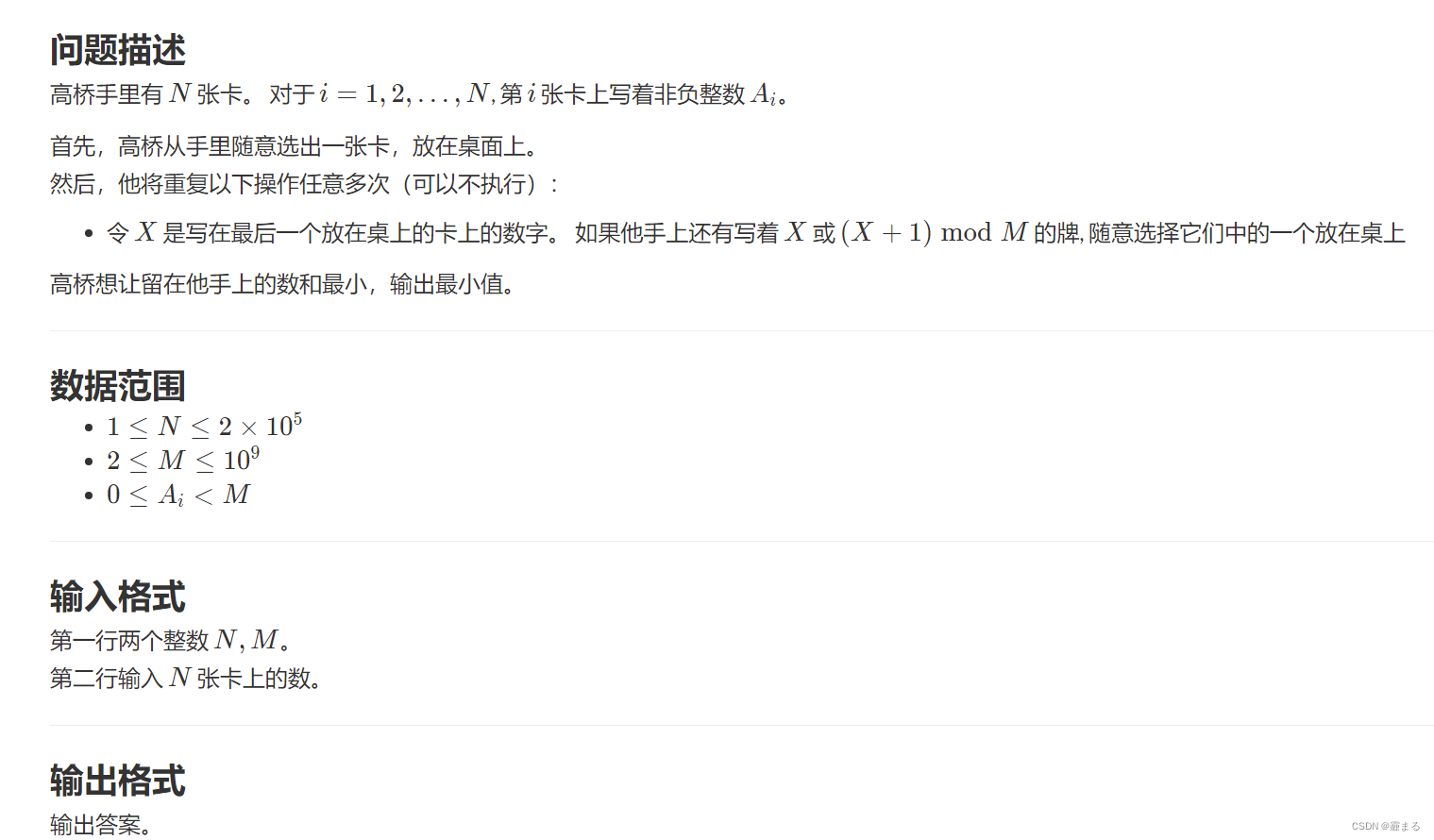

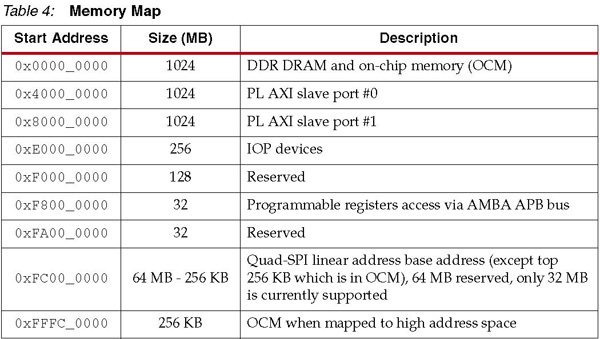

Zynq-7000 EPP系列产品支持4GB的内存空间,详细组织方式如图3所示

对于ZEDBOARD而言,由于其开发板配置了512MB的DDR3内存芯片,故其实际的DDR地址范围是0x00000000~0x1FFFFFFF。

![[golang]Go语言从入门到实践-反射](https://img-blog.csdnimg.cn/76c88bb3476c461caec52f9c4ec5cc46.png)