来源:飞凌嵌入式官网

www.forlinx.com

在多核异构CPU中,多个内核就如同多个大脑,而外设和内存等资源就如同手足,那么多个大脑该如何控制手足才能保证它们正常有序地运行呢?

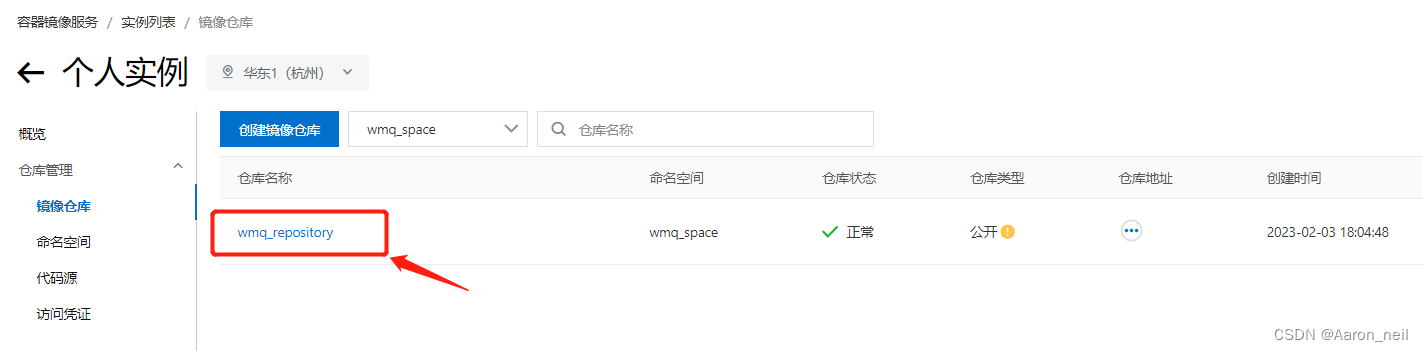

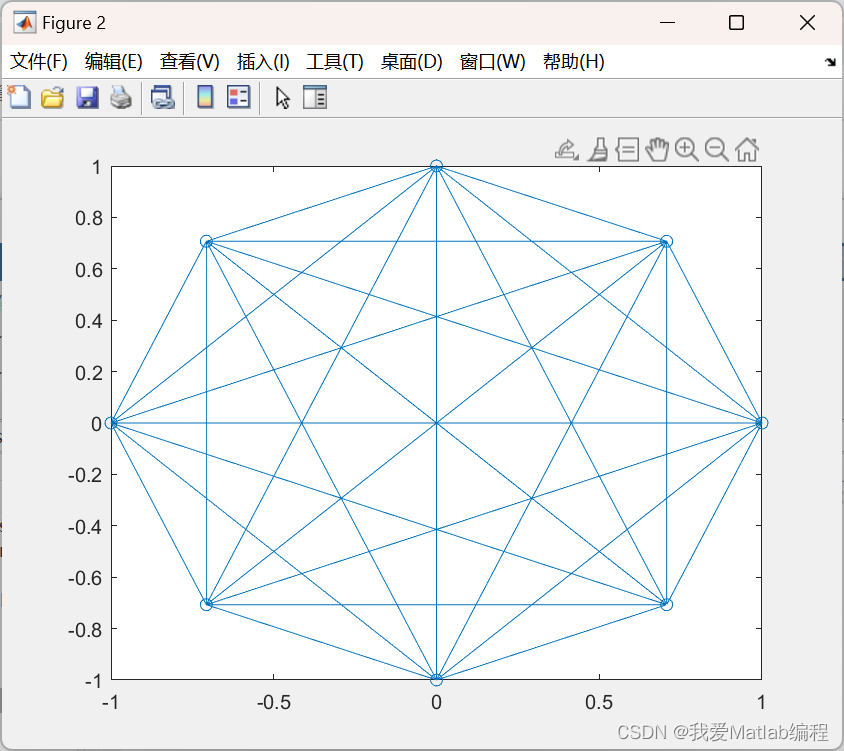

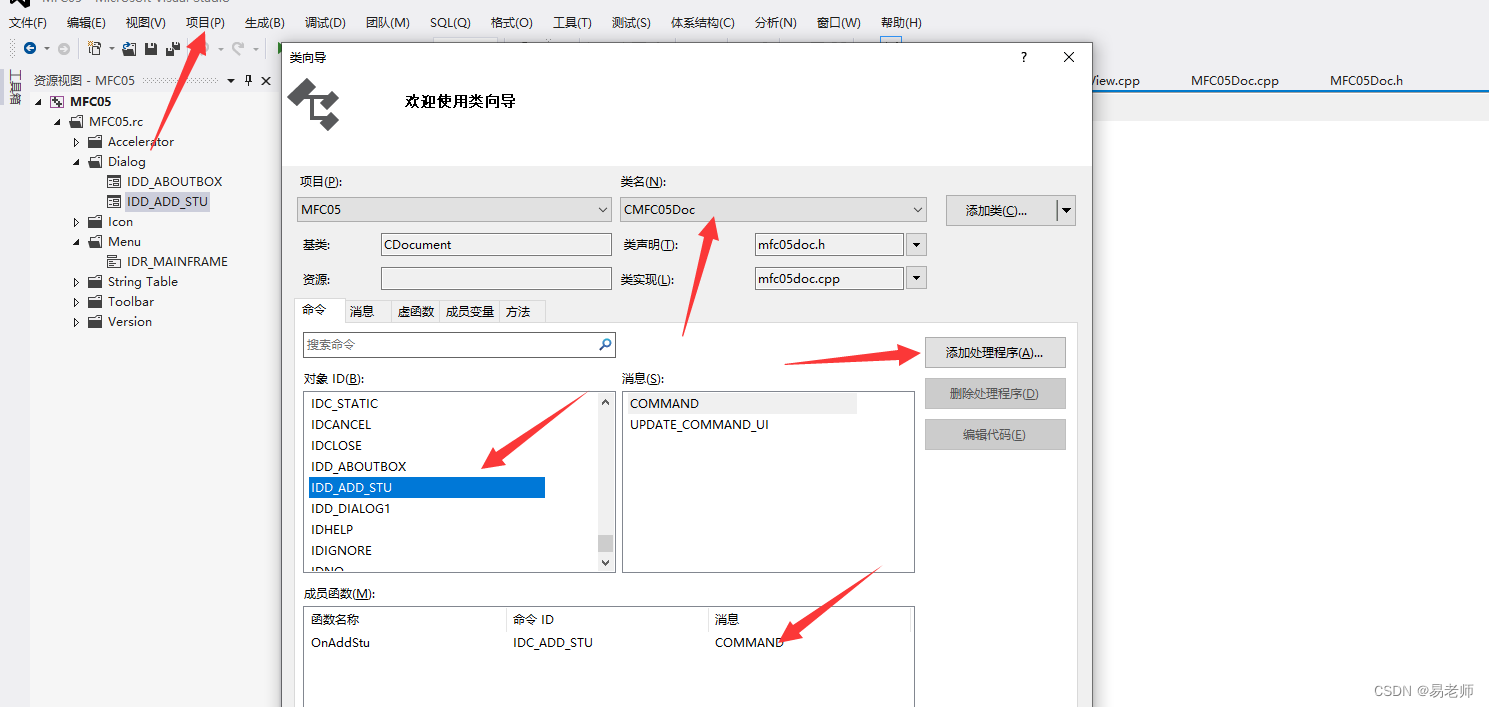

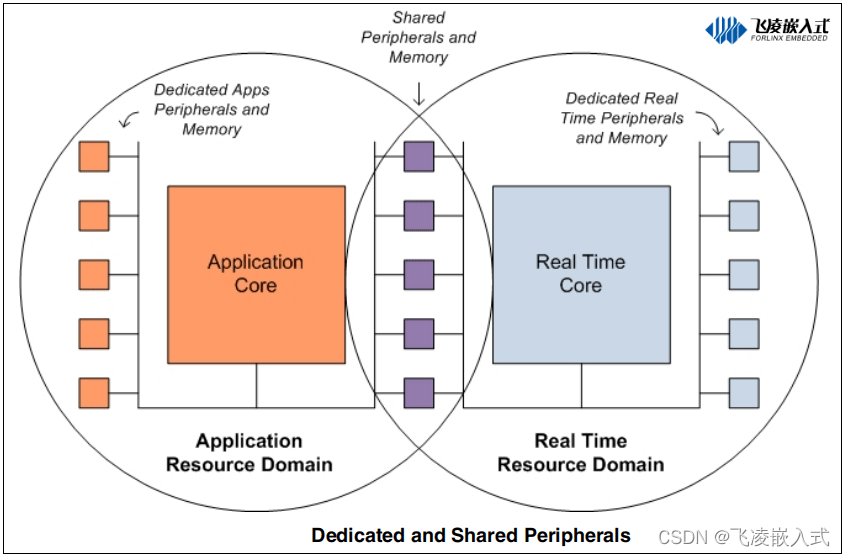

以NXP i.MX8M Plus处理器的A核和M核为例,其实只有少部分外设被指定了属于哪个核,而大部分的外设都能被A核和M核同时使用。如下图所示:

这里我们通过飞凌嵌入式OKMX8MP-C开发板上的UART3进行演示,同时编写A核和M核程序控制UART3打印信息,通过UART3将开发板与电脑链接,在电脑串口调试界面可以看到A核和M核同时输出了信息。

A核和M核同时输出信息

那么在实际应用中,当某个外设需要被指定的内核独占或被多核同时使用时,该如何合理安排时序才能避免外设输出异常呢?接下来,小编就以飞凌嵌入式OKMX8MP-C开发板为例,将多核异构处理器对共享外设和资源的调配方法介绍给大家。

飞凌嵌入式OKMX8MP-C开发板所搭载的NXP i.MX8M Plus处理器具备强悍的性能, 集成4个主频最高可达1.8GHz(工业级主频为1.6GHz)的Arm Cortex-A53多任务核和1个Cortex-M7实时核,不管是对数据的高速吞吐、处理,还是复杂的人机交互界面处理,都能从容应对。

01.A核独占外设

这种情况比较简单,在设备树中定义设备节点,编译新的设备树,将生成的OK8MP-C.dtb和Image拷贝至以下目录:

开发板/run/media/mmcblk2p1/

重启开发板,同时M核程序中不初始化UART3即可。以UART3为例:

02. M核独占外设

对于NXP i.MX8M Plus处理器而言,由于A核和M核对内存和外设的访问都是共享且平等的,为了确保不产生资源冲突会通过资源域(resource domains)控制器从硬件层面来对指定内存和外设的访问权限进行保护。

i.MX8M Plus处理器允许定义最多4个资源域并将不同的内存和外设资源指定到这些资源域中。默认情况下,A核和相关外设被指定于域0;当M核程序运行后,M核以及相关外设最初也是域0,但马上被重新指定于域1。

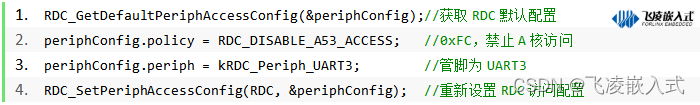

因此若一个外设需要被M7内核单独使用,首先要修改A核设备树,删除外设节点;其次在M核程序中将域0改为域1;最后再将外设初始化,这样就可以单独控制了。域转换代码如下:

03.多核共享外设

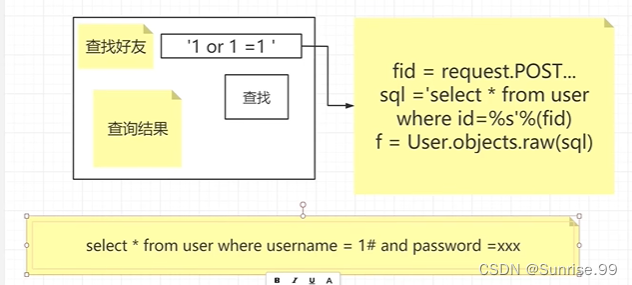

如果多核想共享某个外设,但在某段时间又需要独占,后续再释放;或者多核的开发人员不是同一人,为了避免出错,在自己的程序中强制独占某个核,是否可以实现呢?

答案是肯定的——使用RDC功能即可。RDC全程为Resource Domain Controller,即资源域控制器,可以通过寄存器和信号量两种方式实现某个域对外设的独占和释放。

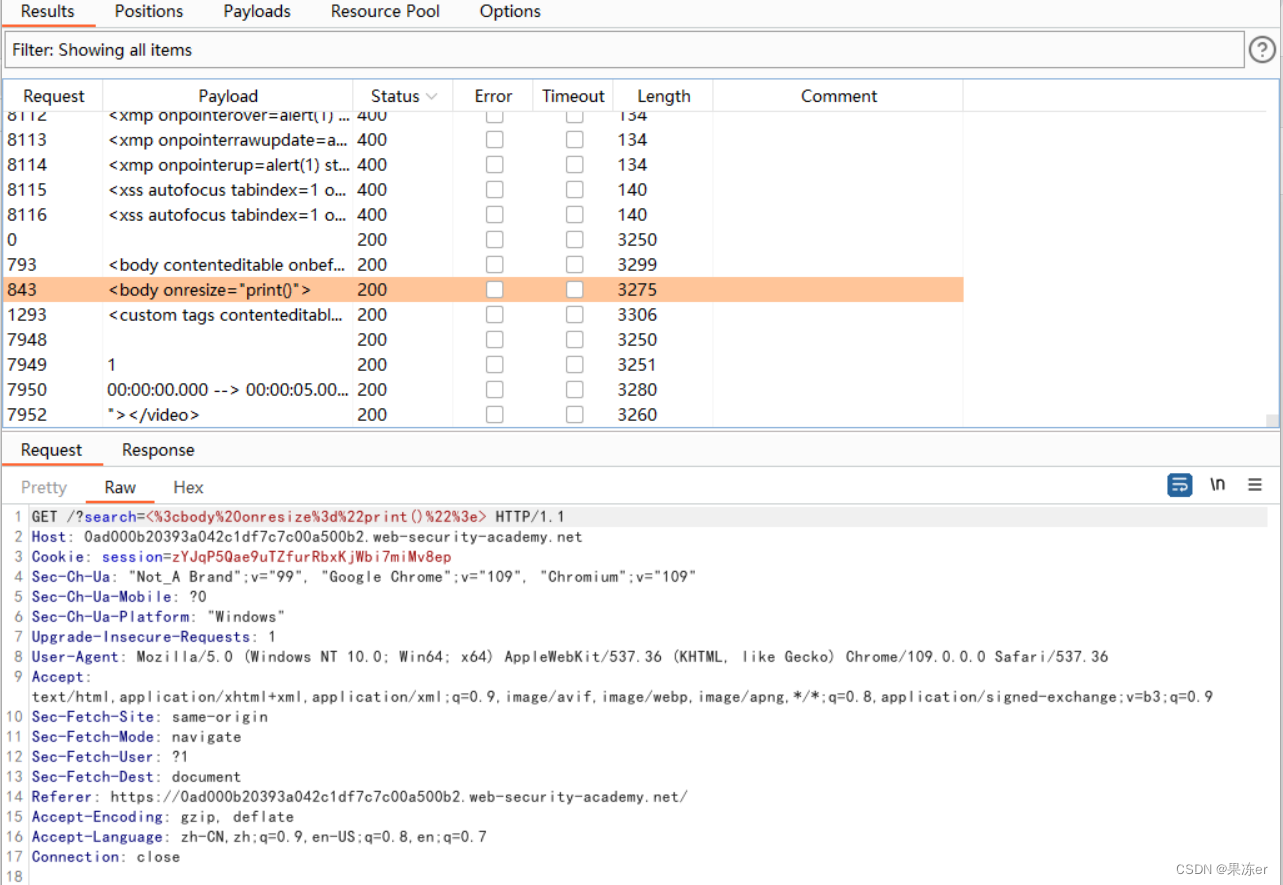

(1)寄存器RDC_PDAPn

由于i.MX8M Plus处理器最多支持4个域,因此对寄存器后8比特位写入不同数值,将允许相应的域对某个管脚和内存的读写使能,如禁止A核域0读写某个管脚,则设置寄存器为0xFC即可,后两个比特位为0,表示禁止域0读写此外设;其他六个比特位为1,表示允许从域1到域3读写此外设。

每个共享外设在RDC资源表中均有一个序号,用于区别其他外设,如UART3在RDC中定义如下:kRDC_Periph_UART3 = 104U, /**< UART3 RDC Peripheral */

在M核程序中可如下修改程序,实现M核独占UART3的目的。

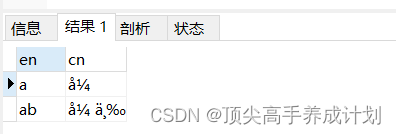

修改程序验证,此时只有M核控制UART3打印信息。

仅M核输出信息

注意:

因为在设备树中没有删除UART3,所以在A核启动内核解析设备树生成设备文件时,需对UART3操作。因M核程序中禁止A核的访问UART3,此时内核将无法正常启动。可以加10秒延时等待内核启动完成,也可在A核启动后,通过双核通信告知M核启动RDC外设独占。

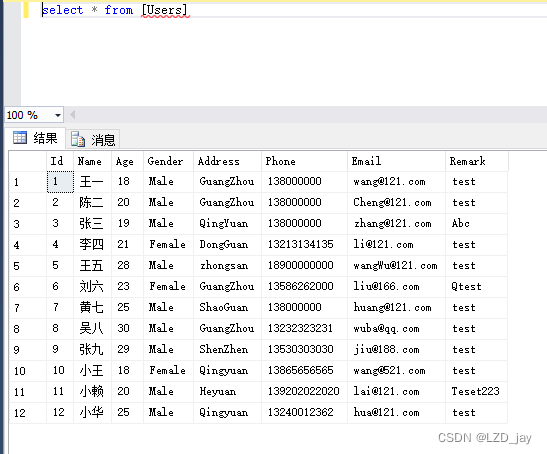

(2)信号量RDCSEMA42

RDC SEMA42是一个专门配合RDC功能的信号量,当某个域获取某个外设的SEMA42锁后,其他的域将无法访问此外设,只能等待域释放该外设锁,才能再访问。

RDC SEMA42数据锁的开启配置如下:

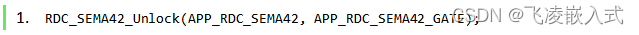

M核对UART3上锁,获取管脚的使用权:

M核释放UART3的RDC SEMA42锁,放弃管脚的使用权:

修改程序后验证,发现和RDC寄存器一样,M核上锁后获取UART3使用权,仅可独自发送,A核访问UART3会出错。释放SEMA42锁后,A核和M核就均能访问UART3了。

以上就是小编基于OKMX8MP-C开发板为大家带来的多核异构处理器对外设和内存资源的使用方法,各位工程师小伙伴可以根据自己的需求灵活设置策略,以满足不同场景的需要。