简介

The AMD LogiCORE™IP Aurora 64B/66B core是一种可扩展的轻量级高数据速率链路层协议,用于高速串行通信。该协议是开放的,可以使用AMD设备技术实现。

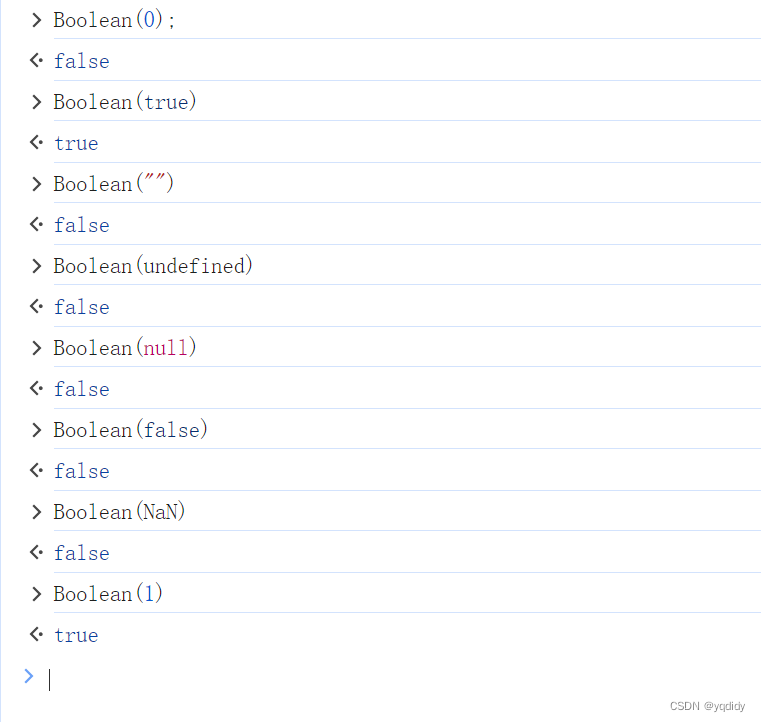

Aurora 64B/66B是一种轻量级的串行通信协议,适用于多千兆位链路 (如下图所示)。它用于使用一个或多个GTX、GTH或GTY收发器在设备之间传输数据。连接可以是全双工 (两个方向的数据) 或单工 (任一方向的数据)。

Aurora 64B/66B信道概览

Aurora 64B/66B内核在连接到Aurora64B/66B渠道合作伙伴时会自动初始化渠道。初始化后,应用程序可以通过通道传递数据作为帧或数据流。Aurora 64B/66B框架可以是任何尺寸。高优先级请求能够在任何时间中断这些帧。有效数据字节之间的间隙会自动填充闲置,以保持锁定并防止过多的电磁干扰。流控制在Aurora 64B/66B中是可选的,可用于限制linkpartner的传输数据速率,或通过通道发送简短的高优先级消息。流在Aurora 64B/66B中实现为单个无休止的帧。每当数据未被发送时,发送闲置以保持链路存活。过多的位错误、断开连接或设备故障会导致内核重置并尝试初始化新通道。Aurora 64B/66B核心可以支持多通道信道的接收中的最多两个符号偏斜。Aurora 64B/66B协议使用64B/66B编码。与8B的25% 开销相比,64B/66bencoding具有非常低 (3%) 的传输开销,因此理论上可以提高性能。

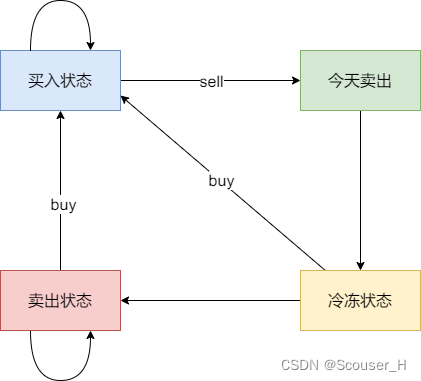

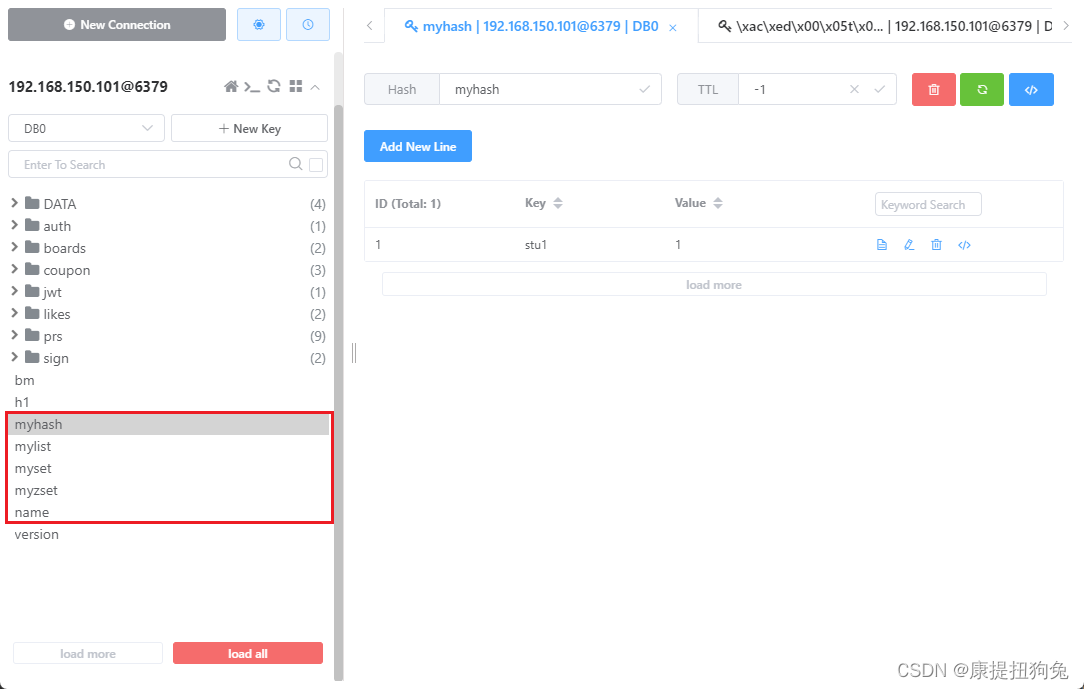

Aurora 64B/66B核心框图

通道逻辑: 通道逻辑模块的实例驱动每个GT收发器。该通道逻辑初始化每个单独的收发器,处理控制字符的编码和解码,并执行错误检测

通道逻辑: 通道逻辑模块的实例驱动每个GT收发器。该通道逻辑初始化每个单独的收发器,处理控制字符的编码和解码,并执行错误检测。

全局逻辑: 内核中的全局逻辑模块执行用于通道初始化的通道绑定。在操作期间,通道跟踪由Aurora 64B/66B协议定义的未就绪空闲特性,并监视所有通道逻辑模块的错误。

RX用户界面: AXI4-Stream接收 (RX) 用户界面将数据从通道移动到应用程序,并执行流量控制功能。

TX用户界面: AXI4-Stream传输 (TX) 用户界面将数据从应用程序移动到信道,并执行流量控制TX功能。标准时钟补偿模块嵌入在核心内部。该模块控制时钟补偿 (CC) 的周期性传输。

核操作的最大频率取决于支持的线路速率和设备的速度等级。

吞吐量:Aurora 64B/66B核心吞吐量取决于收发器的数量、收发器类型和所选收发器的目标线路速率。对于GTH收发器,吞吐量分别从单通道设计到16通道设计的0.48 Gbps到254.06 Gbps不等。note:为了在使用VIVADO的默认合成策略时获得更好的定时性能,请将线路速率从IP/收发器支持的最大线路速率降低约30%。当启用CRC_MODE时,将线路速率降低50%。使用另一种合适的合成策略,用户可以实现IP中支持的最大线路速率。