verilog语言中,针对逻辑门,有许多内置可直接使用的逻辑门,从输入输出数量可分为多输入门和多输出门。

一、多输入门

有单个或多个输入,只有单个输出的逻辑门,包含and(与),or(或),xor(异或),nand(与非),nor(或非),xnor(同或/异或非)门等。

二、多输出门

有单个或多个输出,只有单个输入的逻辑门,多输出门的作用主要是用于缓冲作用。此处定义可看出与多输入门存在重叠,未方便记忆,可记住只有以下两种:buf,not(非)

三、特殊门

3.1 三态门

三态门:三态门可理解为带有控制端的缓冲门,只有在控制信号有效时,数据才能传递,否则输出为高阻态z。

三态门端口分为一个输入端口,一个输出端口,一个控制端口。

类型:bufif0、bufif1、notif0、notif1,bufif0/notif0在控制信号为1时,输出为z,为0时数据输出,bufif1/notif1在控制信号为0时,输出为z,为1时数据输出,

格式:如bufif0 test(out,in,control)

3.2 上拉/下拉电阻

只有输出没有输入,上拉电阻pullin将输出固定为1,下拉电阻pulldown将输出固定为0

格式:pullin pull_in(out1)

3.3 MOS 开关

包含cmos、pmos、nmos、rcmos、rpmos、rnmos

输入输出端口:与三态门类似,第一个端口为输出,第二个端口为输入,第三个为控制端口

nmos和rnmos开关在控制信号为0,pmos和rpmos开关在控制信号为1时,输出为z

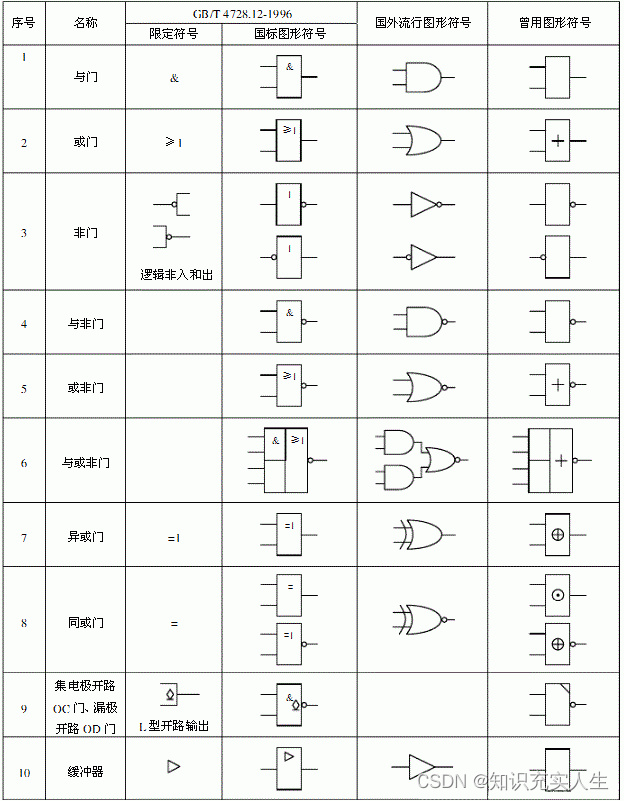

四、逻辑门图形符号

各种逻辑门的图像符号如下图,注:图片来源百度图片