文章目录

- X-BAR

- 9.1 输入X-BAR

- 9.2 ePWM、CLB和GPIO输出X-BAR

- 9.2.1 ePWM X-BAR

- 9.2.1.1 ePWM X-BAR架构

- 9.2.2 CLB X-BAR

- 9.2.2.1 CLB X-BAR架构

- 9.2.3 GPIO输出X-BAR

- 9.2.3.1 GPIO输出X-BAR架构

- 9.2.4 X-BAR标志

- 总结

X-BAR

交叉开关(在本章中称为X-BAR)提供了以各种配置连接设备输入、输出和内部资源的灵活性。

该设备共包含四个X-BAR:

- 输入X-BAR

- 输出X-BAR

- CLB X-BAR

- ePWM X-BAR

每个X-BAR根据X-BAR接收信号的位置命名。例如,输入X-BAR将外部信号“输入”到设备。输出X-BAR将设备的内部信号“输出”到GPIO。CLB X-BAR和ePWM X-BAR分别向CLB和ePWM模块发送信号。

一句话讲,X-BAR就是能够讲外部信号送到内部外设作为一个信号如封锁ePWM;将外部信号送到外部,GPIOx的输入电平在GPIOy上反映,这种用途感觉不多;将内部外设信号送到外部;如ePWM的同步信号输出到GPIOx以供调试。

9.1 输入X-BAR

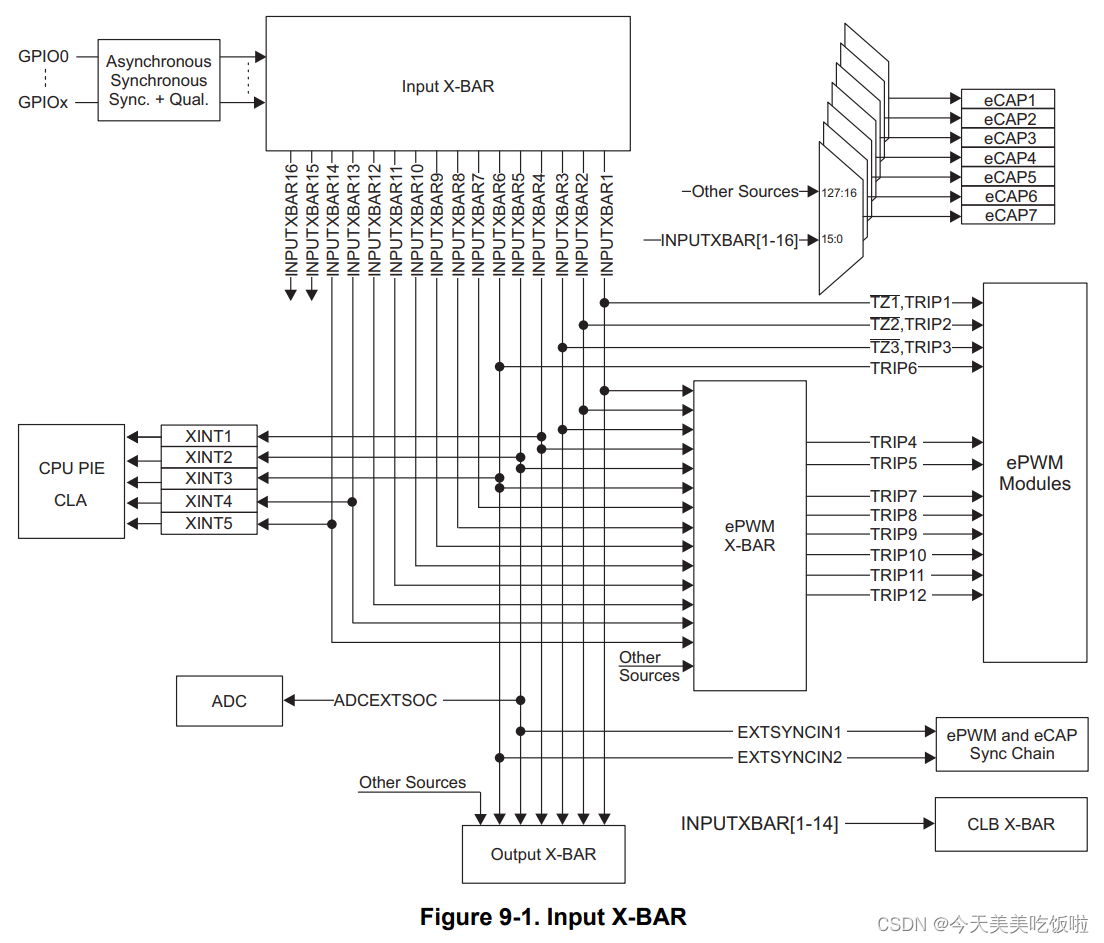

在该设备上,输入X-BAR用于将信号从GPIO路由到许多不同的IP块,如ADC、eCAP、ePWM和外部中断。输入X-BAR可以访问每个GPIO,并可以将每个信号路由到前面提到的任何(或多个)IP块。AIO的数字输入也可在输入X-BAR上使用。这种灵活性通过只需要任何GPIO引脚可用就可以减轻外围复用的一些限制。注意,**GPIO多路复用器上选择的功能不会影响输入X-BAR。**输入X-BAR简单地将输入缓冲器上的信号连接到所选目的地。因此,您可以执行诸如将一个外设的输出路由到另一个外设(即,使用eCAP测量ePWM的输出以进行频率测试)之类的操作。

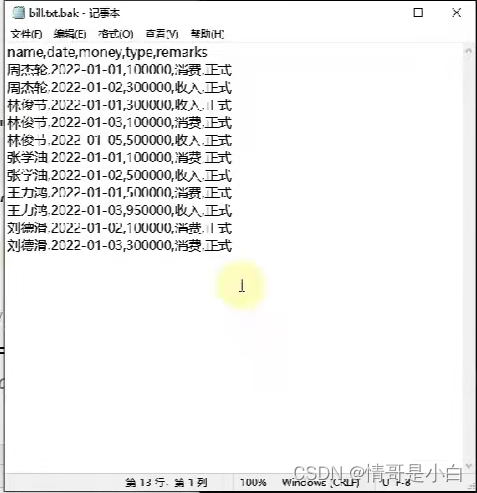

通过INPUTxSELECT寄存器配置输入X-BAR。每个INPUTx的可用IP目的地如图9-1和表9-1所示。有关配置的更多信息,请参阅XBAR寄存器部分中的INPUT_XBAR_REGS寄存器定义。

注:使用XBAR路由到CLB的信号必须在CLB自身内同步。

9.2 ePWM、CLB和GPIO输出X-BAR

9.2.1 ePWM X-BAR

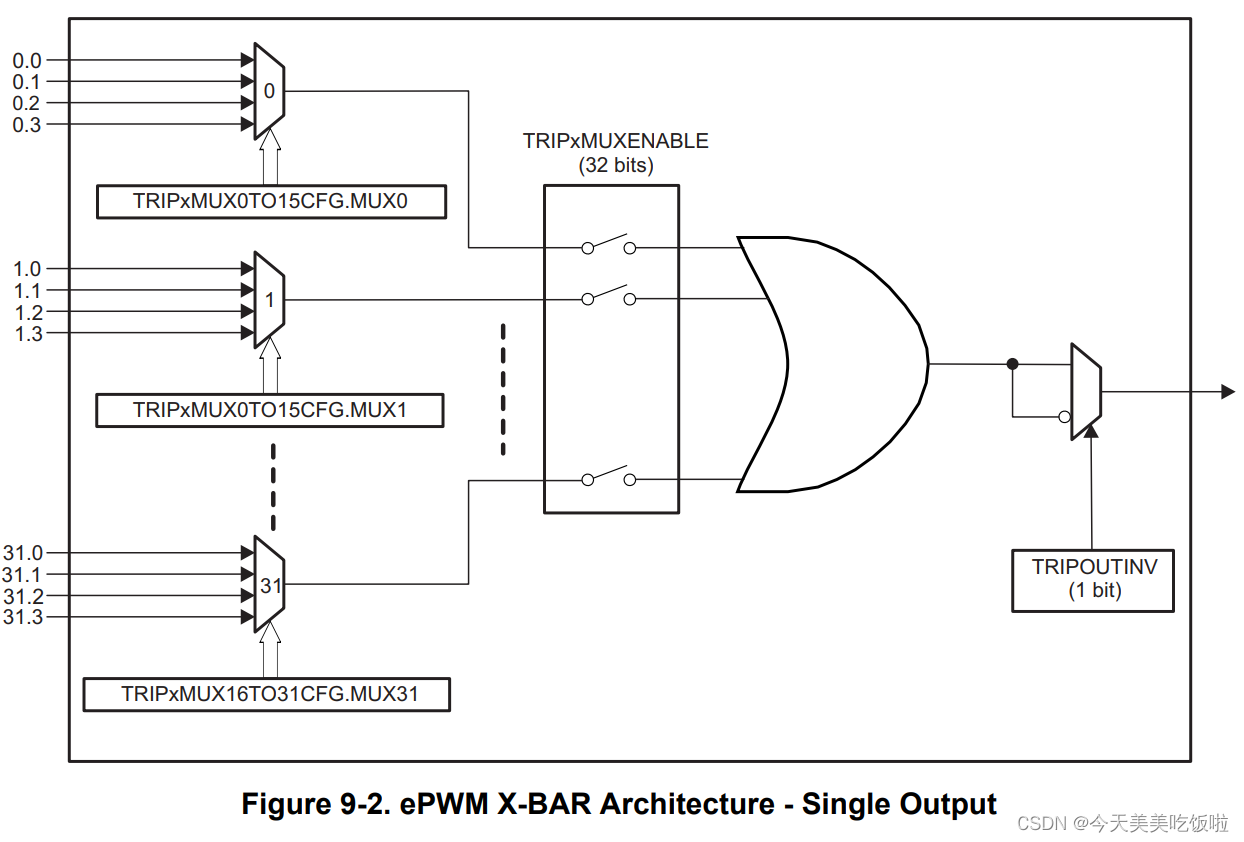

ePWM X-BAR向ePWM模块提供信号。具体而言,ePWM X-BAR连接到每个ePWM模块的数字比较(DC)子模块,以执行诸如跳闸区和同步等操作。请参阅增强型脉宽调制器(ePWM)一章,了解有关DC子模块的其他使用方式的更多信息。图9-2显示了ePWM X-BAR的架构。注意,ePWM X-BAR的架构与GPIO输出X-BAR架构相同(输出锁存器除外)。

9.2.1.1 ePWM X-BAR架构

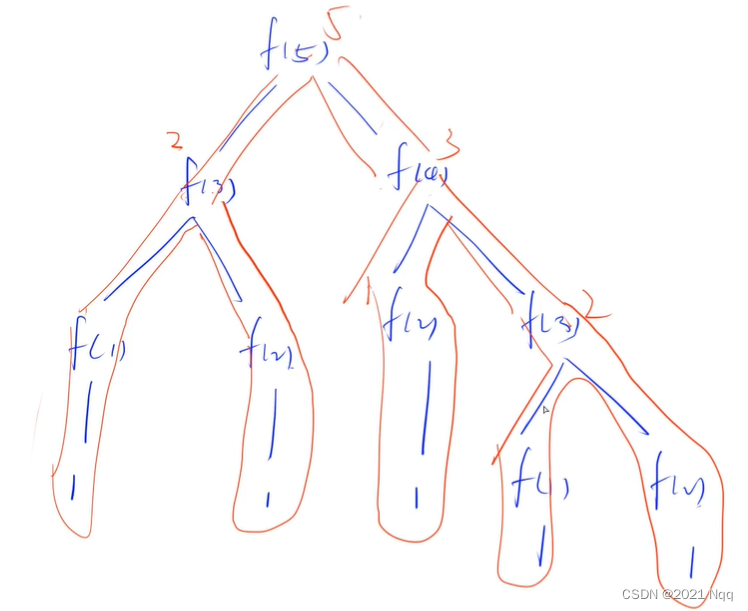

ePWM X-BAR具有八个输出,这些输出被路由到每个ePWM模块。图9-2表示单个输出的架构,但该输出与所有其他输出的架构相同。

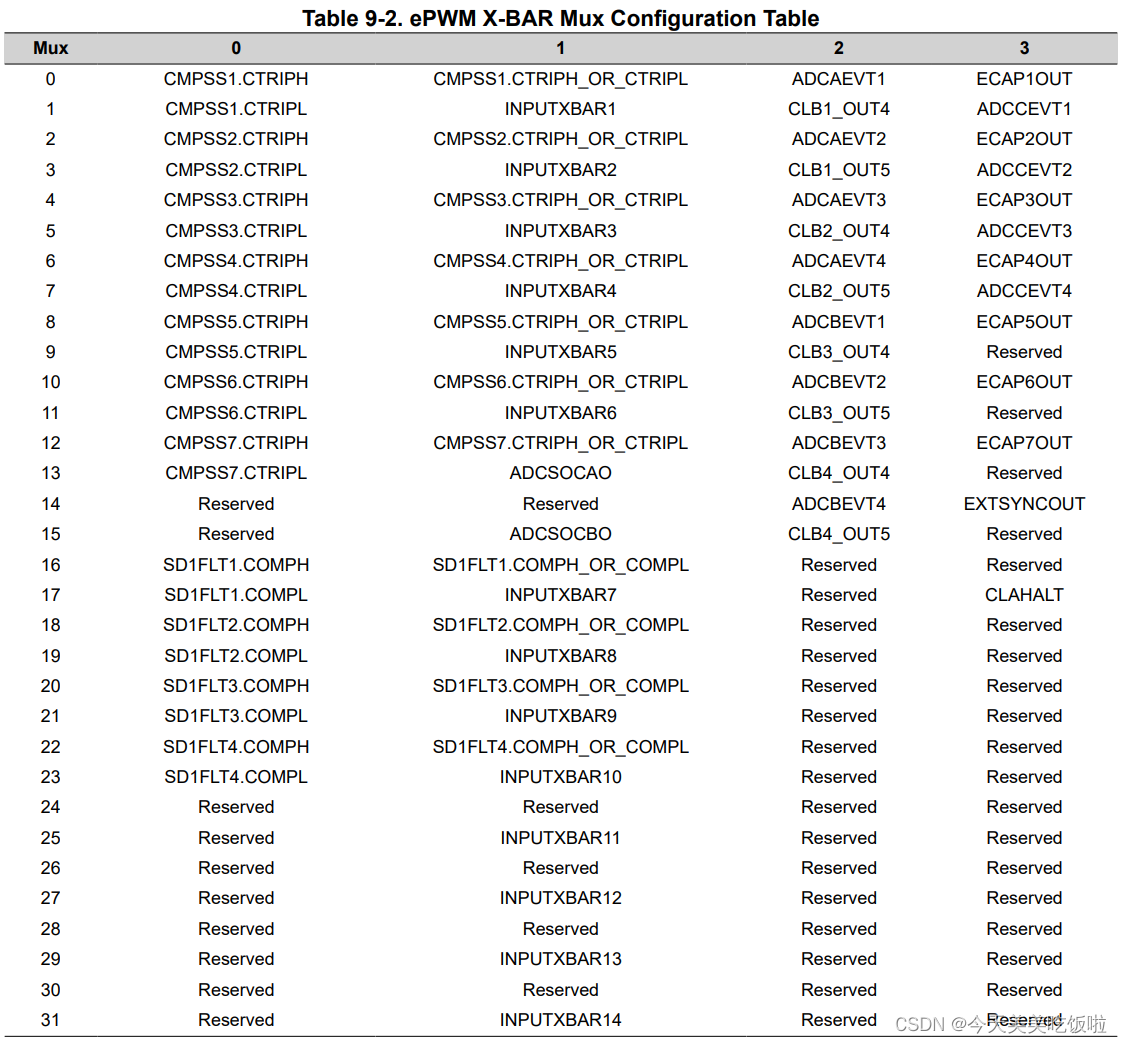

首先,通过参考表9-2确定可以传递到ePWM的信号。对于每个TRIPx输出,每个多路复用器最多选择一个信号(总共32个多路复用器)。使用TRIPxMUX0TO15CFG和TRIPxMUX 16TO31CFG寄存器选择每个多路复用器的输入。要将任何信号传递到ePWM,请启用TRIPxMUX可执行寄存器中的多路复用器。所有被启用的多路复用器在被传递到ePWM上的相应TRIPx信号之前被逻辑“或”。要可选地反转信号,请使用TRIPOU

TINV寄存器。

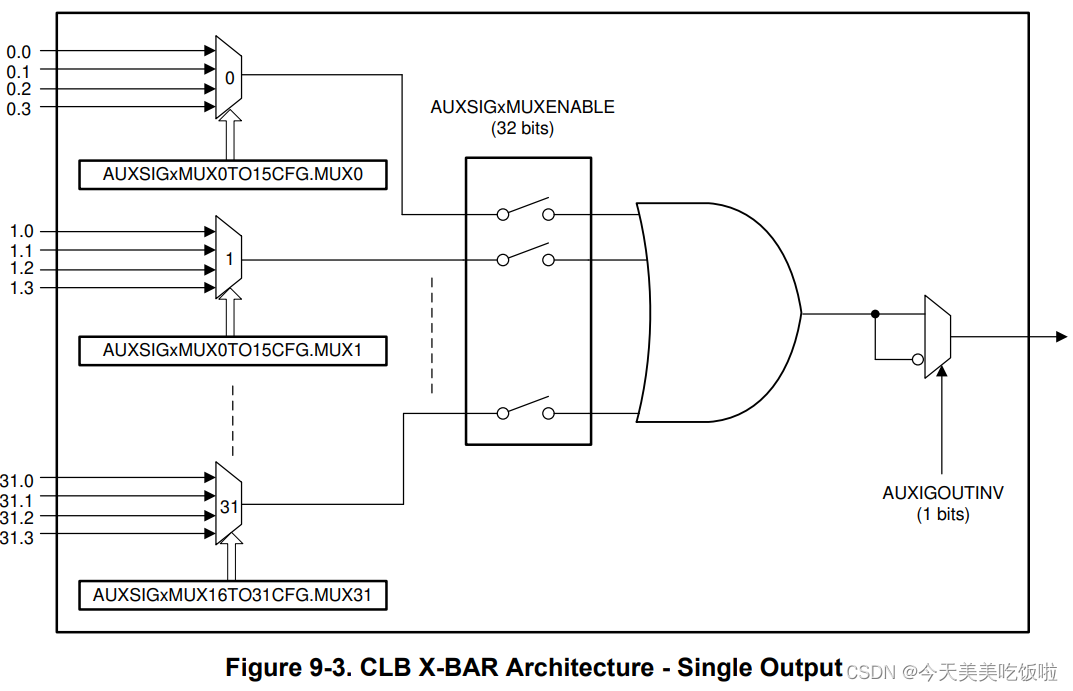

9.2.2 CLB X-BAR

CLB X-BAR为CLB模块提供信号。图9-3显示了CLB X-BAR的架构。注意,CLB X-BAR的架构与GPIO输出X-BAR(输出锁存器除外)的架构相同。

9.2.2.1 CLB X-BAR架构

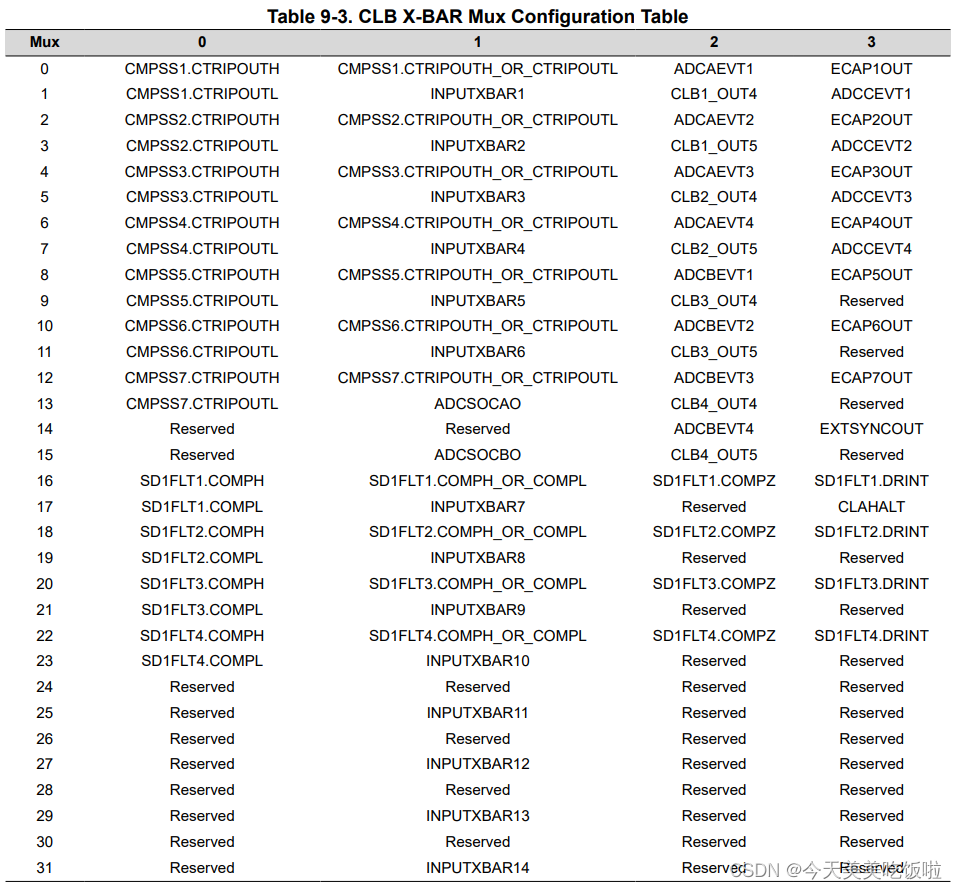

CLB X-BAR有八个输出,这些输出被路由到每个CLB模块。图9-3表示单个输出的架构,但输出与所有其他输出的架构相同。

首先,通过参考表9-3确定可以传递给CLB的信号。为每个AUXSIGx输出选择每个多路复用器最多一个信号(总共31个多路复用器)。使用AUXSIG MUX0TO15CFG和AUXSIG MUX16TO31CFG寄存器选择每个多路复用器的输入。要将任何信号传递到CLB,请启用AUXSIGxMUX寄存器中的多路复用器。所有被启用的多路复用器在被传递到CLB上的相应AUXSIGx信号之前被逻辑“或”。要可选地反转信号,请使用AUXSIGOUTINV寄存器。

9.2.3 GPIO输出X-BAR

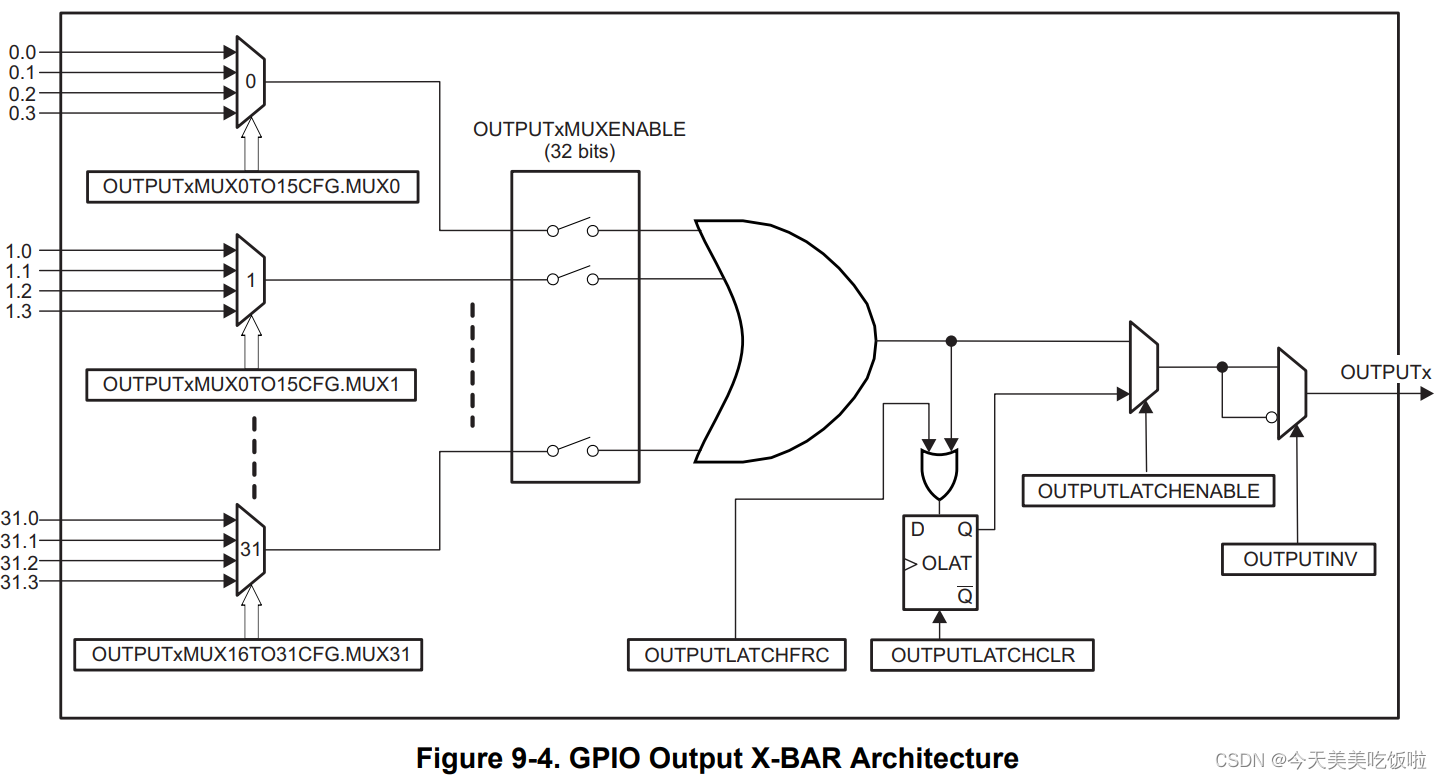

**GPIO输出X-BAR从设备内部接收信号,并将其输出到GPIO。**图9-4显示了GPIO输出X-BAR的架构。X-BAR包含八个输出,每个输出至少包含GPIO多路复用器上的一个位置,表示为OUTPUTXBARx。X-BAR允许选择单个信号或多达32个信号的逻辑或。

9.2.3.1 GPIO输出X-BAR架构

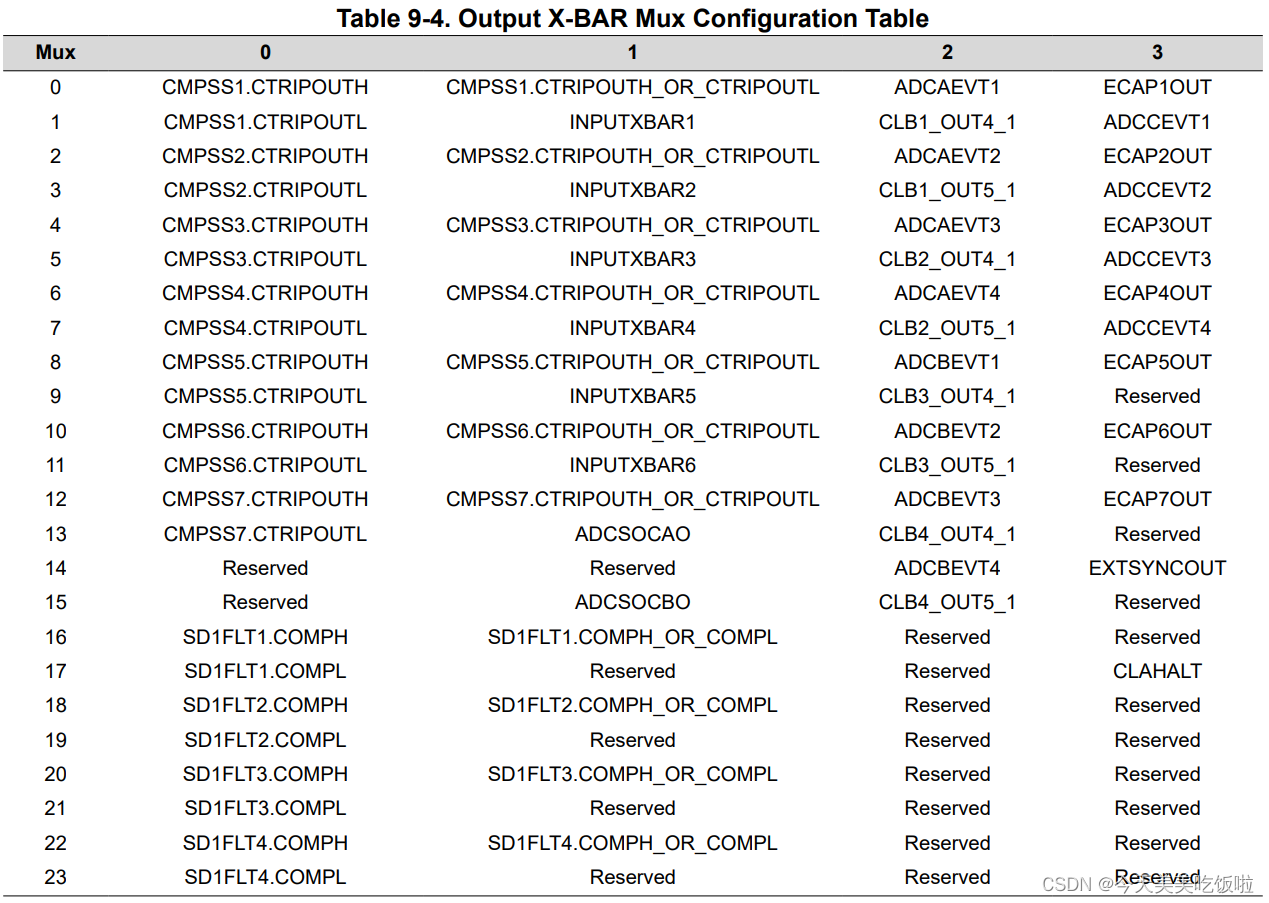

**GPIO输出X-BAR有八个输出,它们被路由到GPIO模块。**图9-4表示单个输出的架构,但该输出与所有其他输出的架构相同。注意,输出X-BAR的架构(输出锁存器除外)与ePWM X-BAR架构相似。

首先,通过参考表9-4确定可以传递到GPIO的信号。对于每个OUTPUTXBARx输出,每个多路复用器最多选择一个信号(总共32个多路复用器)。使用OUTPUTxMUX0TO15CFG和OUTPUTxMUX16TO31CFG寄存器选择每个多路复用器的输入。

要将任何信号传递到GPIO,请启用OUTPUTxMUXENABLE寄存器中的多路复用器。所有被启用的多路复用器在被传递到GPIO模块上的相应OUTPUTx信号之前被逻辑“或”。要可选地反转信号,请使用OUTPUTINV寄存器。如果使用GpioCtrlRegs.GPxMUX和GpioCCtrlRegs.GPSGMUX寄存器选择了正确的OUTPUTx复用选项,则只能在GPIO上识别信号。

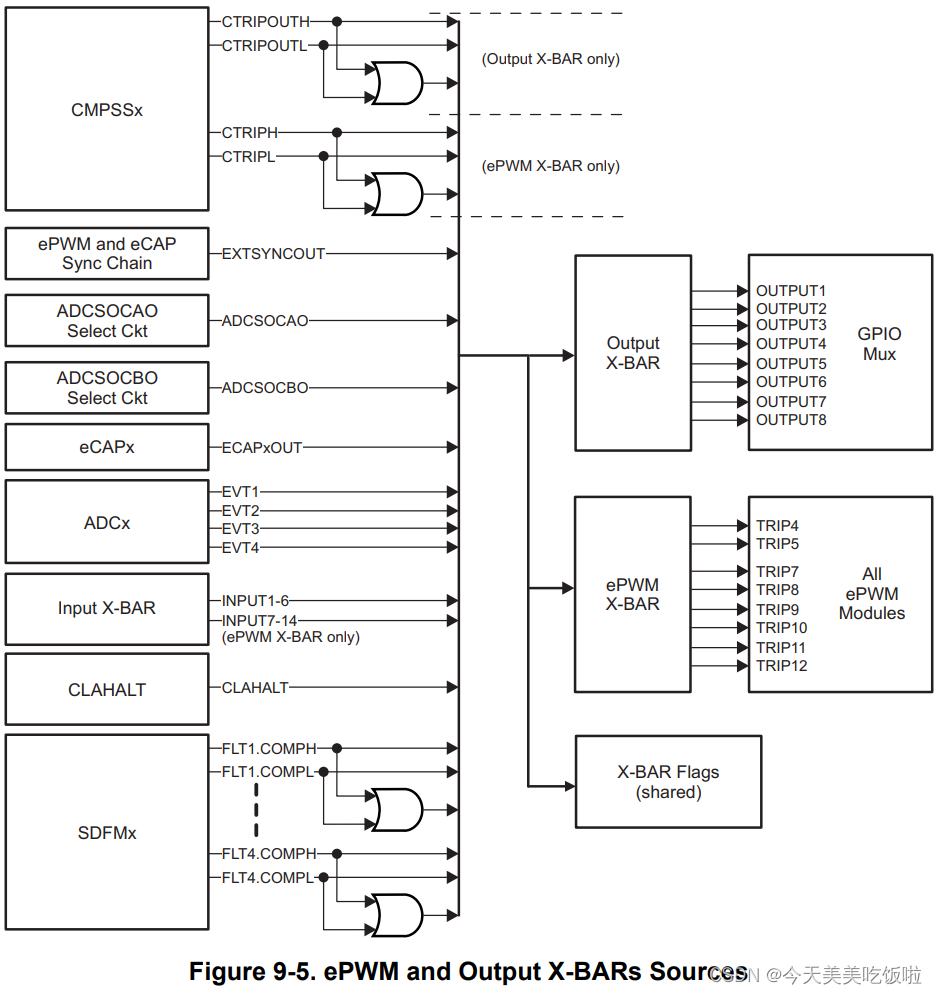

9.2.4 X-BAR标志

除CMPSS信号外,ePWM X-BAR和输出X-BAR具有所有相同的输入信号。由于输入相似,ePWM X-BAR和输出X-BAR利用一组输入标志来指示哪些输入信号已被触发。这允许软件在事件发生时检查输入标志。更多信息请参见图9-5。在一个XBARFLGx寄存器中为

每个输入信号分配一个位。该标志将保持置位状态,直到通过相应的XBARCLRx寄存器清除。

总结

X-BAR不是一个功能模块,只起内部外设与外设之间,或内部外设与GPIO的连接作用。配置X-BAR的就是在配置信号之间的连接。确实如这一节的开头所言,X-BAR提供了以各种配置连接设备输入、输出和内部资源的灵活性。

学完这一节也知道为什么crossbar(X-BAR)的中文翻译是交叉开关。