一、实验目的

1.掌握寄存器堆的工作原理和接口。

2.掌握寄存器堆的实现方法。

3.掌握寄存器堆在微处理器中承担的功能。

二.实验内容

- 设计一32*32bit 的寄存器文件,即32 个 32 位的寄存器文件(寄存器组)

–具备两组读端口及一组写端口;

–通过读端口可从0~31 号的任意地址读取 数据;

–通过写端口可向1~31 号的任意地址写入 数据(0号寄存器的值固定为32’b0); - 利用寄存器堆和ALU 完成平方数f(n),其 中 1<n<16。

- 可选:

1)用fsm三段式实现

2)用7段数码管输出

–数码管的输出不能有明显的闪烁

三.实验程序

alu.v(加法器)

module alu(

input [31:0] a,

input [31:0] b,

input [3:0] op,

output reg[31:0] f,

output c

);

always @(*)

case(op)

4'b0000: f = 32'b0;

4'b0001: f = a + b;

4'b0010: f = a - b;

4'b0011: f = a & b;

4'b0100: f = a | b;

4'b0101: f = a ^ b;

default: f = 32'b0;

endcase

assign c = ~(|f);

endmodule

RegFiles.v(寄存器堆)

module RegFiles(

input clk,

input [4:0] raddr1,

output [31:0] rdata1,

input [4:0] raddr2,

output [31:0] rdata2,

input we,

input [31:0] wdata,

input [4:0] waddr

);

reg[31:0] regs[1:31]; // 寄存器堆,每个寄存器32bit

assign rdata1=(raddr1==5'b00000)?32'b0:regs[raddr1]; // 读端口1

assign rdata2=(raddr2==5'b00000)?32'b0:regs[raddr2]; // 读端口2

always @(posedge clk) // 写端口

if(we)

if(waddr!=5'b00000)

regs[waddr]<=wdata;

endmodule

square.v(求平方数)

module square(

input clk,

input rst,

input [3:0] n,

output [7:0] result

);

wire[31:0] a_w,b_w,f_w; // 两个加数(读端口数据)和结果

wire[31:0] wd; //写端口数据

reg[4:0] wa; // 写端口地址(reg)

reg[4:0] ra1,ra2; // 读端口地址

reg we=1'b0; // 读写控制

reg isf; // 判断加数

reg[3:0] count; // 计数

reg[1:0] cur_state,nex_state; // 现态和次态

assign wd=isf?f_w:n; // 第一个加数恒为n,ifs为0,第二个加数为n,ifs为1,第二个加数为f_w

RegFiles myreg(.clk(clk),.raddr1(ra1),.raddr2(ra2),.rdata1(a_w),.rdata2(b_w),.waddr(wa),.wdata(wd),.we(we));

alu myalu(.a(a_w),.b(b_w),.op(4'b0001),.f(f_w));

// 状态转移

always @(posedge clk)

begin

if(rst)

begin

cur_state<=2'b00;

end

else

cur_state<=nex_state;

end

// 状态转移条件

always @(*)

begin

case(cur_state)

2'b00:

nex_state<=2'b01;

2'b01:

nex_state<=2'b10;

2'b10:

nex_state<=2'b10;

endcase

end

// 状态输出

always @(posedge clk)

begin

case(cur_state)

2'b00:

begin

count<=4'b0010;

isf<=1'b0;

wa<=5'b00001;

we<=1'b1;

end

2'b01:

begin

isf<=1'b0;

ra1<=5'b00001;

ra2<=5'b00010;

wa<=5'b00010;

we<=1'b1;

end

2'b10:

begin

if(count<n)

begin

isf<=1'b1;

count<=count+1;

we<=1'b1;

end

else

begin

we<=1'b0;

end

end

endcase

end

assign result=f_w[7:0];

endmodule

div.v(分频器)

module div(

input clk,

output clk_new

);

reg[17:0] q = 18'b0;

always @(posedge clk)

begin

q=q+1'b1;

end

assign clk_new=q[17];

endmodule

seven.v(七段数码管)

module seven(

input [3:0] data,

output reg[6:0] out

);

always @(*)

case (data)

4'b0000:out = 7'b1111110; // 7e

4'b0001:out = 7'b0110000; // 30

4'b0010:out = 7'b1101101; // 6d

4'b0011:out = 7'b1111001; // 79

4'b0100:out = 7'b0110011; // 33

4'b0101:out = 7'b1011011; // 5b

4'b0110:out = 7'b1011111; // 5f

4'b0111:out = 7'b1110000; // 70

4'b1000:out = 7'b1111111; // 7f

4'b1001:out = 7'b1111011; // 7b

4'b1010:out = 7'b1110111; // 77

4'b1011:out = 7'b0011111; // 1f

4'b1100:out = 7'b1001110; // 4e

4'b1101:out = 7'b0111101; // 3d

4'b1110:out = 7'b1001111; // 4f

4'b1111:out = 7'b1000111; // 47

default:out = 7'b1111110; //7e

endcase

endmodule

show.v(七段数码管显示)

module show(

input clk,

input rst,

input [7:0] result,

output reg[1:0] an,

output [6:0] out

);

wire clk_new;

div mydiv(.clk(clk),.clk_new(clk_new));

reg[3:0] data;

reg[1:0] cur_state,nex_state;

// 状态转移

// always @(posedge clk)

always @(posedge clk_new)

begin

if (rst)

cur_state<=2'b00;

else

cur_state<=nex_state;

end

// 状态转移条件

always @(*)

begin

case(cur_state)

2'b00:

nex_state<=2'b01;

2'b01:

nex_state<=2'b00;

endcase

end

// 状态输出

// always @(posedge clk)

always @(posedge clk_new)

begin

case(cur_state)

2'b00:

begin

an<=2'b01;

data<=result[3:0];

end

2'b01:

begin

an<=2'b10;

data<=result[7:4];

end

endcase

end

seven myseven(.data(data),.out(out));

endmodule

top.v(不用数码管显示)

module top(

input clk,

input rst,

input [3:0] n,

output [7:0] result

);

wire[7:0] result;

square mysquare(.clk(clk),.rst(rst),.n(n),.result(result));

endmodule

top.v(用数码管显示)

module top(

input clk,

input rst,

input [3:0] n,

output [2:0] an,

output [6:0] out

);

wire[31:0] temp;

fib myfib(.clk(clk),.rst(rst),.n(n),.result(temp));

show myshow(.clk(clk),.rst(rst),.result(temp[11:0]),.an(an),.out(out));

endmodule

四、仿真程序

mysim.v(不用数码管显示)

module mysim(

);

reg clk=1'b0;

reg rst=1'b1;

reg[3:0] n=4'b1110;

wire [7:0] result;

always

#10 clk=~clk;

initial

#11 rst=1'b0;

top mytop(.clk(clk),.rst(rst),.n(n),.result(result));

endmodule

mysim.v(用数码管显示)

module mysim(

);

reg clk=1'b0;

reg rst=1'b1;

reg[3:0] n=4'b1110;

wire[2:0] an;

wire[6:0] out;

always

#10 clk=~clk;

initial

#11 rst=1'b0;

top mytop(.clk(clk),.rst(rst),.n(n),.an(an),.out(out));

endmodule

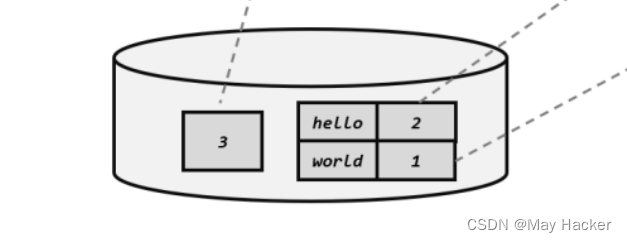

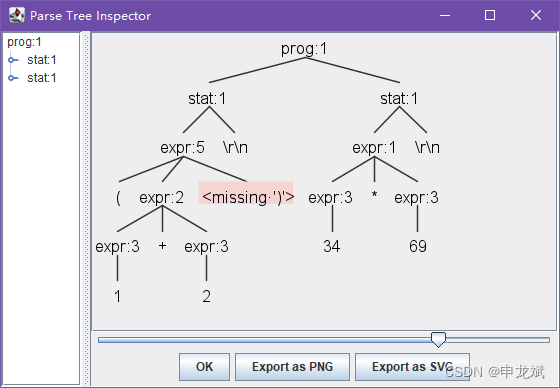

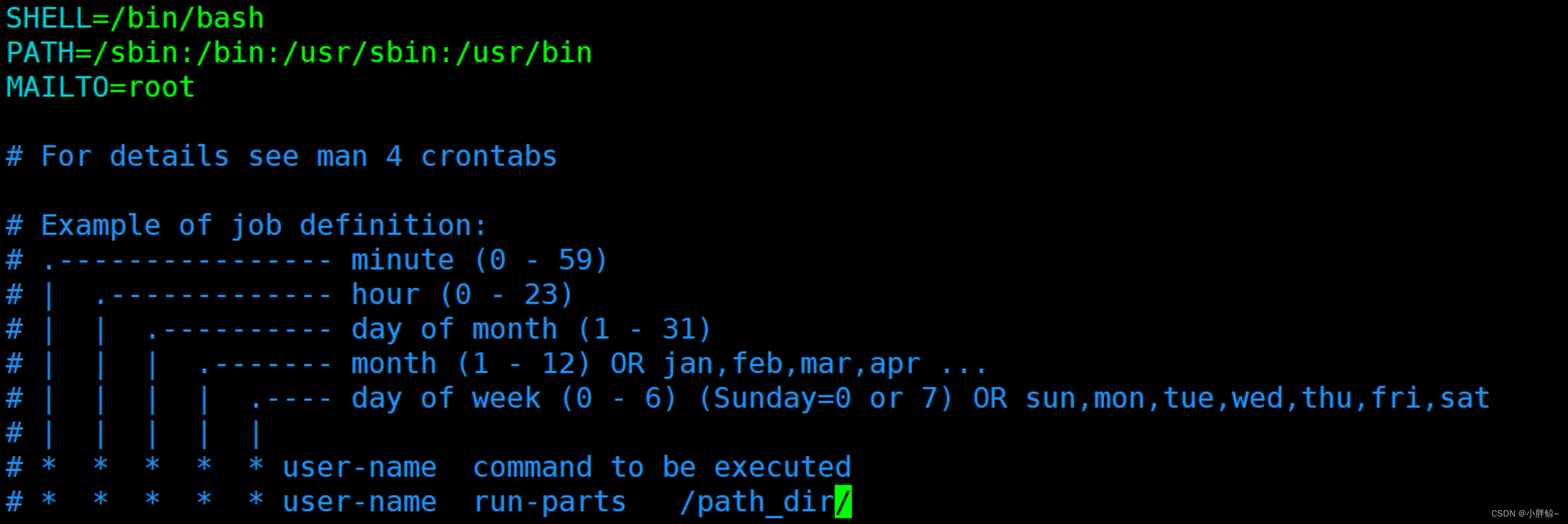

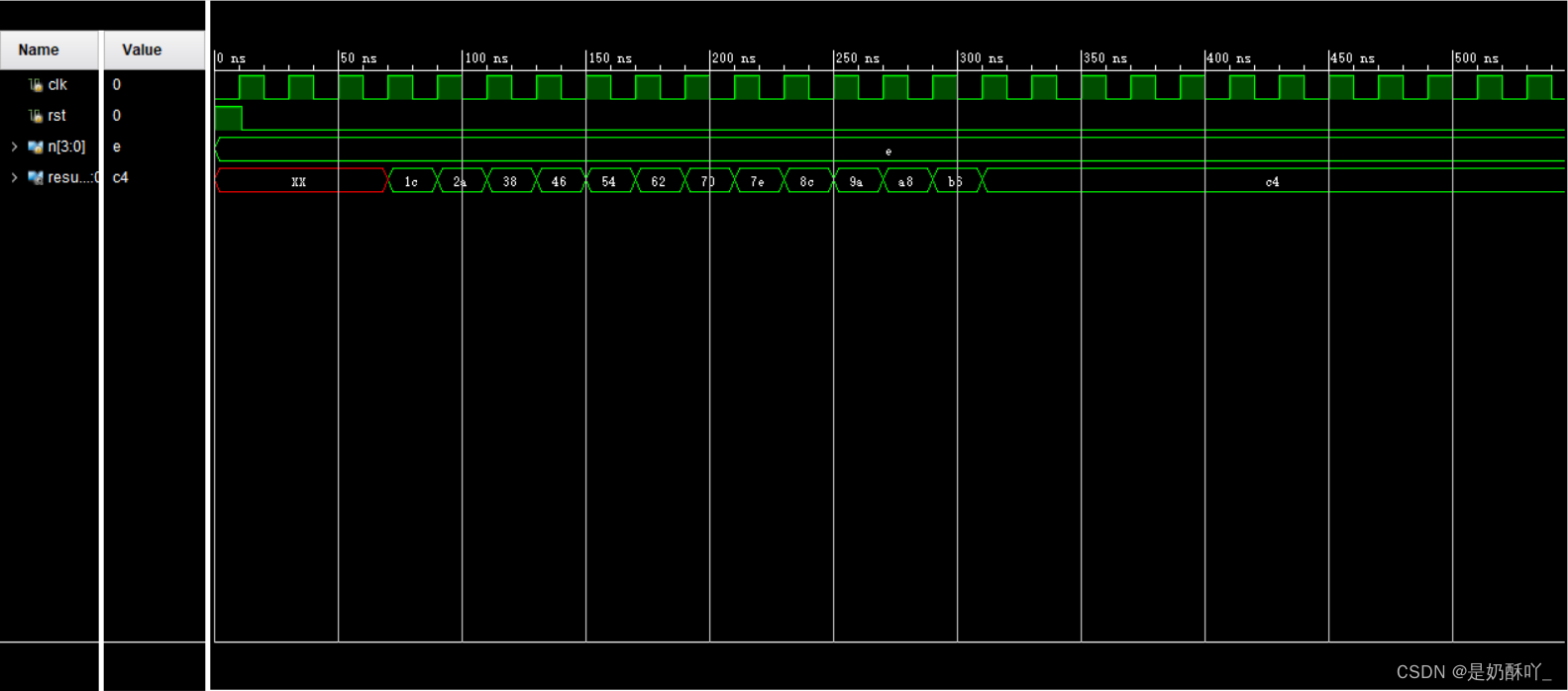

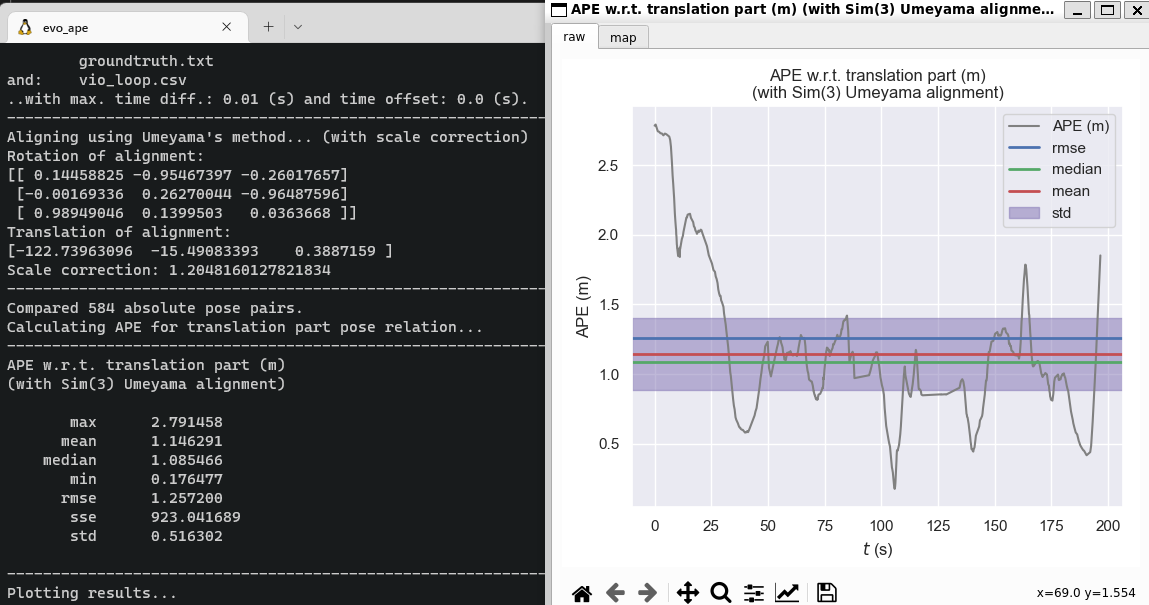

五、仿真结果

不用数码管显示:

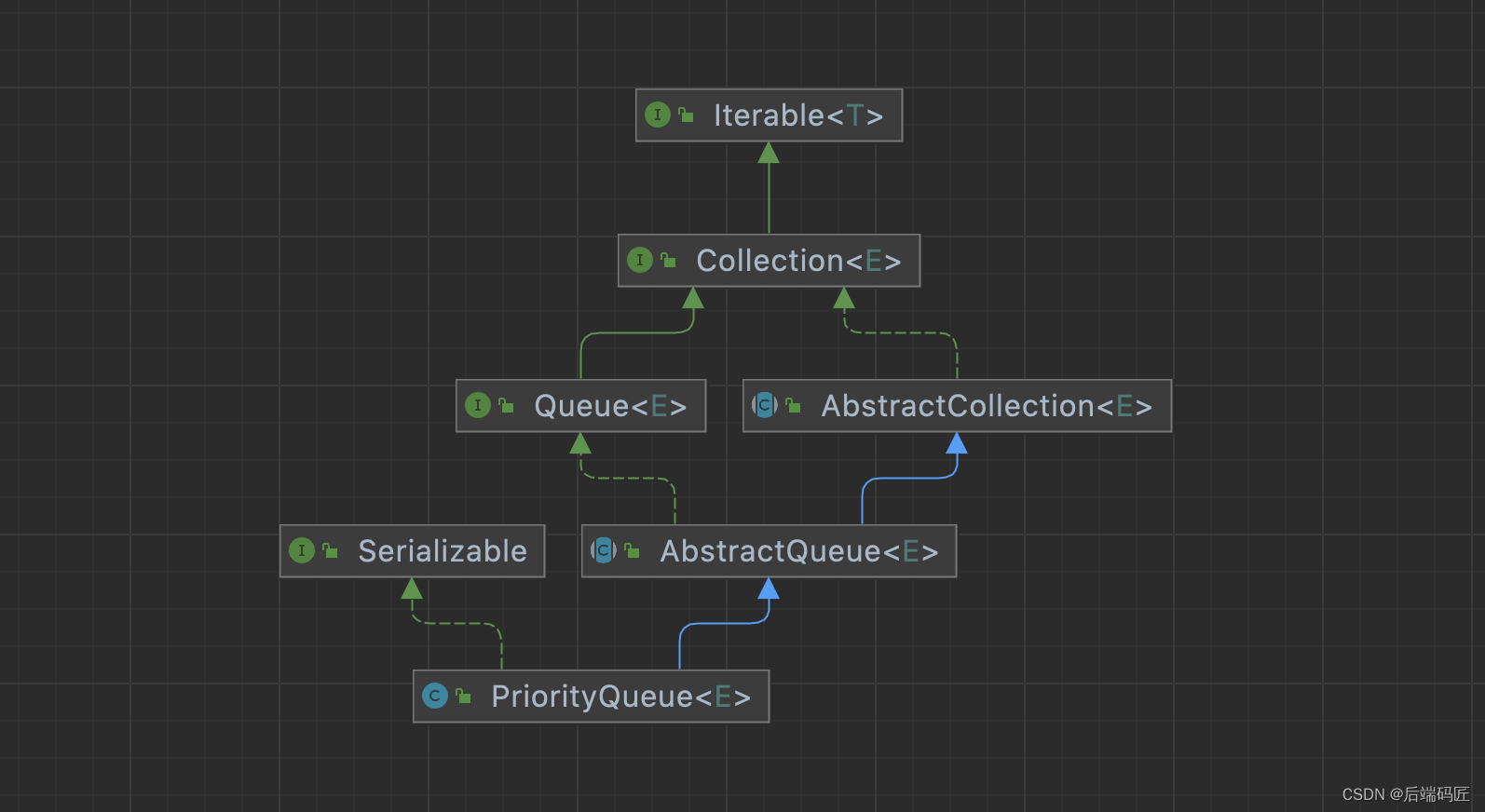

用数码管显示:

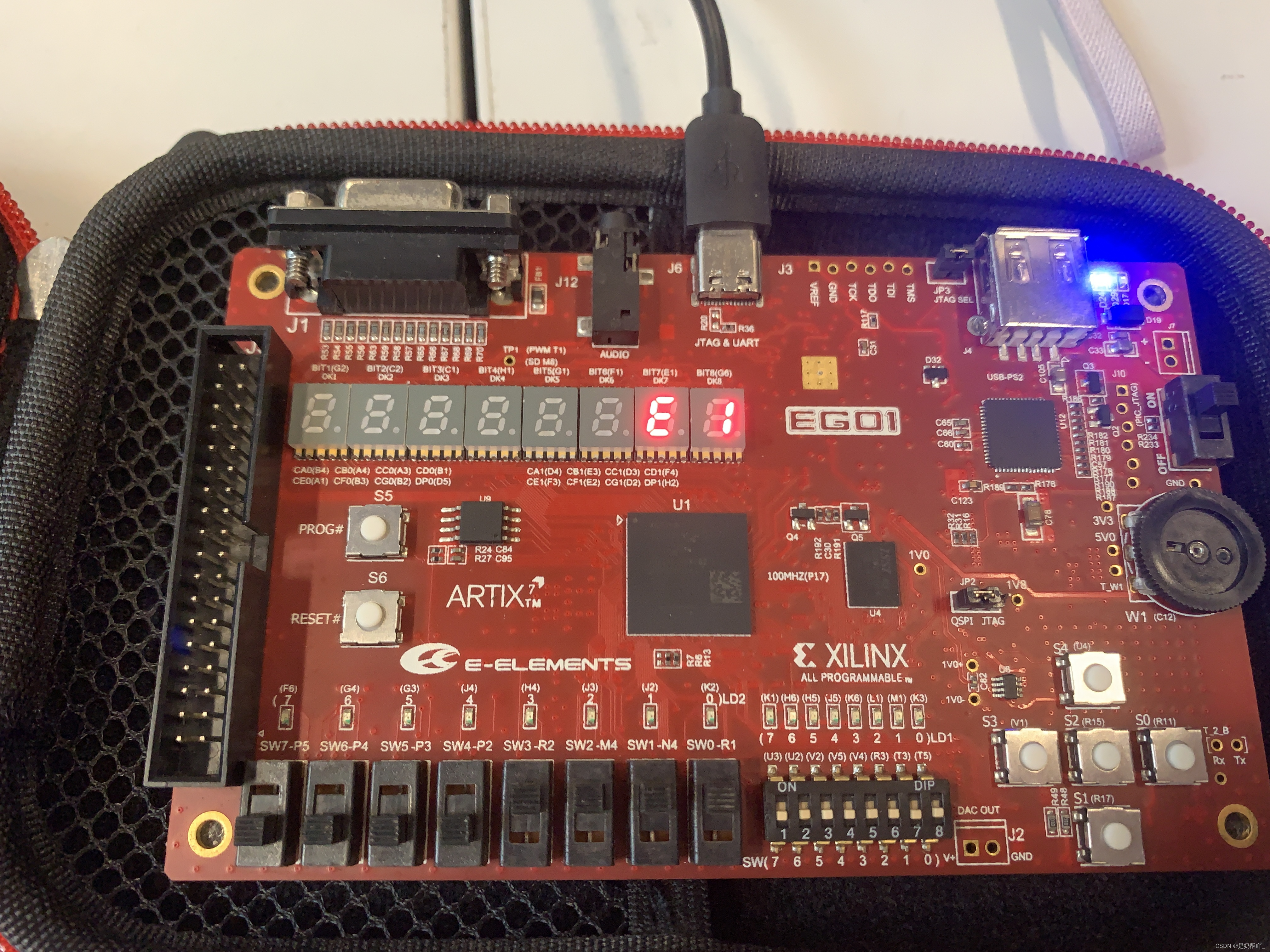

六、实验结果

用数码管显示

![[go学习笔记.第十八章.数据结构] 2.约瑟夫问题,排序,栈,递归,哈希表,二叉树的三种遍历方式](https://img-blog.csdnimg.cn/c059abcbe7cc4f848b6fa547111fab07.png)