萌新的SOC大学习之hello_world

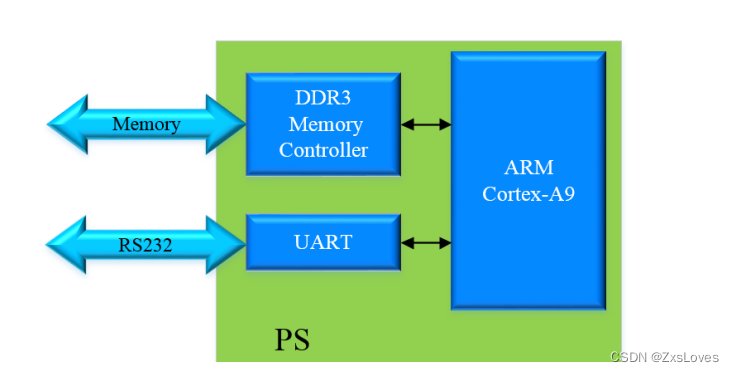

zynq本次hello world 实验需要

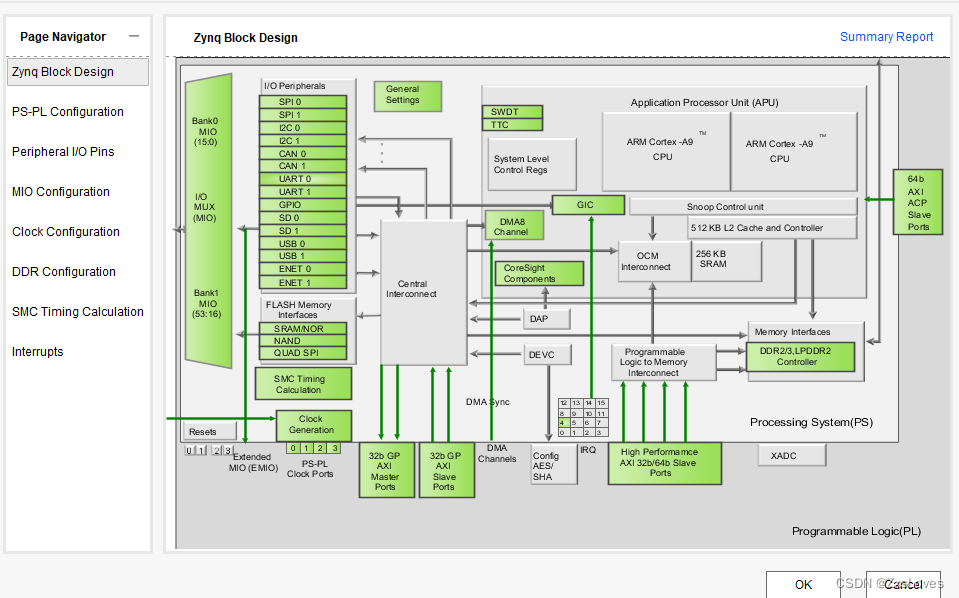

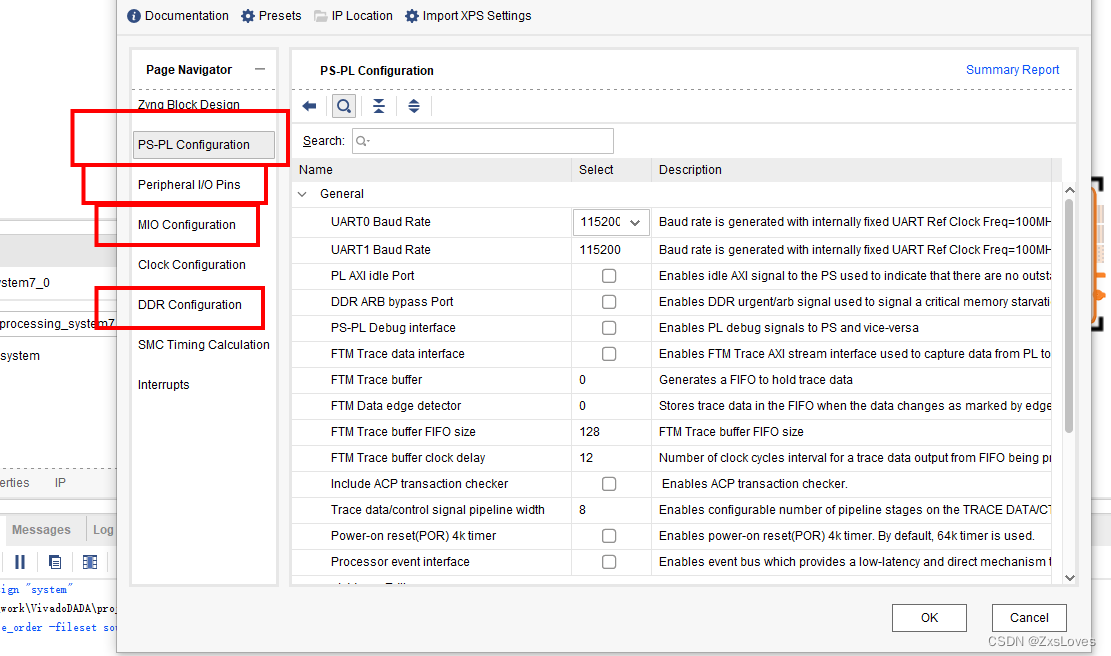

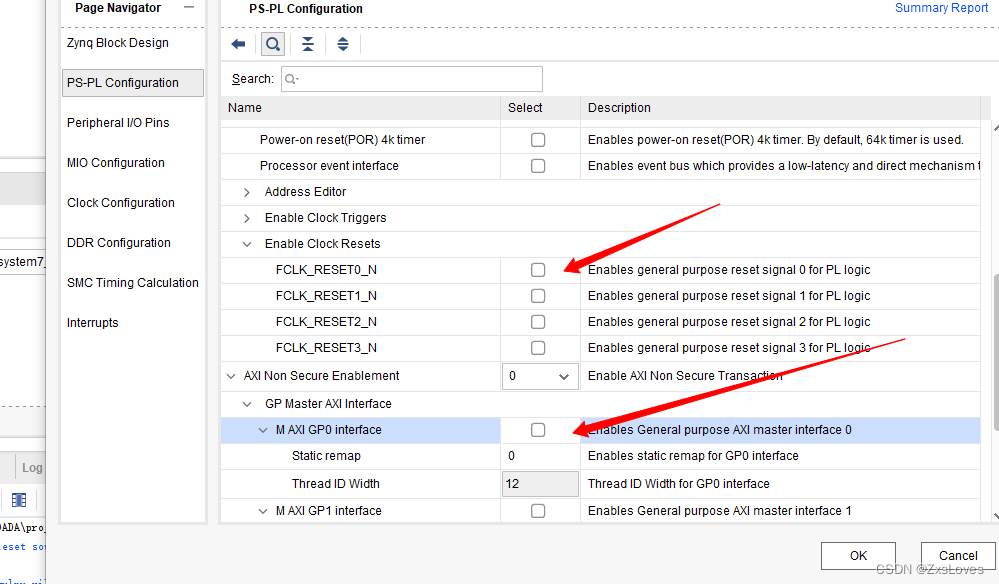

PS-PL Configuration 页面能够配置 PS-PL 接口,包括 AXI、HP 和 ACP 总线接口。

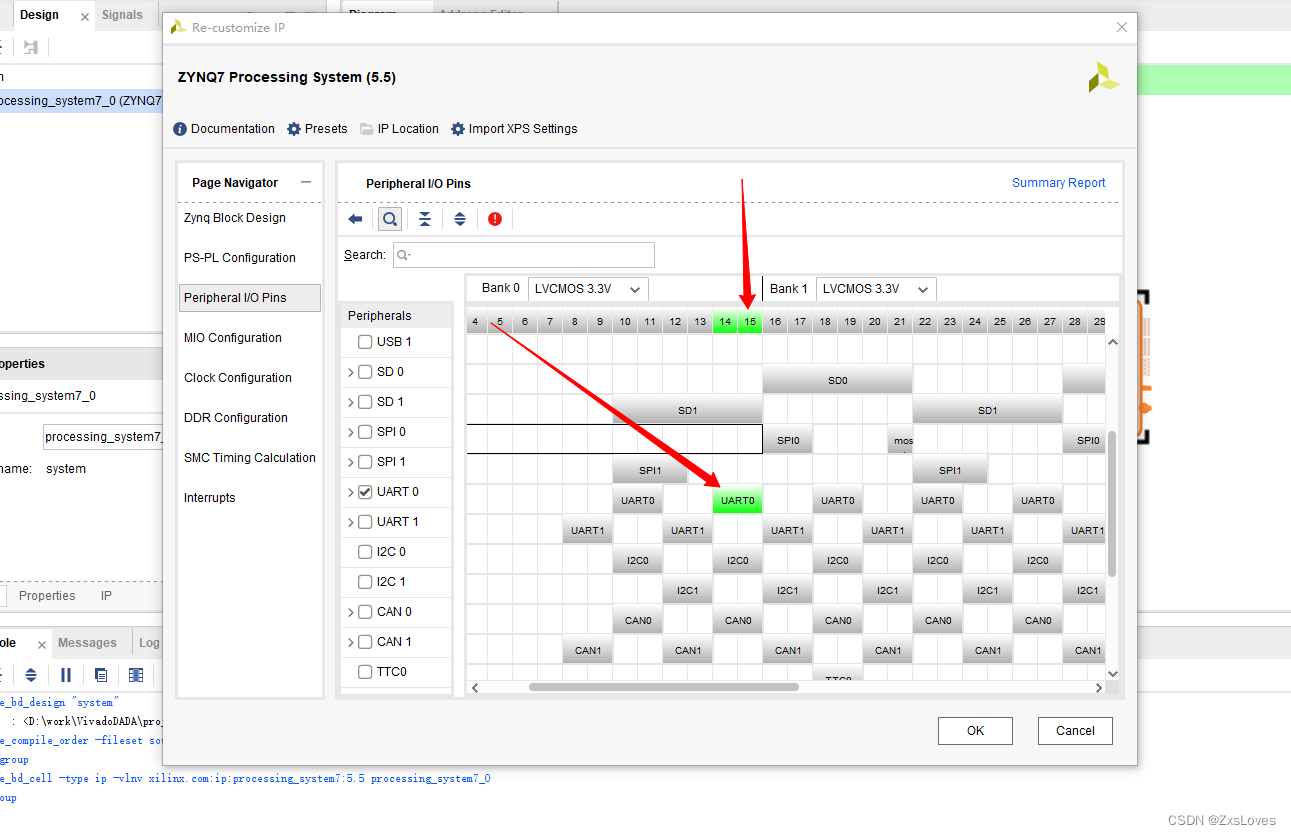

Peripheral IO Pins 页面可以为不同的 I/O 外设选择 MIO/EMIO 配置。

MIO Configuration 页面可以为不同的 I/O 外设具体配置 MIO/EMIO。

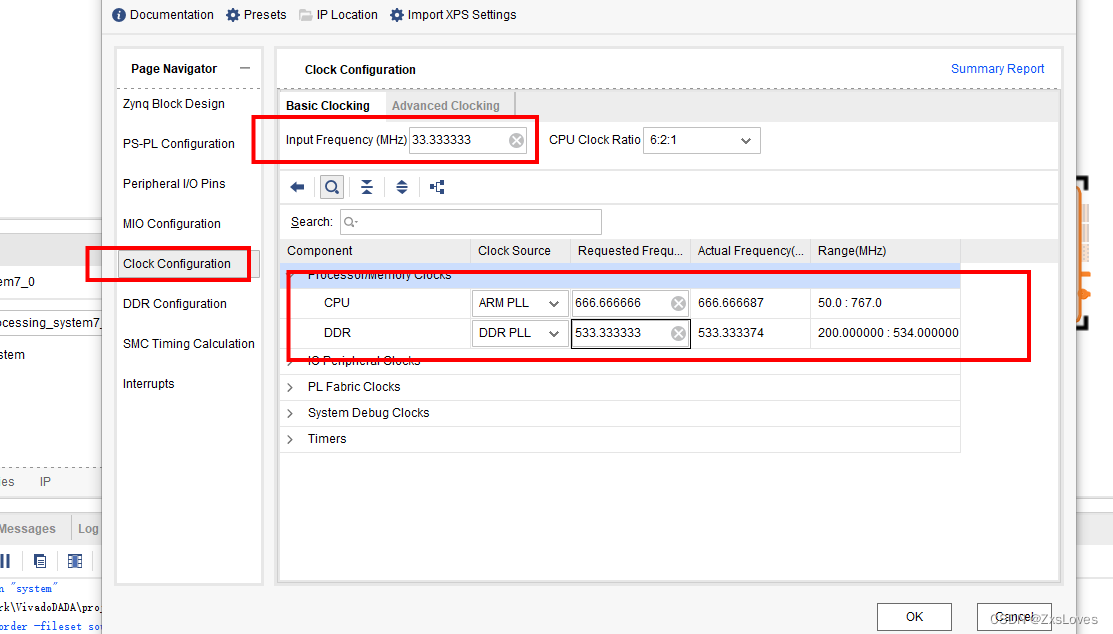

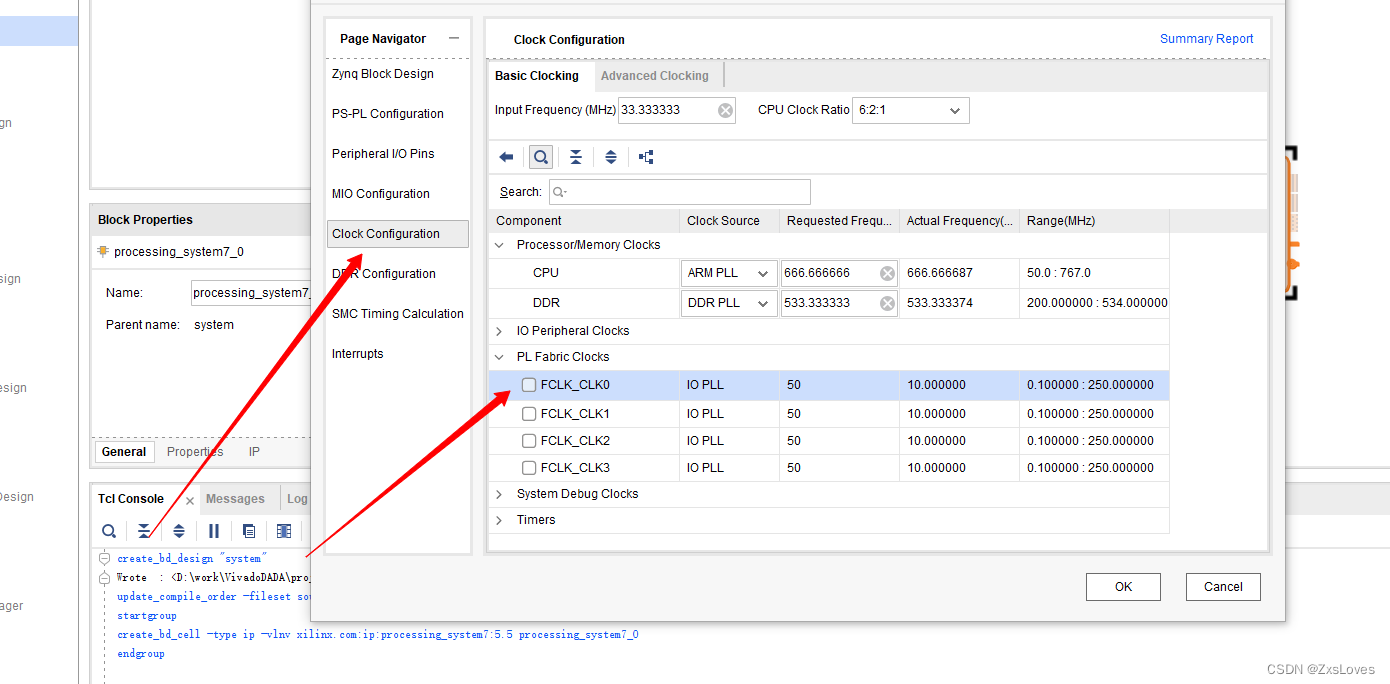

Clock Configuration 页面用来配置 PS 输入时钟、外设时钟,以及 DDR 和 CPU 时钟等。

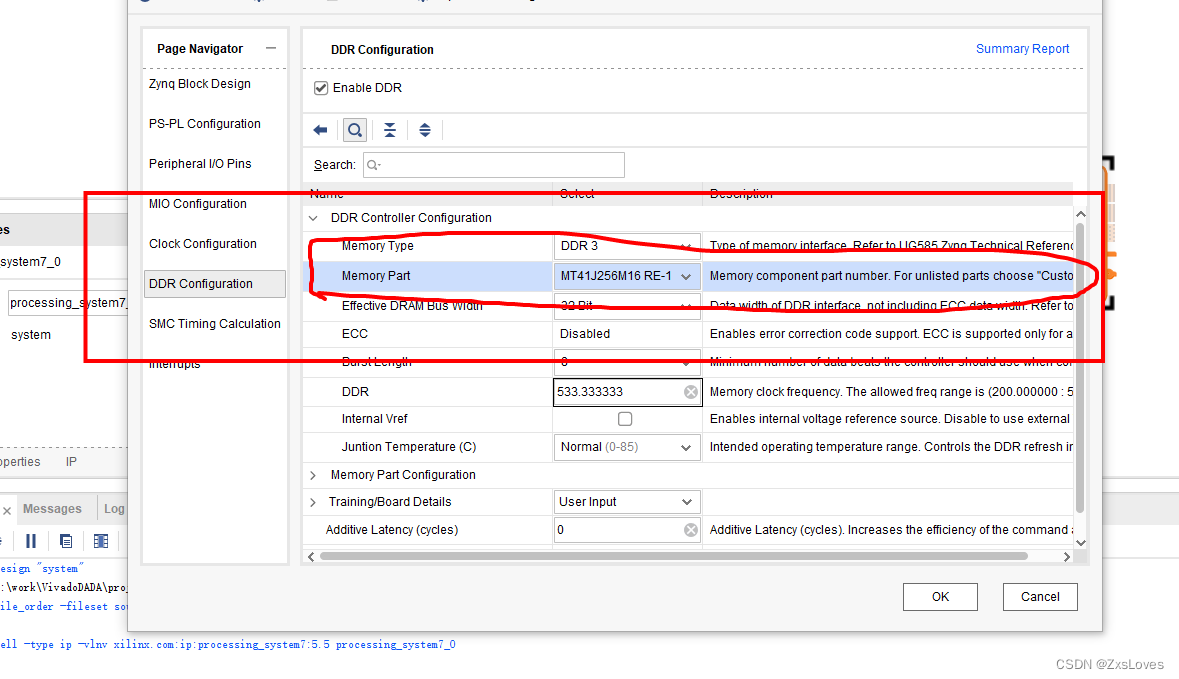

DDR Configuration 页面用于设置 DDR 控制器配置信息。

SMC Timing Calculation 页面用于执行 SMC 时序计算。

Interrupts 页面用于配置 PS-PL 中断端口。

本次发送需要DDR3存储器 和 UART串口 和 arm Cortex-A9核心

其实在原理图上可以看的出来 MIO 14 15可以用作UART串口通信的引脚

点击左侧的 DDR Configuration 页面,在右侧 DDR Controller Configuration 下的“Memory Part”一栏选

择 DDR 的器件,XC7Z020 的核心板选择 MT41J256M16RE-125

基本都是默认的时钟频率

因为是纯PS实验 忽略PL的影响

不懂不懂不懂为什么 点了再说

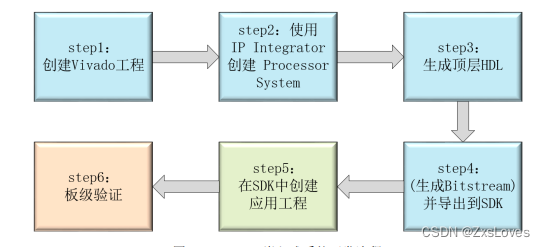

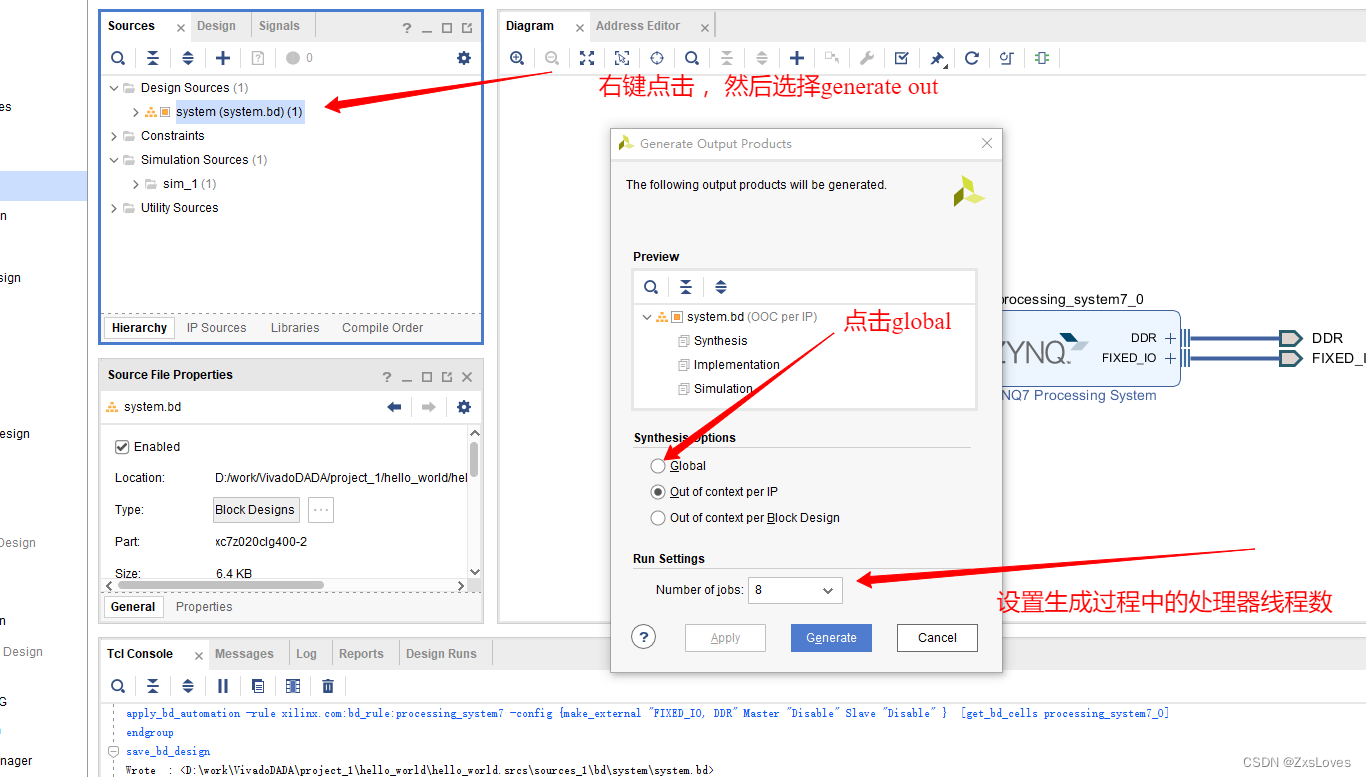

接下来是第三步用来确定 生成顶层HDL模块

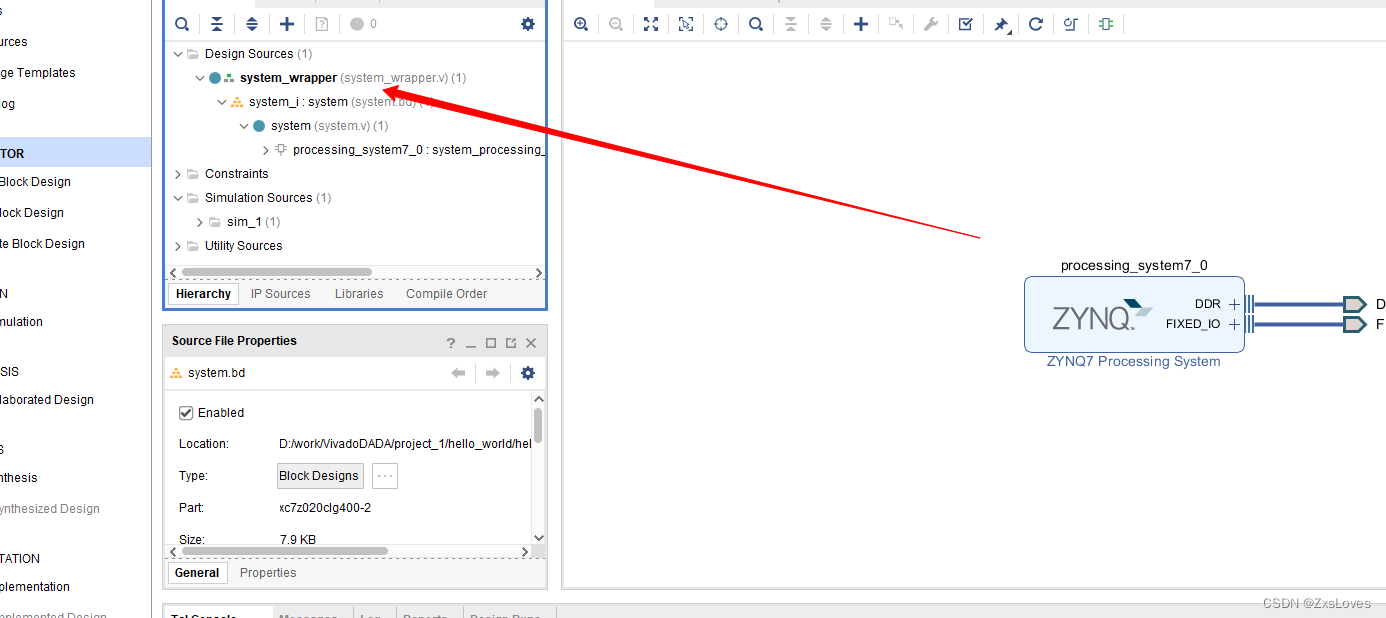

system_wrapper.v 为创建的 Verilog 文件,箭头所指的“品”字形图标指示当前模块为顶层模块。该模

块使用 Verilog HDL 对设计进行封装,主要完成了对 block design 的例化,大家也可以双击打开该文件查看

其中的内容。

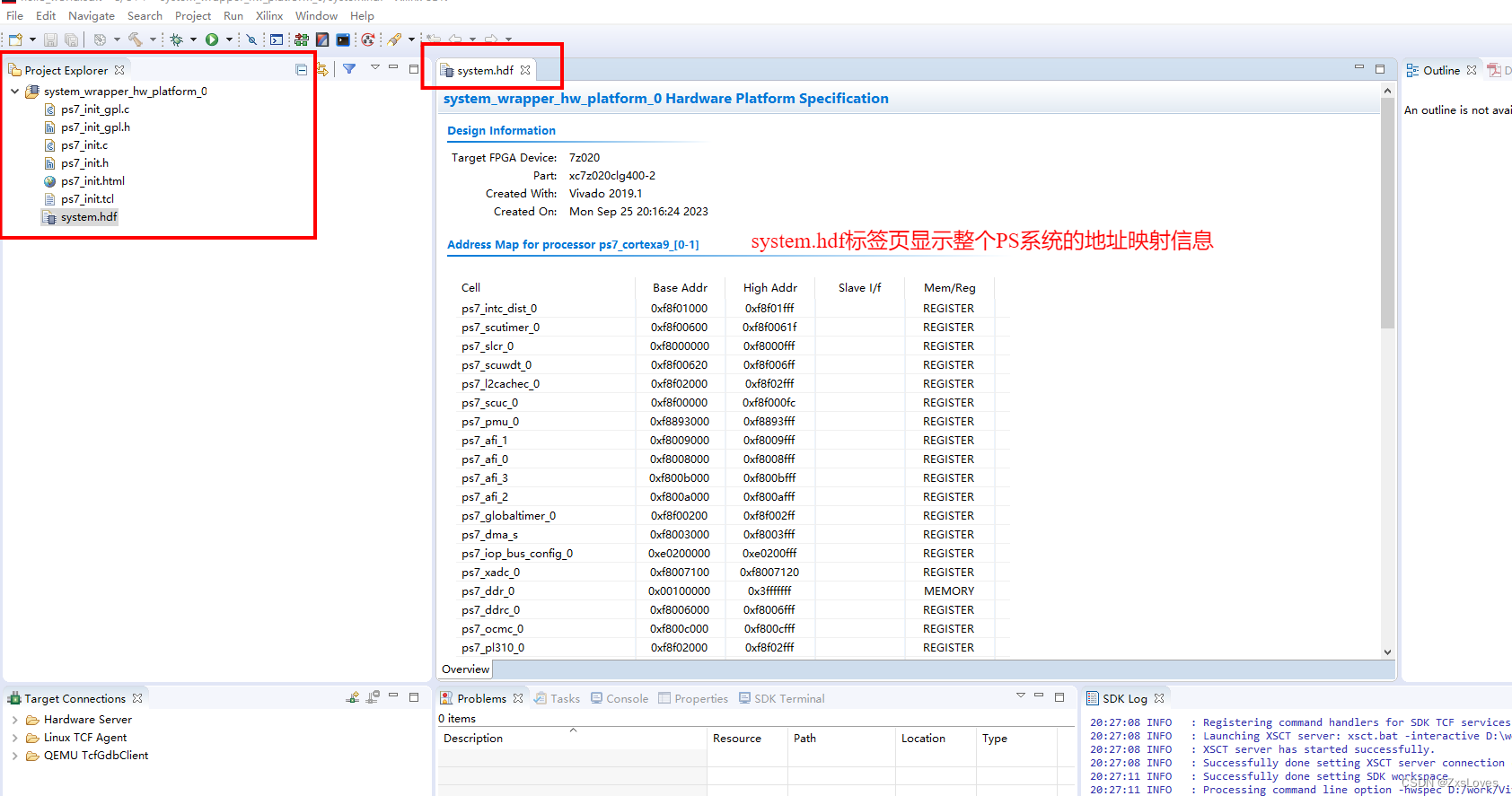

大家应该还记得,在启动 SDK 之前,我们将硬件以一个 ZIP 压缩文件(system_wrapper.hdf)的形式导

出到软件的工作空间。在 SDK 启动时,该文件会自动解压,大家可以在图 1.4.1 的左侧看到解压后的所有

文件。其中,前四个文件(ps7_init_gpl.c、ps7_init_gpl.h、ps7_init.c 和 ps7_init.h)包含了 Zynq SOC 处理系

统的初始化代码,以及 DDR、时钟、pll 和 MIO 的初始化设置信息。在初始化过程中,SDK 使用这些信息

去配置相应的模块,使得应用程序能够在 PS 上运行。

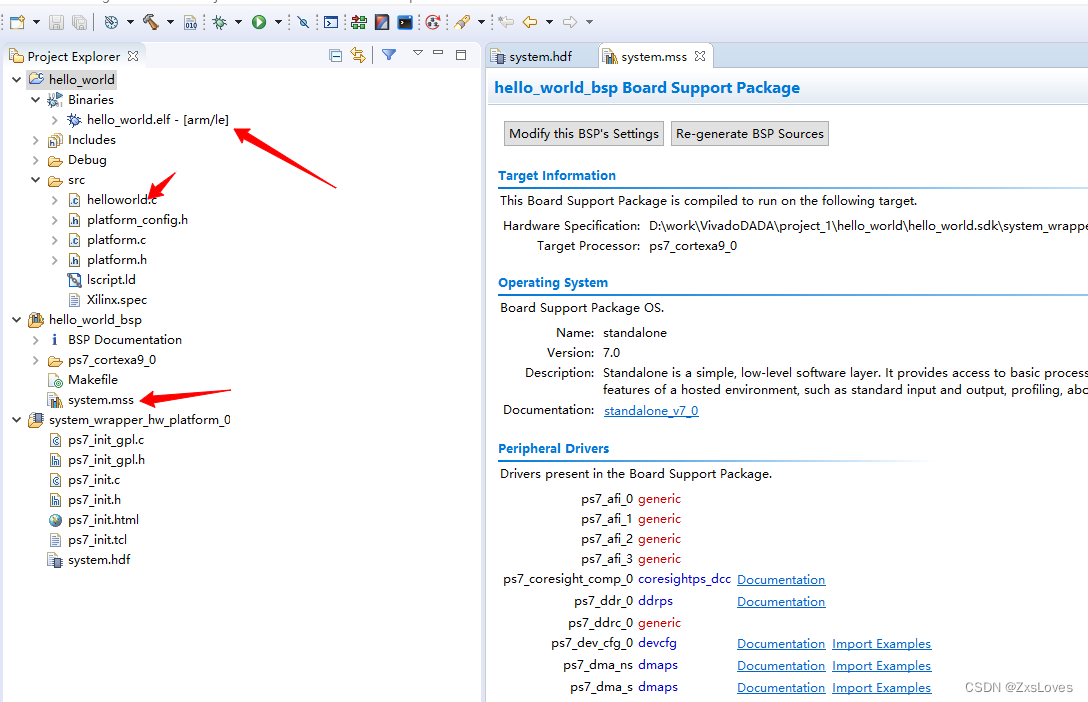

MSS 是英文

Microprocessor Software Specification 的缩写,即微处理器软件说明。该文件包含 BSP 的操作系统信息、硬

件设计中各个外设的软件驱动等信息。

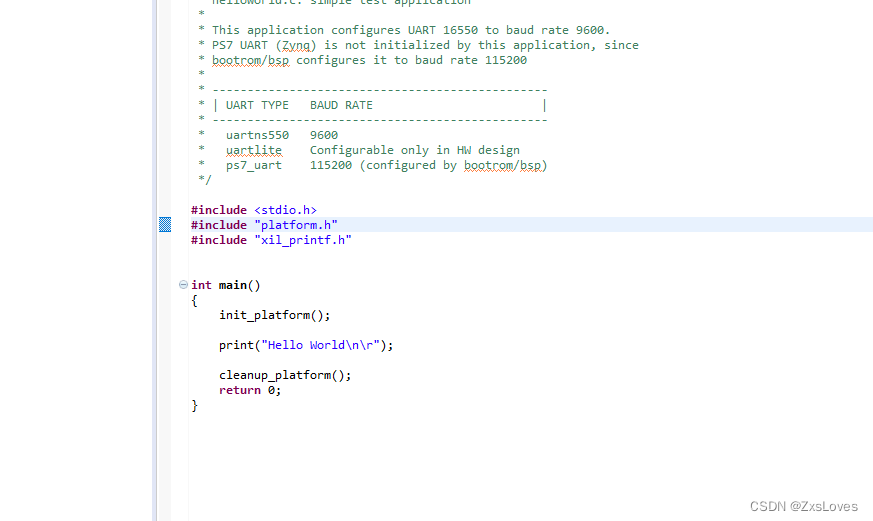

可以看到 init_platform 函数的作用是使能 caches 和初始化 uart;cleanup_platform 函数的作用是取消使

能 caches。实际上这两个函数在该工程中并没有启动任何作用,因为这两个函数是针对于特定平台如

Microblaze 的,对于我们使用的 ZYNQ 平台而言是不起作用的,所以 main 函数中只需包含第 9 行的 print

语句就可以了,出于平台的通用性和可移植性,此处我们保留这两个函数。

另外需要注意程序中打印字符串“Hello World”使用的是 print()函数,而不是 C 语言里的 printf()函数。

print()函数是 Xilinx 定义的一个用于打印字符串的函数,调用该函数需要包含头文件“xil_printf.h”。

![孜然单授权系统V1.0[免费使用]](https://img-blog.csdnimg.cn/5d4887a2f14340c0895275802115f550.png)