【笔记:模拟CMOS集成电路】MOS特性仿真分析

- 前言

- 一、电路图

- 二、电路仿真

- (1)Ids与Vds的关系仿真

- 仿真结果

- 仿真结果分析

- (2)Ids与Vgs的关系仿真

- 仿真结果

- 仿真结果分析

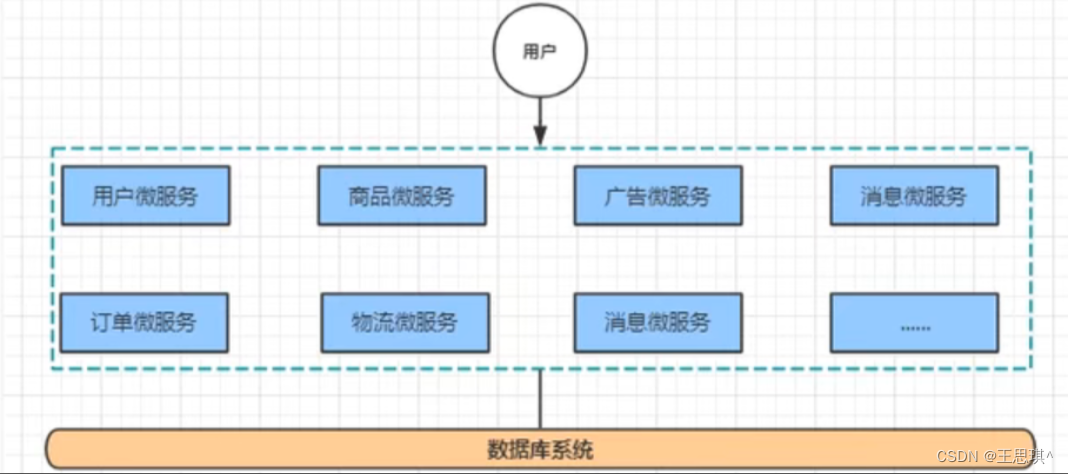

前言

本文为本人学习模拟集成电路相关知识的的学习笔记,入门级别,意为小白快速上手所写,关于进阶文章,后续更新。

关于如何使用Cadence Virtuoso IC617进行Library的创建、cell的创建、简单仿真操作,请参考文章【Cadence Virtuoso】IC617 入门操作 (MOS特性分析)

一、电路图

二、电路仿真

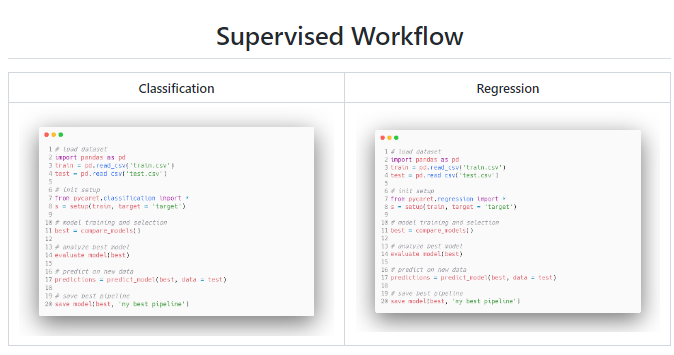

(1)Ids与Vds的关系仿真

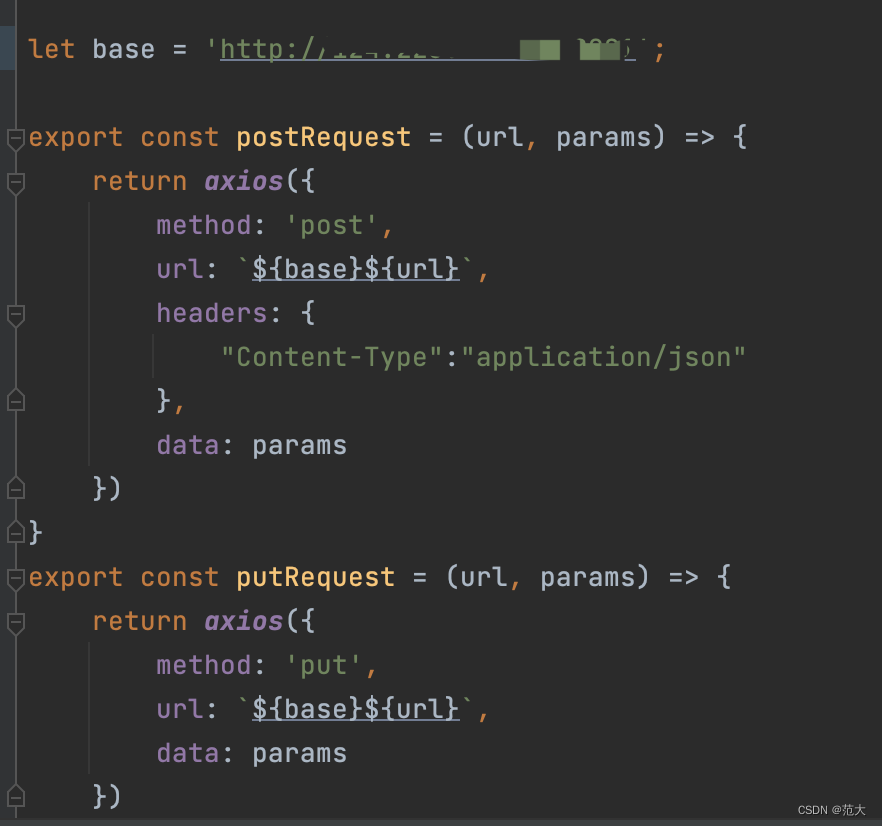

打开ADE L窗口进行仿真设置,为方便后续特性仿真,在该页面依次进入Variables->Edit,新建变量

v

g

s

=

0.9

V

v_{gs}=0.9V

vgs=0.9V和

v

d

s

=

1.5

V

v_{ds}=1.5V

vds=1.5V,设置窗口如下:

接下来进行仿真设置,依次进入Analyses->Choose,设置仿真类型为dc分析,并对Design Variable进行线性设置,区间0-5V,间隔0.2V,并将晶体管漏极电流作为输出,如下图:

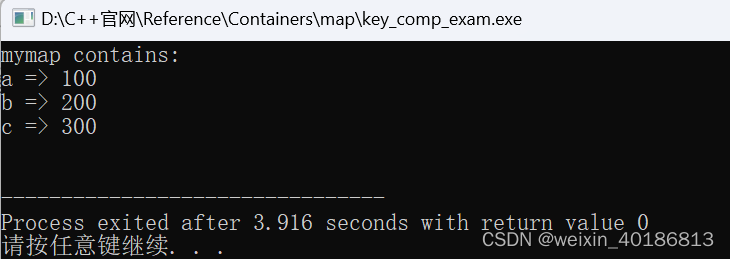

点击Netlist and Run开始进行扫描,MOS管漏极输出电流曲线如下图所示:

仿真结果

仿真结果分析

当

v

d

s

<

∆

v_{ds}<∆

vds<∆时,MOS处于可变电阻区,此时MOS显示出电阻特性

当

v

d

s

>

∆

v_{ds}>∆

vds>∆时,MOS进入饱和区,此时MOS近似为恒流源,但是由于沟道调制效应(λ),恒流特性不理想。

当

v

d

s

≫

∆

v_{ds}≫∆

vds≫∆时,MOS击穿,电流开始增大。

(2)Ids与Vgs的关系仿真

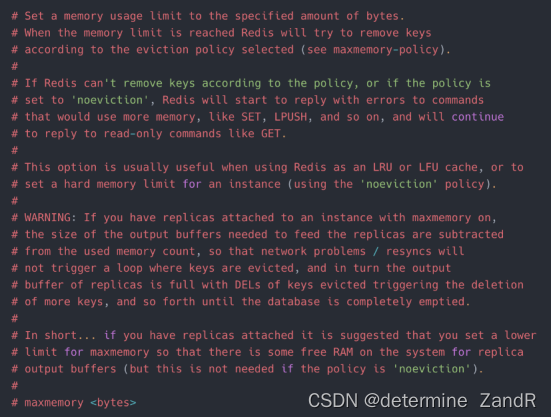

在前面描述操作的基础上,进行参数扫描,选择Tools->Parametric Analysis,对变量vgs进行设置,扫描范围为0.5 - 1.5V,总的扫描数为6。

运行参数扫描,结果如下图所示

仿真结果

仿真结果分析

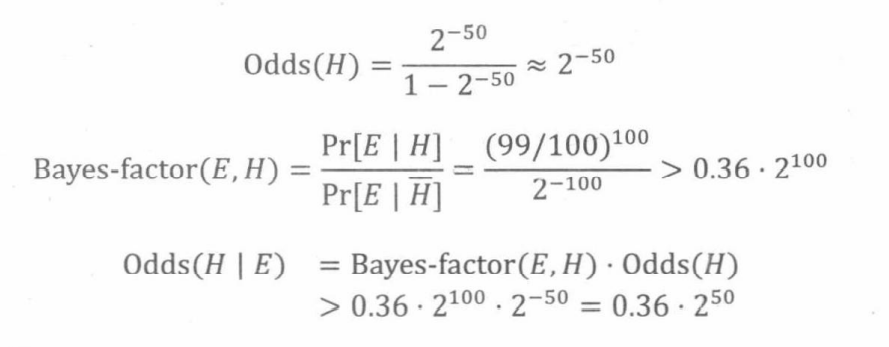

已知参数

V

T

H

=

788

m

V

V_{TH}=788mV

VTH=788mV,随着V_GS的增大,MOS截止区、弱反型区、强反型区、速度饱和区切换(速度饱和没看到,

V

G

S

V_{GS}

VGS不够大,预测

V

G

S

V_{GS}

VGS过大 电流会达到一个饱和值)。

1、由图可知

a)

V

G

S

=

0.5

V

V_{GS}=0.5V

VGS=0.5V和

V

G

S

=

0.7

V

V_{GS}=0.7V

VGS=0.7V时,

i

d

s

i_{ds}

ids几乎为零,处于截止状态。

b)

V

G

S

=

0.7

V

V_{GS}=0.7V

VGS=0.7V时,MOS处于弱反型区,最后进入强反型。

2、 当

V

G

S

>

V

T

H

V_{GS}>V_{TH}

VGS>VTH时,MOS导通,对于给定

V

D

S

V_{DS}

VDS,

i

d

s

∝

V

G

S

2

i_{ds} \propto V_{GS} ^{2}

ids∝VGS2。

欢迎交流探讨

如有错误,可私聊,及时更正