根据上一章的arbiter结构图,结合设计文档中MCDF的整体结构图,可以发现formatter整形器模块是arbiter的上级,负责最终的数据输出,与外界数据接收端相连。

第一节 fromatter文档理解

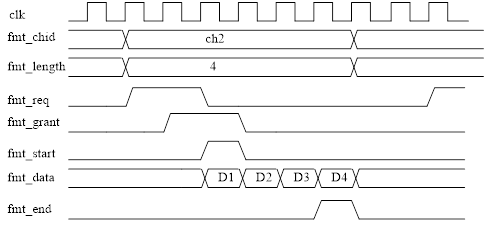

设计文档formatter的部分时序介绍如下

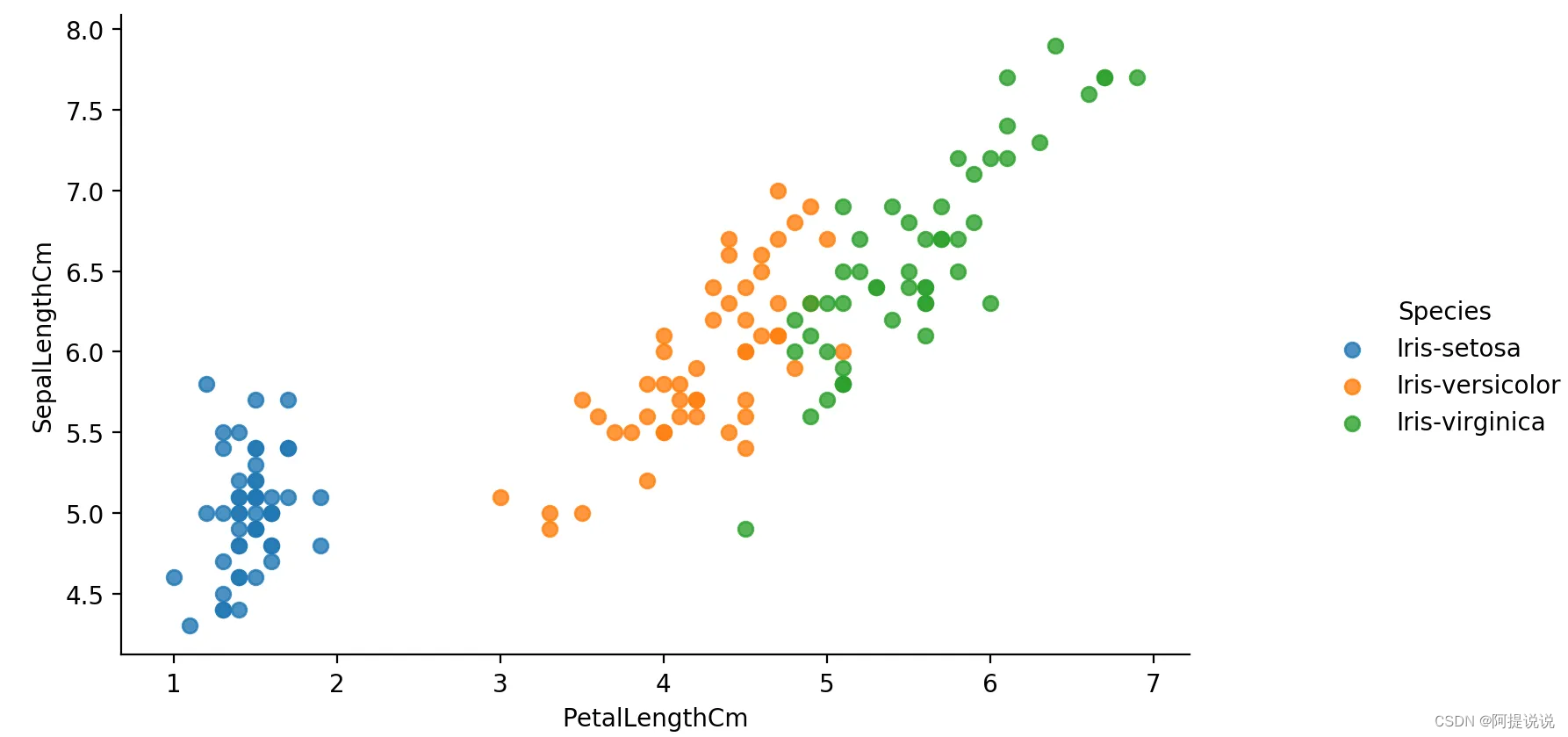

如图所示。整形器按照数据包的形式发送数据。数据包的长度可以是4、8、16和32。整形器必须完整的发送某一个通道的数据包后,才可以准备发送下一个数据包。在发送数据包期间,fmt_chid和fmt_length应保持不变,直到数据包发送结束。

整形器准备发送数据包时,先将fmt_req置高,等待接收端的fmt_grant信号。当fmt_grant信号变为高时,则在下一个周期将:

(1) fmt_req置低

(2) fmt_start输出一个时钟周期的高电平脉冲

(3) fmt_data开始送出第一个数据

数据开始发送后应连接发送,中间不允许有空闲周期,直到发送完所有数据。在发送最后一个数据时,fmt_end信号应置高并保持一个时钟周期。

相邻的数据包之间应至少有一个时钟周期的空闲,即fmt_end变为低电平后,至少经过一个时钟周期fmt_req才可以再次置高。

根据文档描述,我们可以设计以下握手流程。

formatter握手时序关系

当前发送任务完毕时,

先朝下级看,看arbiter有没有发送请求,跟arbiter握手

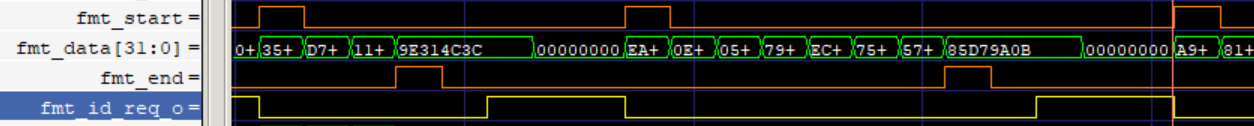

formatter发送结束之后,就将询问信号fmt_id_req置高。如图所示

在

fmt_start和fmt_end之间表示正在发送的时候,fmt_id_req_o为高,表示当前formatter空闲。(当然了,这里空出了一个时钟周期,其实也可以不空。因为设计文档说相邻数据包之间间隔至少1个时钟周期,而上下级握手是需要时间的,因此不需要再额外空出一个周期。)

回顾上一章的结构图,

fmt_id_req_o是和仲裁信号产生部分相连,当clk_i上升沿到来时发现fmt_id_req_o为1,就会刷新当前综合优先级最高的通道并选通。如下图所示,当fmt_id_req_o为1的下一个周期就会刷新并选通最优先的通道。(必须是就绪的,有包可以发送的)。

当然这一块也有可以改进的地方,就是fmt_id_req_o信号下降沿可以提早一个周期结束,以防止数据发送时优先级突变。不过这里因为假想优先级是一开始在寄存器中设定好的,不考虑数据传输时优先级突然改变的情况。因此仍然保留原来的设计。

arbiter刷新优先级选通相应通道(也可能所有通道都没就绪,就选通空通道)可以根据arbiter输入的优先通道信号来知道有没有就绪,如果时11空通道就表示没用就绪(这是一个隐藏的握手信号,arbiter向formatter握手表示是否准备发送)

因此置高完

fmt_id_req就等待有效通道不是11就行了(这里注意信号不要重叠,先让优先级刷新完再判断,因为fmt_id_req过一个周期才是刷新后的通道,所以判断需要等待一个周期再判断)

不是11代表

arbiter就绪,可以发送。这时候已经自动选通了,相当于直连slave,因此slave就等待一个ack信号就可以发送了。现在下级已经就绪,我们通过不是11就向上握手,等待上级进行允许发送。当有效通道不是11,则fmt_req置高,否则继续等待直到不是11.

再朝上级看,formatter等待外部传入允许发送的信号grant

fmt_req置高之后,等待外部允许发送信号fmt_grant,当fmt_grant(为高时,在下一个周期

置低fmt_req

fmt_start输出一个时钟周期的高电平脉冲

fmt_data开始送出第一个数据

[注意]:这里有严格的时序关系,就是grant为高的下个时钟周期就要开始发送第一个数据了,这就要求grant直连的信号slave的ack也满足这样的时序关系,具体而言就是要求slave中的数据在ack之后下一个时钟周期就要发送,valid信号同理

具体做法就是采用了一些简单的波形变换(因为之前的设计还没有涉及到握手时序,波形不满足,所以我又修改了一下,现在slave中波形就满足了时序关系,如下图黄色波形所示)

end信号我们在slave中已经产生过了,只需要直接连接过来,通过多路选择器选通即可

握手结束,等待数据发送完毕

然后再fmt_id_req置高开始下一次循环

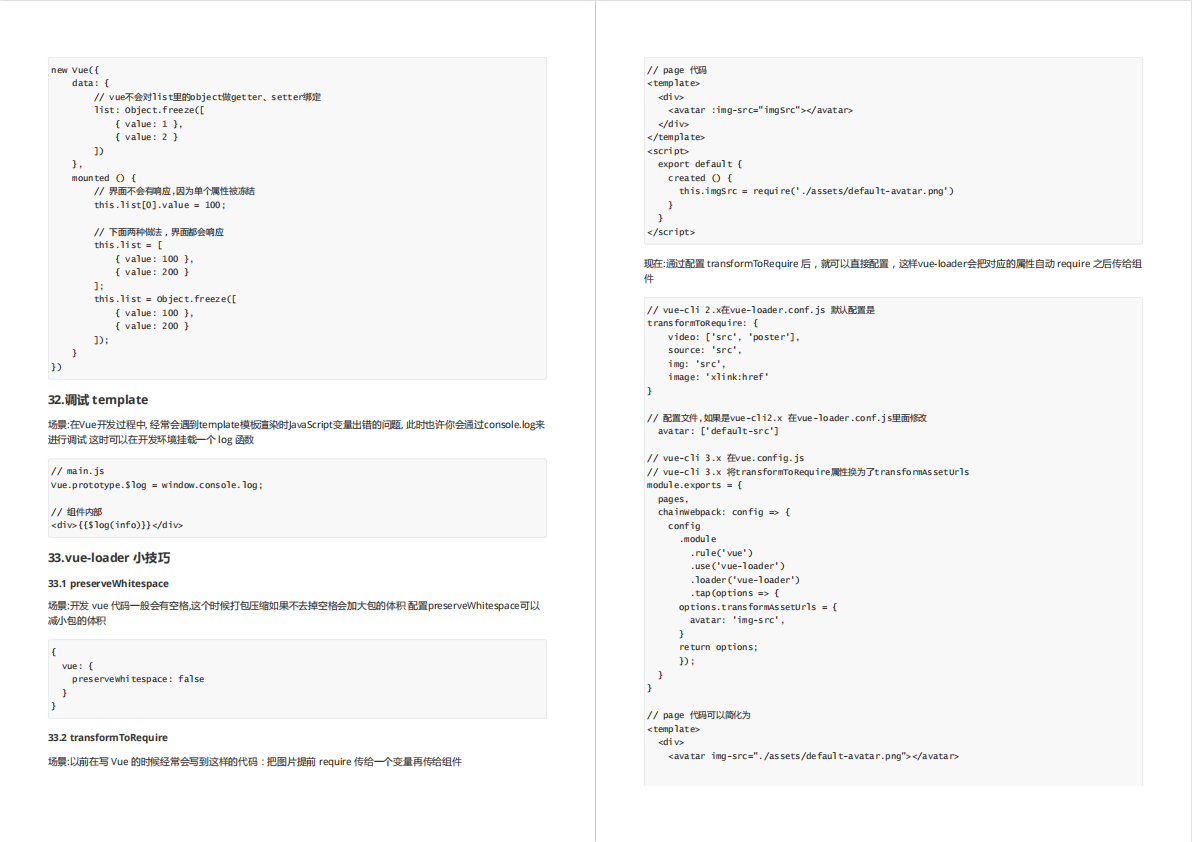

第二节 fromatter代码实现

文件名:formatter.v

具体注释详见代码

/***************<MCDF 整形器 formatter>*********************/

`timescale 1ns/100ps

/***************<端口声明>*********************/

module formatter

(

input wire clk_i,

rstn_i,

input wire a2f_val_i,//!!!这个信号没用到,检查是否可以去除

input wire [1:0] a2f_id_i,

input wire [31:0] a2f_data_i,

input wire [2:0] a2f_pkglen_sel_i,

input wire fmt_grant_i,

input wire a2f_end_i,//增加的信号,在arbiter中判断end更方便

output wire f2a_ack_o,

output reg fmt_id_req_o,

output wire [1:0] fmt_child_o,

output reg [5:0] fmt_length_o,

output wire fmt_req_o,

output wire [31:0] fmt_data_o,

output reg fmt_start_o,

output wire fmt_end_o

);

/***************<中间信号>*********************/

reg fmt_end_d1;//end信号时延一个周期

reg fmt_id_req_o_d1;//fmt_id_req_o信号延迟一个周期,用于波形变换,使得fmt_req上升沿延后

/***************<时序电路>*********************/

//fmt_id_req_o信号延迟一个周期

always @(posedge clk_i or negedge rstn_i) begin

if(~rstn_i)

fmt_id_req_o_d1<=0;

else

fmt_id_req_o_d1<=fmt_id_req_o;

end

// >>>fmt_end_d1用于产生fmt_id_req_o,并保证两次发送之间的时隙

//end信号时延一个周期

always @(posedge clk_i or negedge rstn_i) begin

if(~rstn_i)

fmt_end_d1<=0;

else

fmt_end_d1<=fmt_end_o;

end

// >>>fmt_id_req_o<<<

//1产生向下握手信号 fmt_id_req_o,等待优先通道不为11

always @(posedge clk_i or negedge rstn_i) begin

if(~rstn_i)begin

fmt_id_req_o<=1;//复位时没有发送占用,因此可以向下级握手

end

else if(fmt_end_d1)begin//因为end和start并不会重合,所以谁先谁后判断不影响

fmt_id_req_o<=1;

end

else if(fmt_grant_i)begin

fmt_id_req_o<=0;

end

else

fmt_id_req_o<=fmt_id_req_o;

end

// >>> fmt_start_o 是f2a_ack_o延迟一个周期

always @(posedge clk_i or negedge rstn_i) begin

if(~rstn_i)

fmt_start_o<=0;

else

fmt_start_o<=f2a_ack_o;

end

/***************<组合电路>*********************/

// >>>fmt_req_o<<<

//等待优先通道不为11,产生 fmt_req_o,表示下级就绪,当出现 fmt_grant_i 时再置低

//采用 波形变换 方式实现 优先通道不为11&fmt_id_req_o,参考时序参考图

assign fmt_req_o=fmt_id_req_o & (a2f_id_i!=2'b11) & fmt_id_req_o_d1;

//波形变换,ack信号,在通道联通后,直送给slave

assign f2a_ack_o=fmt_grant_i & fmt_req_o;

//一些直连信号

assign fmt_end_o=a2f_end_i;//直连arbiter中的end信号(这个信号是另加的,因为arbiter中判断end更容易)

assign fmt_data_o=a2f_data_i;

assign fmt_child_o=a2f_id_i;

always @(*) begin//数据包长度译码(在slave_FIFO里面时用求幂实现)

case(a2f_pkglen_sel_i)

3'b000:fmt_length_o<=6'd4;

3'b001:fmt_length_o<=6'd8;

3'b010:fmt_length_o<=6'd16;

3'b011:fmt_length_o<=6'd32;

default:

fmt_length_o<=6'd32;

endcase

end

endmodule

第三节 fromattertestbench代码实现

文件名:formatter_tb.v

具体注释详见代码

`timescale 1ns/100ps

`include "formatter.v"

/*************************<端口声明>*********************/

module formatter_tb;

reg clk_i;

reg rstn_i;

reg a2f_val_i;

reg [1:0] a2f_id_i;

reg [31:0] a2f_data_i;

reg [2:0] a2f_pkglen_sel_i;

reg fmt_grant_i;

reg a2f_end_i; //增加的

wire f2a_ack_o;

wire fmt_id_req_o;

wire [1:0] fmt_child_o;

wire [5:0] fmt_length_o;

wire fmt_req_o;

wire [31:0] fmt_data_o;

wire fmt_start_o;

wire fmt_end_o;

/*************************<实例化>*********************/

formatter fm1(

clk_i,

rstn_i,

a2f_val_i,

a2f_id_i,

a2f_data_i,

a2f_pkglen_sel_i,

fmt_grant_i,

a2f_end_i,

f2a_ack_o,

fmt_id_req_o,

fmt_child_o,

fmt_length_o,

fmt_req_o,

fmt_data_o,

fmt_start_o,

fmt_end_o

);

/*************************<信号产生>*********************/

initial begin

clk_i<=0;

rstn_i<=0;

a2f_val_i<=0; //这个信号没用到

a2f_id_i<=2'b11; //接通的通道

a2f_data_i<=$random; //接通通道的数据

a2f_pkglen_sel_i<=0; //与a2f_id_i同步变化

fmt_grant_i<=0;

a2f_end_i<=0;

$dumpfile("formatter.vcd");

$dumpvars;

#15 rstn_i<=1;

#40

@(posedge clk_i) a2f_id_i<=2'b00;

#30

@(posedge clk_i) fmt_grant_i<=1;

@(posedge clk_i) fmt_grant_i<=1;

@(posedge clk_i) fmt_grant_i<=0;

@(posedge clk_i) fmt_grant_i<=0;

@(posedge clk_i) a2f_end_i<=1;

@(posedge clk_i) a2f_end_i<=0;

#500 $finish;

end

always @(posedge clk_i) begin

a2f_data_i<=$random;

end

always #10 clk_i<=~clk_i;

always @(*) begin//模拟arbiter中的信号同步

case(a2f_id_i)

2'b00:a2f_pkglen_sel_i<=3'b000;

2'b01:a2f_pkglen_sel_i<=3'b001;

2'b10:a2f_pkglen_sel_i<=3'b010;

2'b11:a2f_pkglen_sel_i<=3'b000;

endcase

end

endmodule

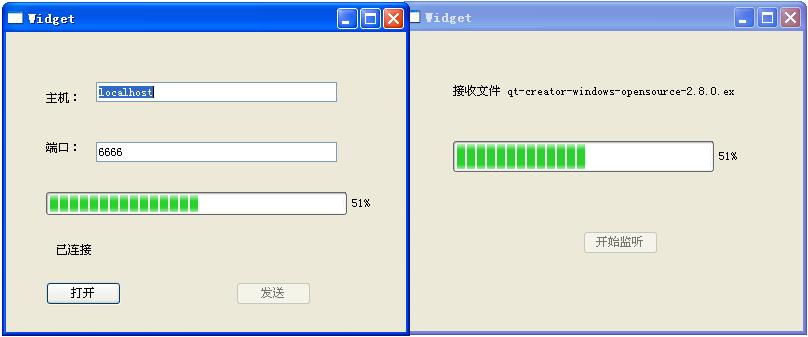

仿真结果如下,同样地,因为涉及到上下级时序配合,因此此处也省略波形分析,将在最后的MCDF顶层仿真中进行详细分析。