qtrvsim 使用

介绍

Qtrvsim 是一个基于 WebAssembly(基于非 js 语言并使得其可以在浏览器中运行)的图形化 RISC-V 微处理器模拟器,给初学者提供了一个实现 RISC-V 架构的渠道。

Developed by the Computer Architectures Education project at Czech Technical University.

github 项目链接:cvut/qtrvsim: RISC-V CPU simulator for education purposes (github.com)

下载使用

有两种使用方法,第一种是直接访问基于 WebAssembly 的 Qtrvsim 网站在线设计,另一种是下载仓库代码编译运行。

在线网站:https://comparch.edu.cvut.cz/qtrvsim/app

下载运行:这里作者只尝试了 Ubuntu 环境下的搭建。

$ git clone git@github.com:cvut/qtrvsim.git

# 需要安装的其他环境:Qt 5, elfutils

$ cmake -DCMAKE_BUILD_TYPE=Release /path/to/qtrvsim

$ make

模版程序运行

下面作者演示一下在其上运行 Web 中提供的测试程序的流程。

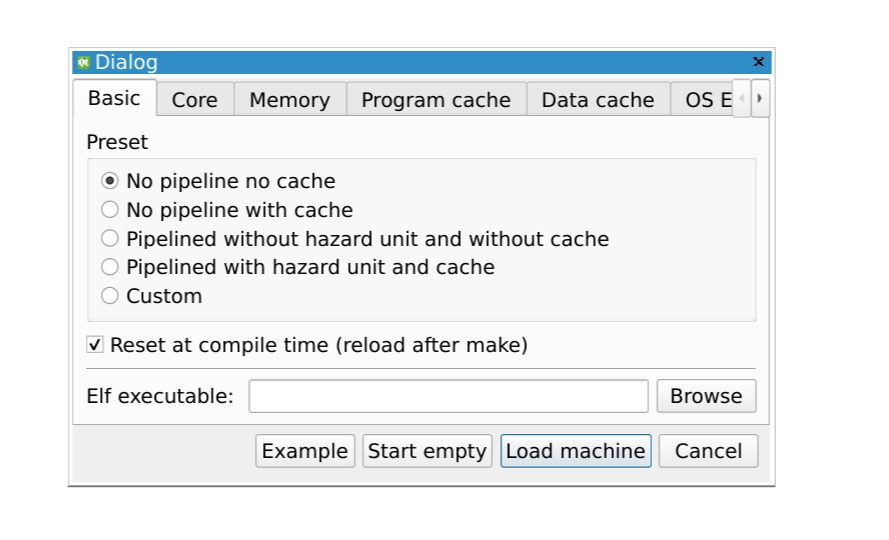

打开 Web 网站,配置程序信息,这里选择无缓存和管道的基础配置,点击 Start Empty:

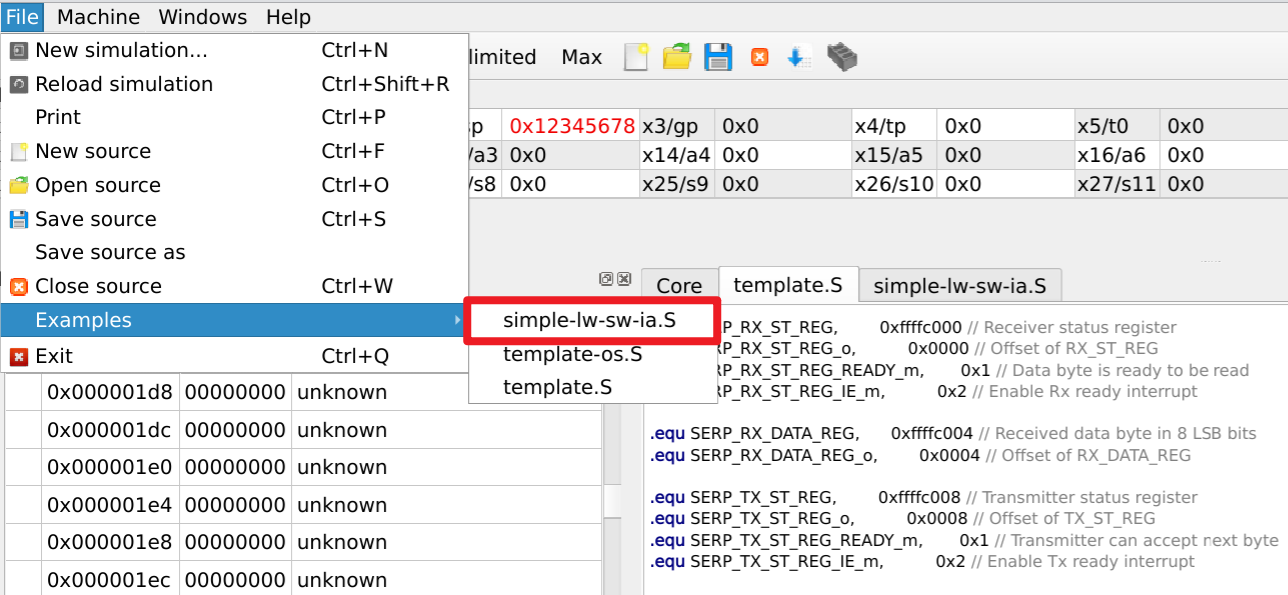

在 File 中找到提供好的模板文件:

可以看到模板程序是一个简单的存取操作

// Template file with simple memory example

// QtRVSim simulator https://github.com/cvut/qtrvsim/

//

// template-os.S - example file

//

// (C) 2021 by Pavel Pisa

// e-mail: pisa@cmp.felk.cvut.cz

// homepage: http://cmp.felk.cvut.cz/~pisa

// work: http://www.pikron.com/

// license: public domain

// Directives to make interesting windows visible

#pragma qtrvsim show registers # 打开寄存器窗口

#pragma qtrvsim show memory # 打开内存窗口

.globl _start

.option norelax

.text

_start:

loop:

// load the word from absolute address

lw x2, 0x400(x0)

// store the word to absolute address

sw x2, 0x404(x0)

// stop execution wait for debugger/user

// break

// ensure that continuation does not

// interpret random data

beq x0, x0, loop # 不断把 x0 的值赋给 x2,再把 x2 的值赋给 x0,赋值失败跳出循环

nop

nop

ebreak # 断点

.data

.org 0x400 # 声明后续数据地址

src_val:

.word 0x12345678 # x0 初值

dst_val:

.word 0 # x2 初值

// Specify location to show in memory window

#pragma qtrvsim focus memory src_val

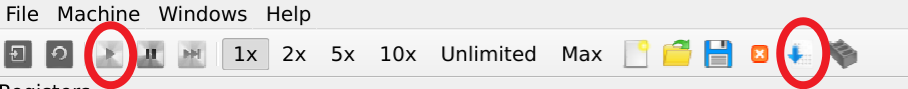

接下来,点击上方的下载标志箭头下载程序,把程序烧录到 Program 栏中;点击三角形按钮开始运行。

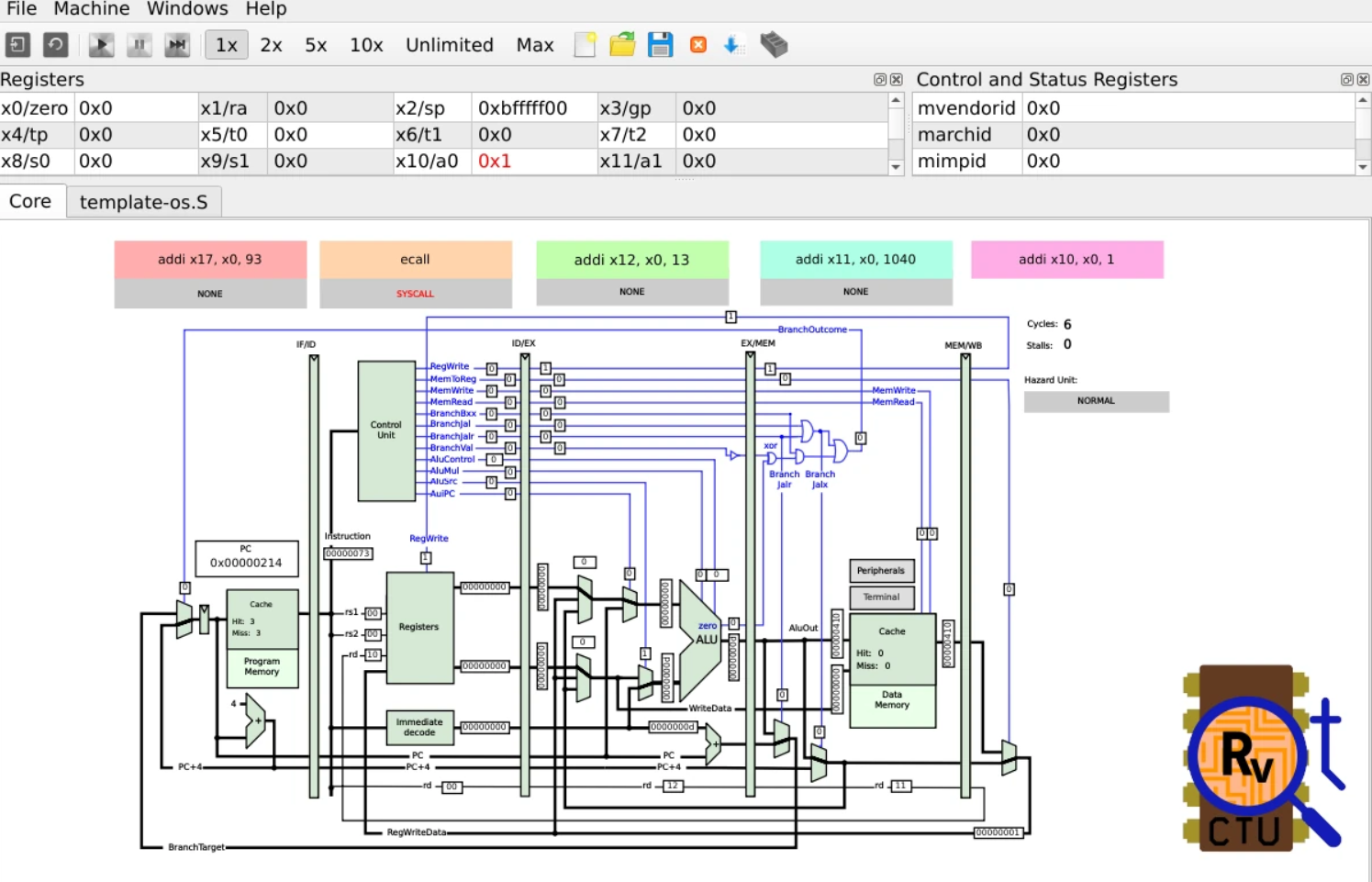

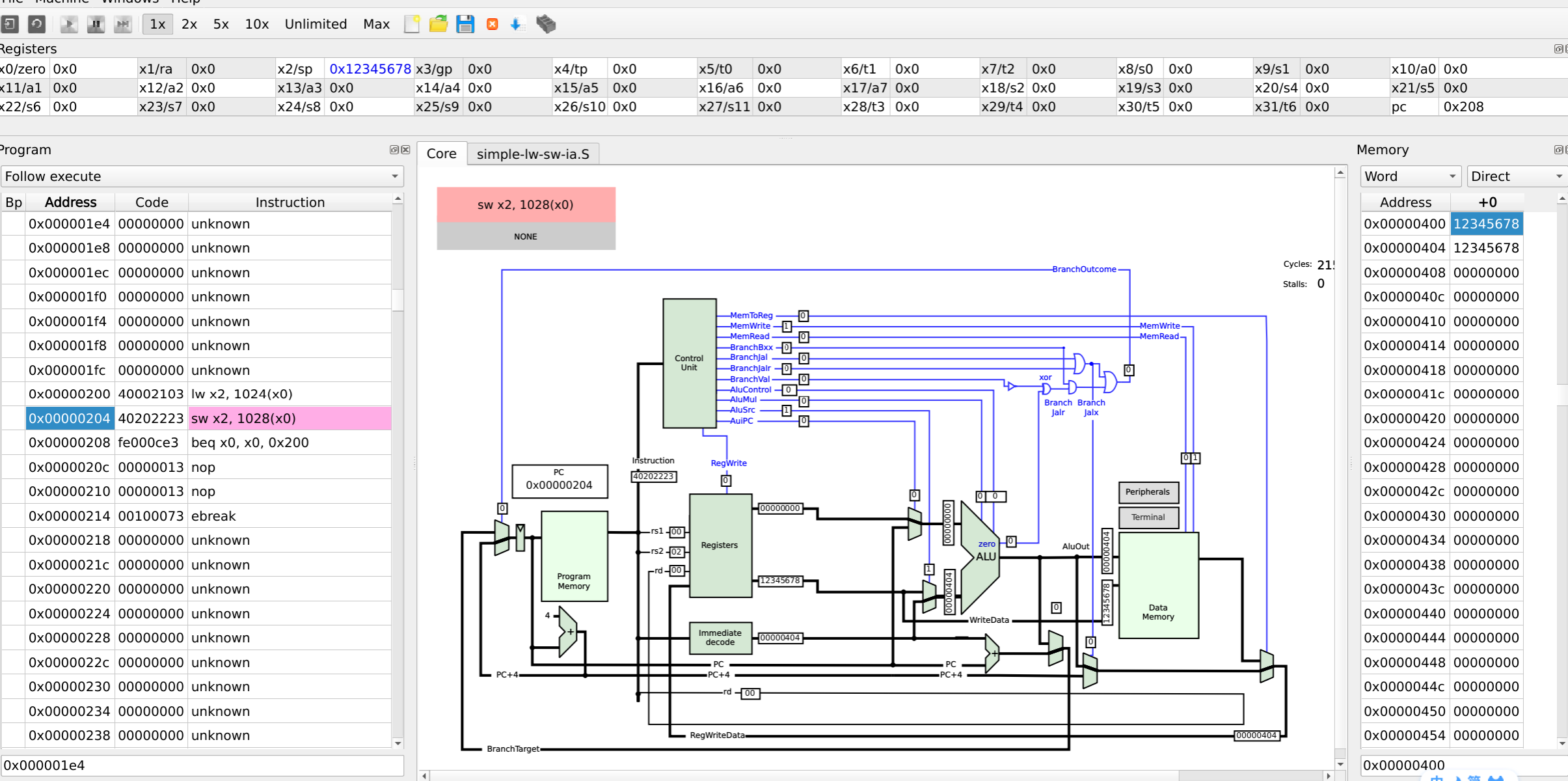

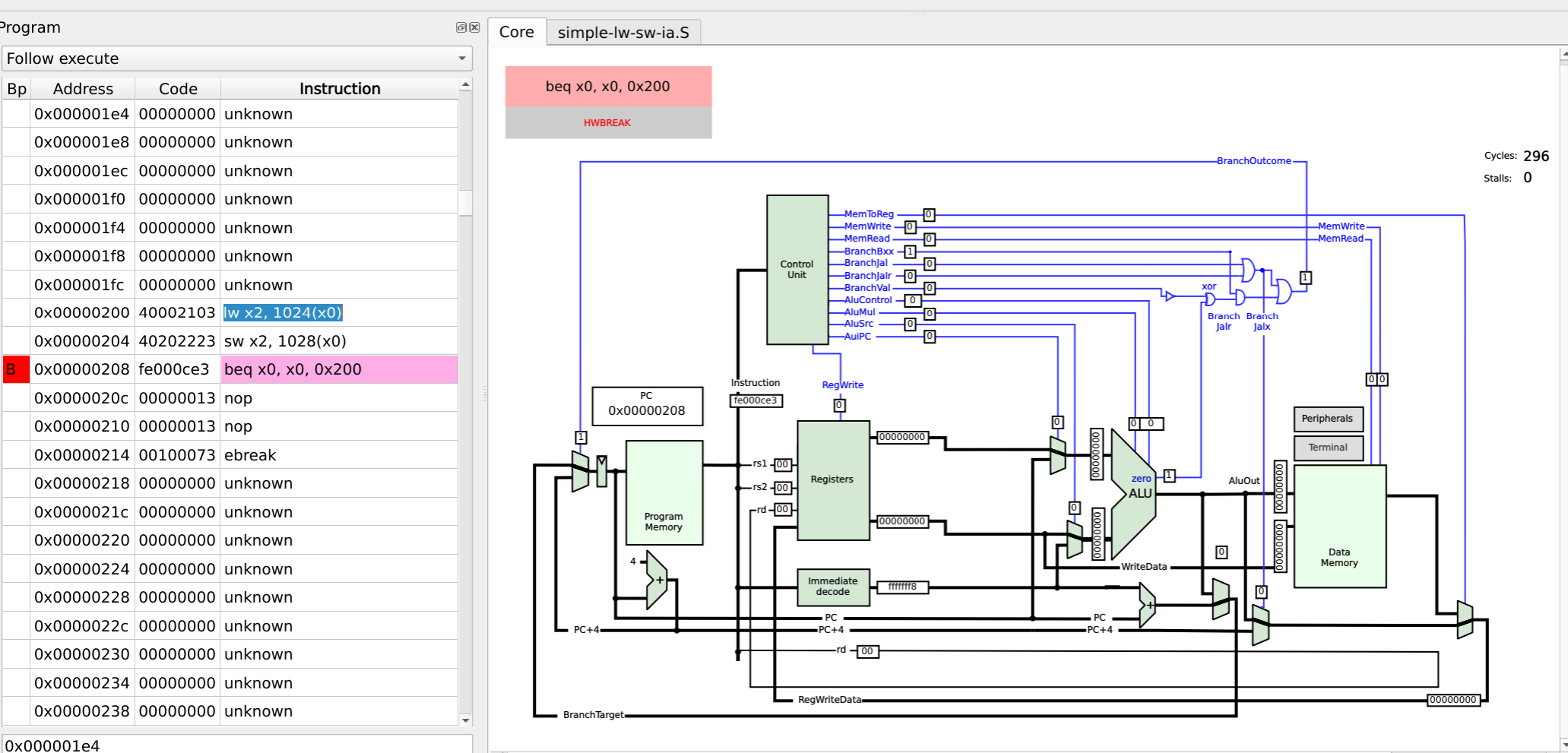

可以看到程序开始逐行执行。

左侧 Program 窗口的字段分别是:断点 breakpoint,指令地址,指令值(hex),指令本身。

右侧 memory 窗口中的值是对应内存中数据值,可以看到 0x400 处 和 0x404 处都被赋值为 0x12345678.

上方寄存器窗口存放了寄存器中存储的数据,作为临时存储的 x2 值被赋值为 0x12345678.

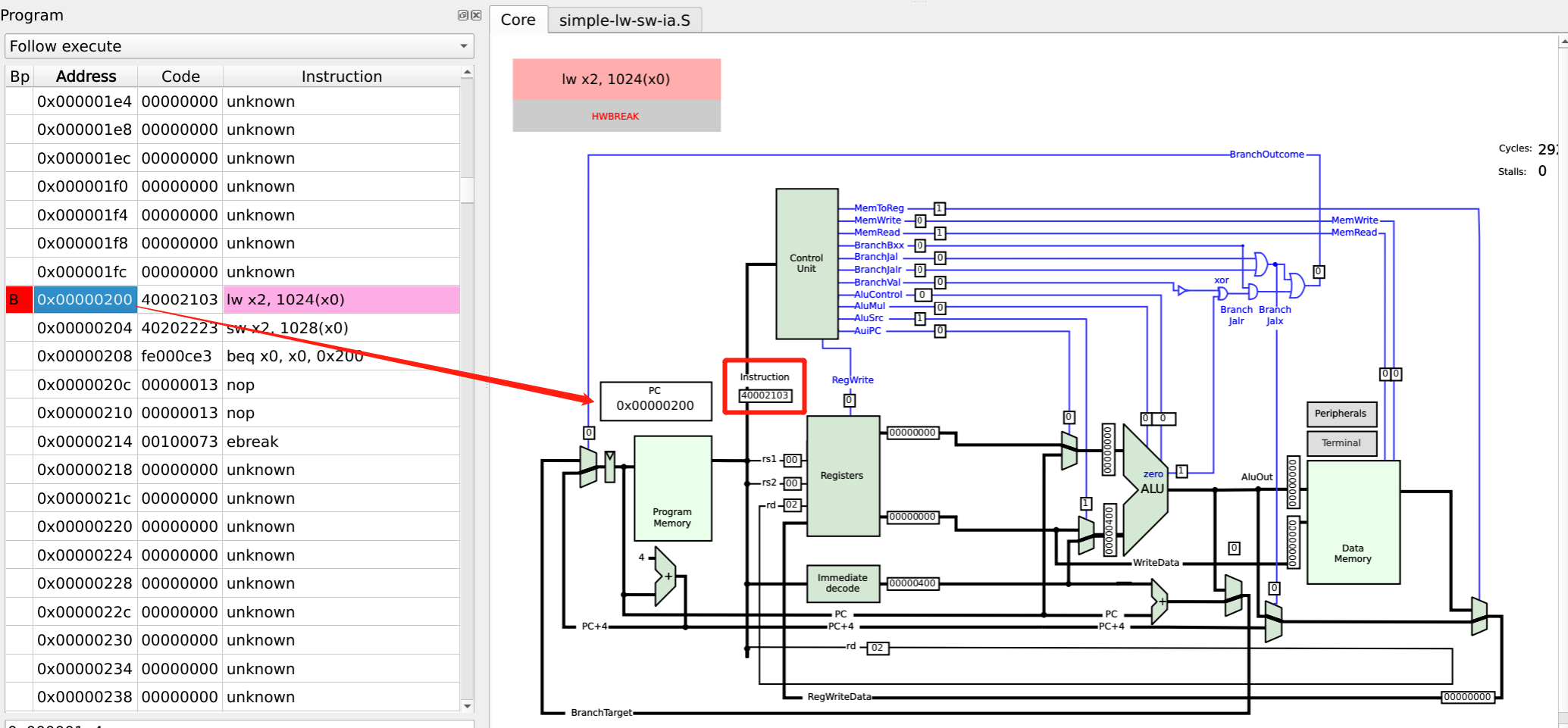

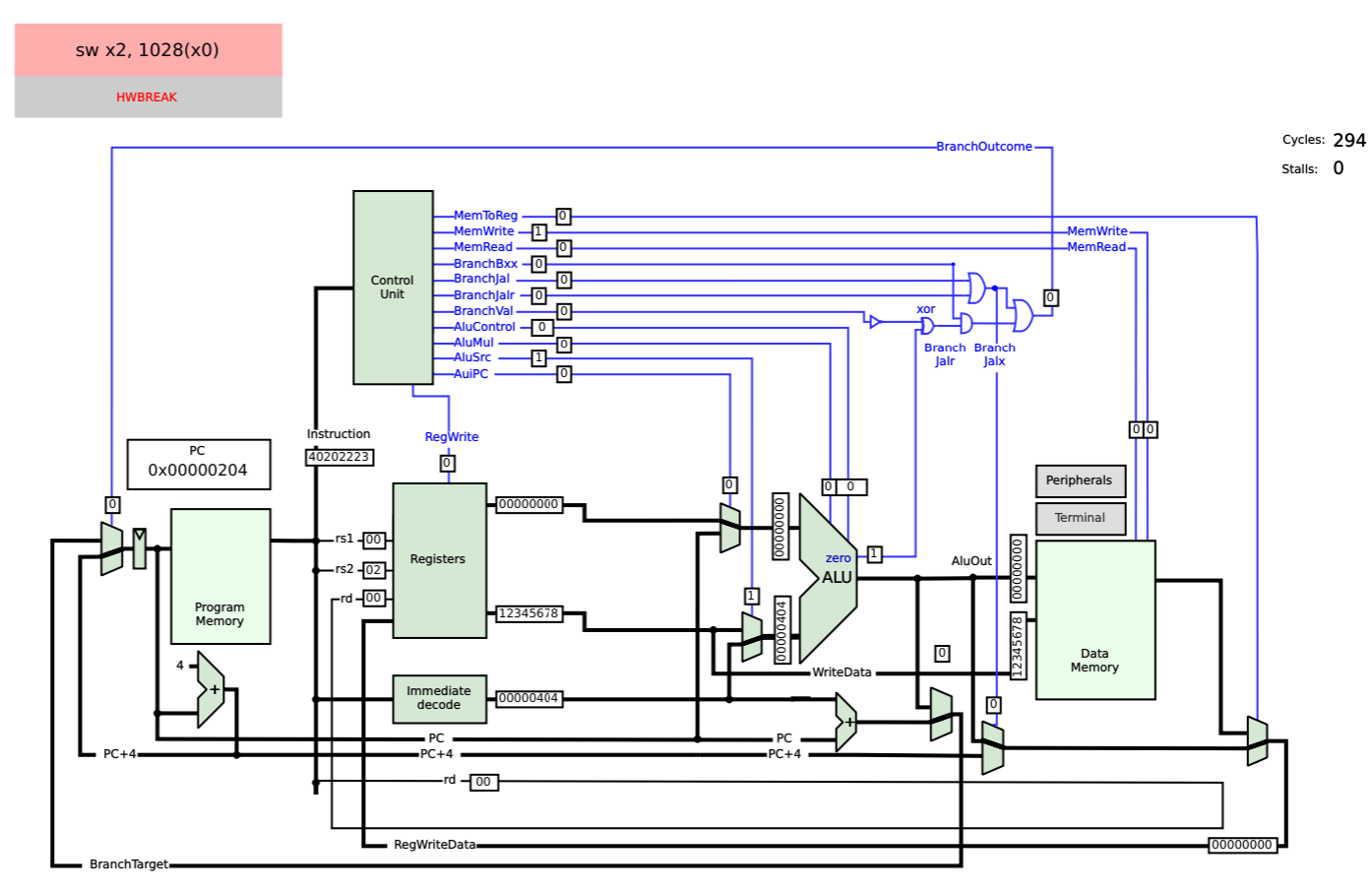

我们在第一条指令(0x00000200)BP 处双击打断点,这时可以看到 Core 中具体数据状态。

PC 处是当前指令位置,Instruction 取得当前指令值,

上方 Control Unit 标明:当前指令为读取内存,读到寄存器中,且要对 src 地址做运算,因此开启了相应状态位。

rs1 rs2 rd 标明源寄存器和目标寄存器,x0 为 rs1,x2 为 rd。

立即数是指定 x0 偏移地址为 0x400.

再看第二条指令时 Core 状态如下:

PC 值随着指令执行而逐渐增加,Control Unit 中的标志位标明:将数据写入内存,且要对 src 地址进行运算。

x0 为 rs1,x0 为 rs2,此指令不存在 rd。

可以看到寄存器中传输了 0x12345678 数据到 Data Memory 中。

立即数是指定 x0 偏移地址为 0x404.

最后再看最后一条指令的执行状态:

主控单元标明此指令为一个判断跳转指令,x0=0 时跳转到 loop 处也就是 0x00000200.

这里立即数采用的是 -8 的补码表示,表示若判断成功应+(-8)跳转到 0x00000200 处。

总结

Qtrvsim 提供了一个很有趣的在线 RISC-V 架构实现平台,非常适合初学者学习,实现一些 RISC-V 模块。不过目前还不是特别完善,现阶段只支持 RVxxG ,RVxxM 和一些伪指令。