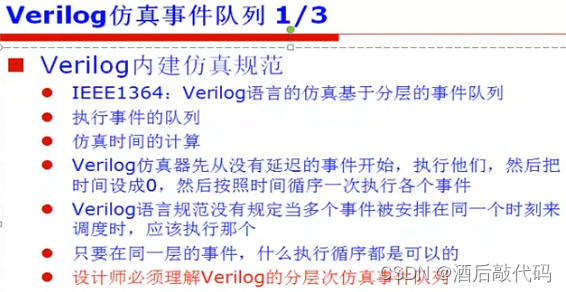

1、Verilog simulation event queue(Verilog 仿真时间队列)

龟腚:

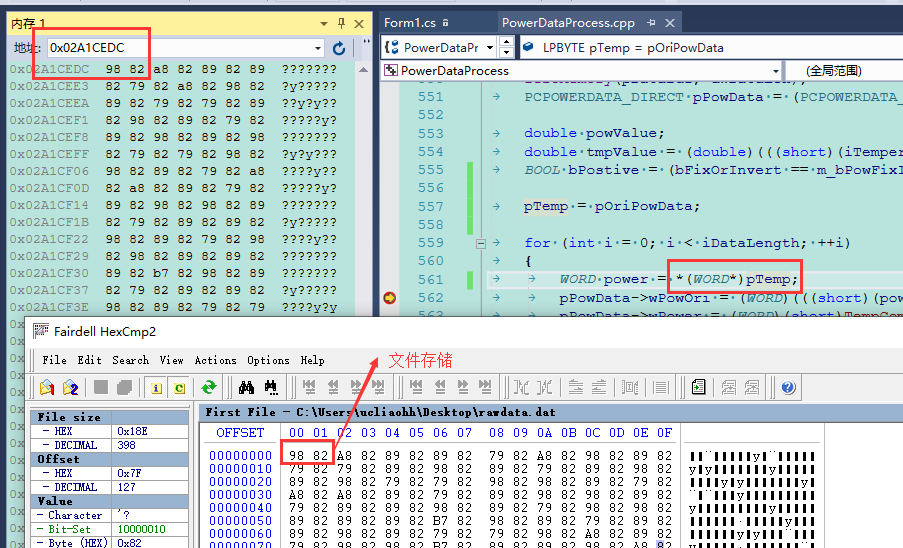

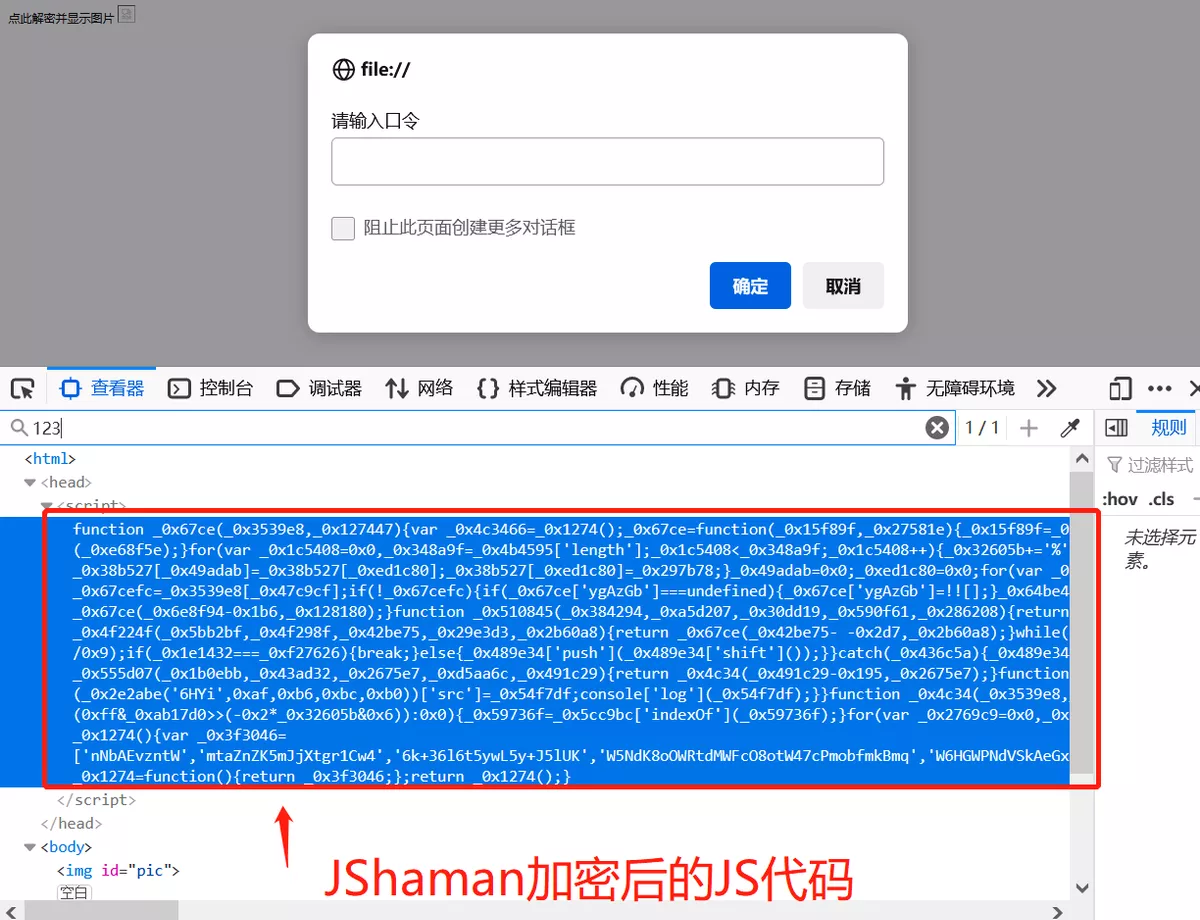

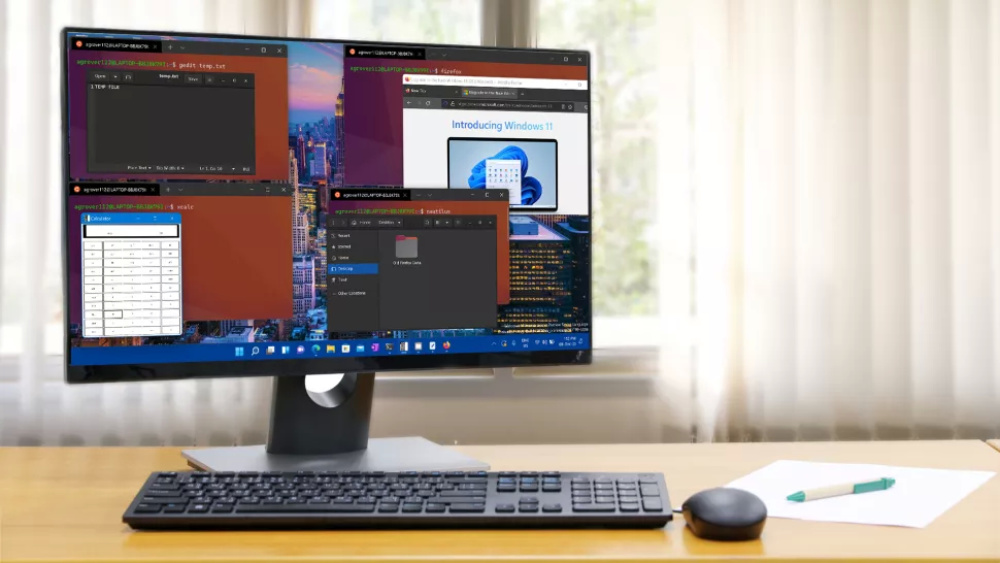

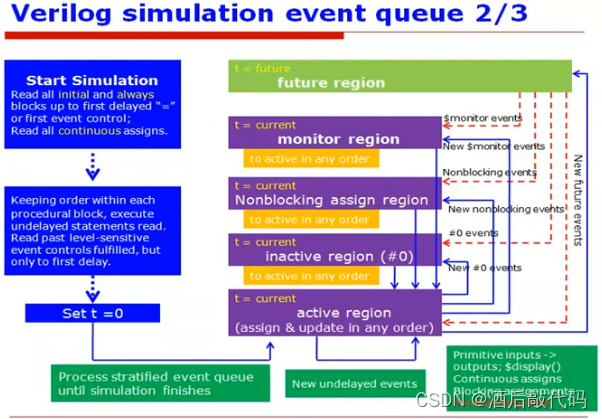

VCS大概的处理Verilog代码的流程:

上述流程在t=0之前,先对一些不存在延时的一些语句进行处理,然后到达t=0时刻,也称为current time。

current time之后开始进入右边五个区:

1)先进入 active region(激活区):在这个区执行一些原语(UDP),简单的与非门、CMOS逻辑、上拉下拉、阻塞赋值、非阻塞赋值的右边表达式等,如右下角介绍。

2)再进入inactive region:主要处理解决延迟问题,

3)接下来进入nonblocking assign region(非阻塞赋值区):主要是对1)中的非阻塞变量赋值,

4)接着monitor region():监测到的是赋值后的新值。

5)最后进入future region:处理一些其他层的操作。

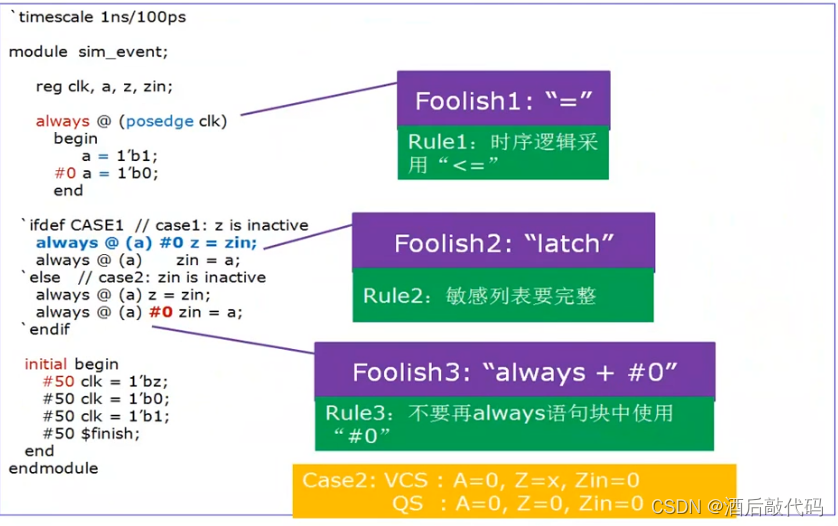

经典案例并解析:

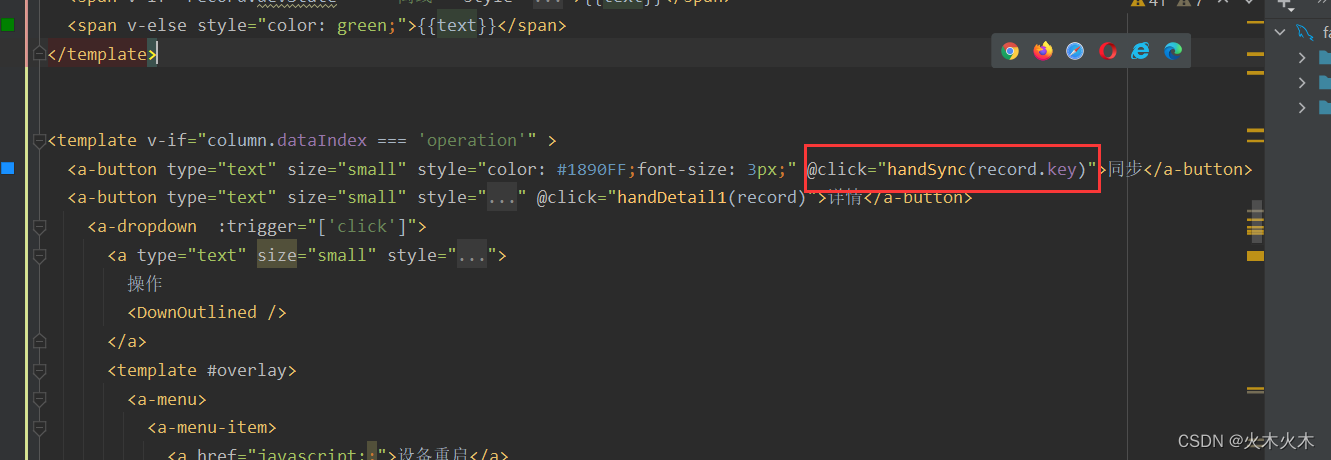

`ifdef ...else...条件编译语句:上图中表述的是如果定义了宏CASE1就执行紧挨着的代码,否则执行else后的代码。

注意:不同的编译器甚至相同软件的不同版本仿真的结果都可能不同。

上述代码中出现的问题总结:

1)寄存器在时许逻辑中的赋值;

2)“#0”操作也不建议在always块中出现,不管always块用于时序逻辑还是组合逻辑;

3)敏感列表书写不全以及信号错误,建议使用always@(*)对组合逻辑中的操作赋值;

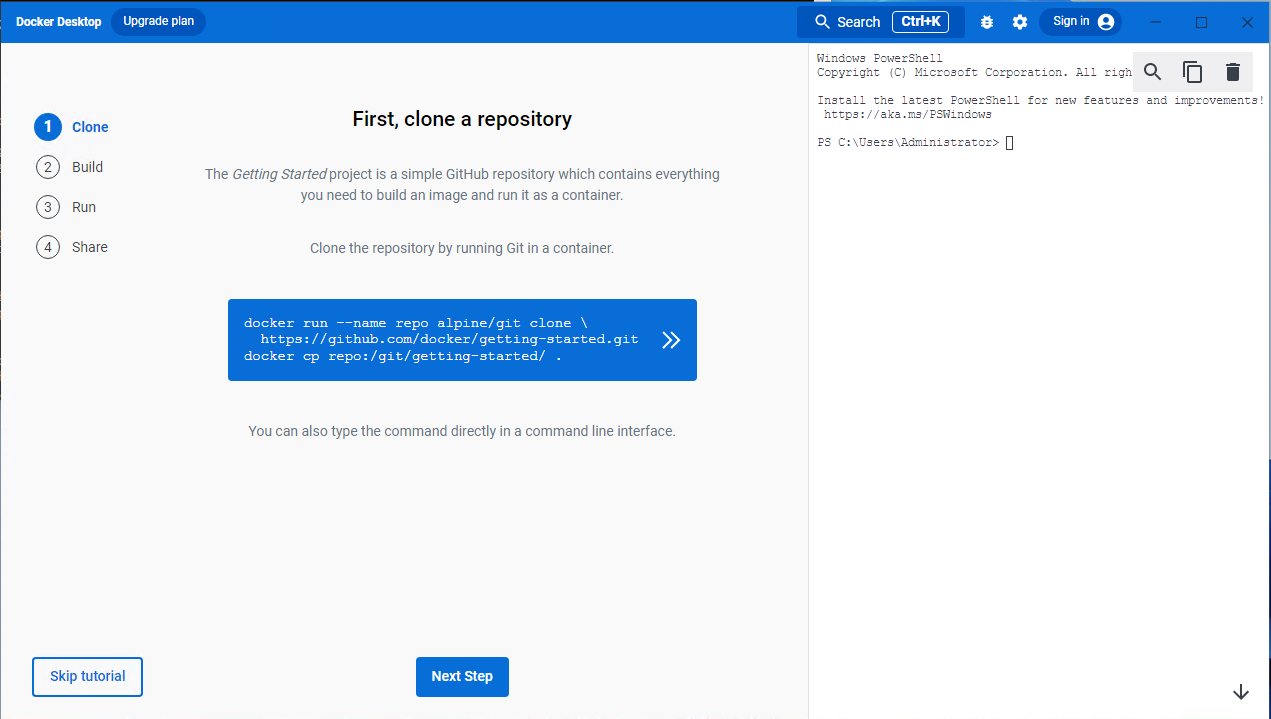

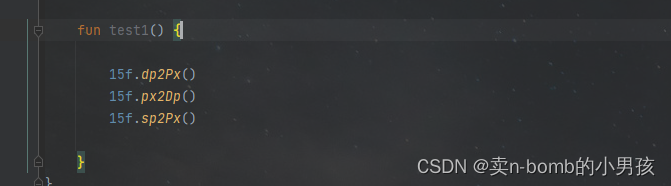

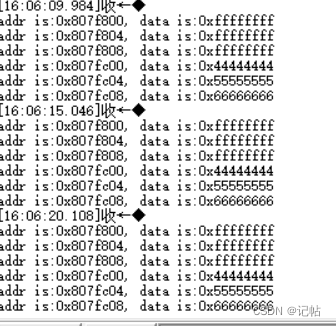

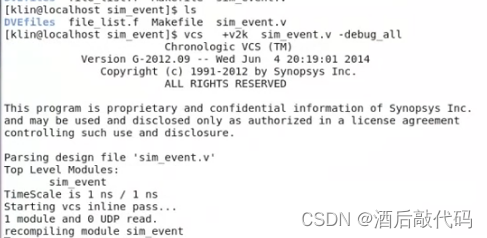

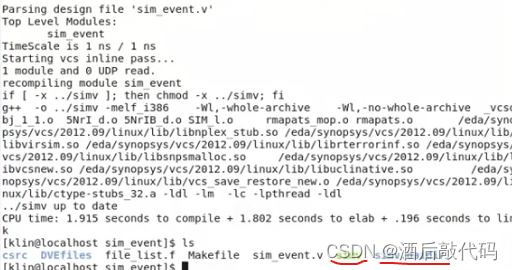

上述代码在VCS中的仿真软件操作流程:

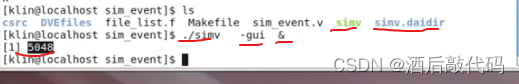

会产生一个simv的二进制可执行文件,编译的过程就是执行这个simv文件。

接着执行二进制执行文件simv,启动DVE,使用GUI,&表示后台执行,5048表示进程号。

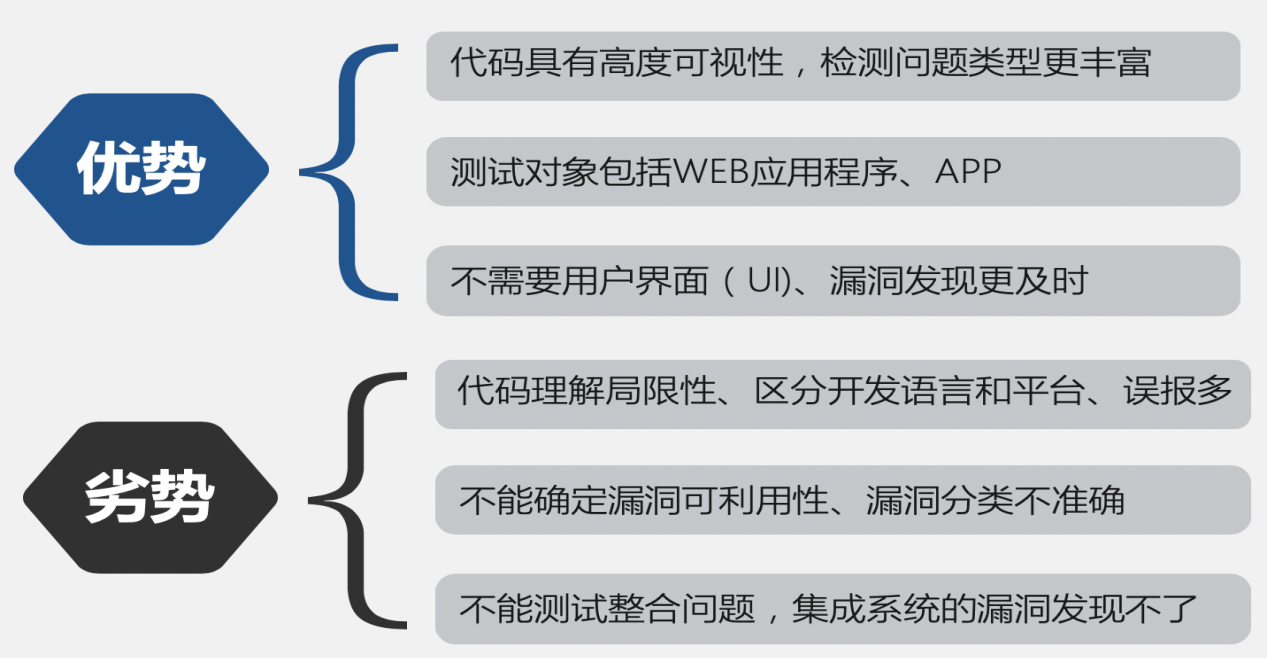

业务要求: