SPI接口简介

SPI是英语Serial Peripheral interface的缩写,顾名思义就是串行外围设备接口。是Motorola首先在其MC68HCXX系列处理器上定义的。

SPI,是一种高递的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,主要应用在EEPROM, FLASH,实时时钟, AD转换器,还有数字信号处理器和数字信号解码器之间。

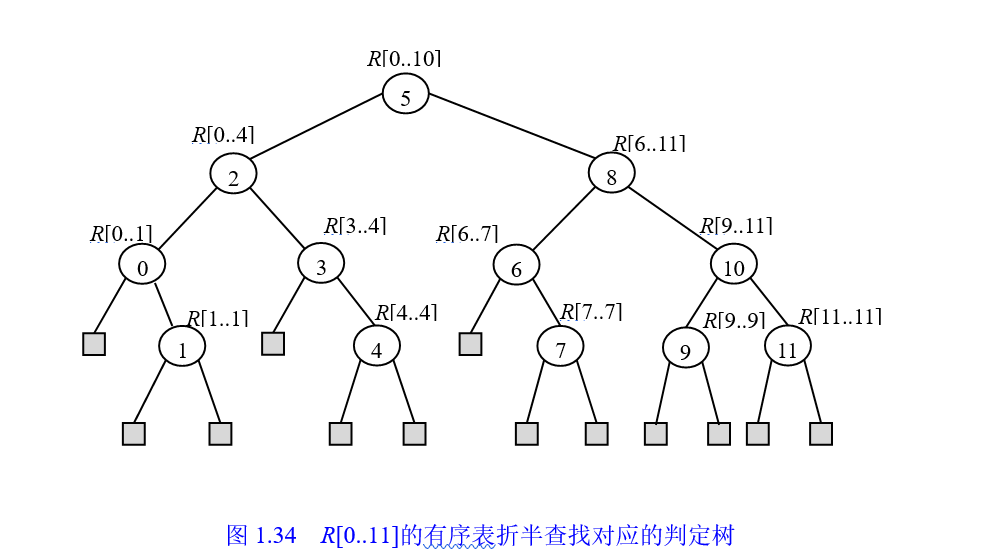

SPI内部结构简明图

MISO主设备输入/从设备输出引脚

MOSI主设备输出/从设备输入引脚

SCLK时钟信号

CS 从设备片选引脚

位移寄存器相当于主机的位移寄存器里面是1000000一个时钟来了后会把最高位位发出去到从机的最低位,然后从机把最高位发到主机的最低位,主机左移一位,最低位接收来自从机寄存器的最高位,每个时钟主机都会发送自己的最高位发出去,从机当第二个时钟周期来之前会左移一位,等待新的一位数据,然后再发给主机的最高位,这样8个时钟周期过去后,2个位移寄存器的值是就互相交换了。

SPI接口框图

SPI工作原理总结

1.硬件上为4根线。

2.主机和从机都有一个串行移位寄存器,主机通过向它的SPI串行寄存器写入一个字节来发起一次传输。

3.串行移位寄存器通过MOSI信号线将字节传送给从机,从机也将自己的串行移位寄存器中的内容通过MISO信号线返回给主机。这样,两个移位寄存器中的内容就被交换。

4.外设的写操作和读操作是同步完成的。如果只进行写操作,主机只需忽略接收到的字节;反之,若主机要读取从机的个字节,就必须发送一个空字节来引发从机的传输。

SPI特征

1..3线全双工同步传输

2.8或16位传输顿格式选择

3.主或从操作支持多主模式

4.8个主模式波特率预分频系数(最大为fpcLk/2)

5.从模式频率(最大为fecLk/2)主模式和从模式的快速通

6.主模式和从模式下均可以由软件或硬件进行NSS管理:主/从操作模式的动态改变

7.可编程的时钟极性和相位可编程的数据顺序, MSB在前或LSB在前

8.可触发中断的专用发送和接收标志

9.SPI总线忙状态标志

10.支持可靠通信的硬件CRC

在发送模式下, CRC值可以被作为最后一个字节发送

在全双工模式中对接收到的最后一个字节自动进行CRC校验

11.可触发中断的主模式故障、过载以及CRC错误标志

12.支持DMA功能的1字节发送和接收缓冲器:产生发送和接受请求

从选择(NSS)脚管理

有2种NSS模式:

软件NSS模式:可以通过设置SPI_CR1寄存器NSSM位来使能这种模式。在这种模式下NSS引脚可以用作它用,而内部NSS信号电平可以通过写SPI_CR1的SSI位来驱动

硬件NSS模式,分两种情况:

1.NSS输出被使能:当STM32 工作为主SPI,并且NSS输出已经通过SPI_CR2寄存器的SSOE位使能,这时NSS引脚被拉低,所有NSS引脚与这个主SPI的NSS引脚相连并配置为硬件NSS的SPI设备,将自动变成从SPI设备。当一个SPI设备需要发送广播数据,它必须拉低NSS信号,以通知所有其它的设备它是主设备;如果它不能拉低NSS,这意味着总线上有另外一个主设备在通信,这时将产生一个硬件失败错误(Hard Fault)。

2.NSS输出被关闭:允许操作于多主环环境

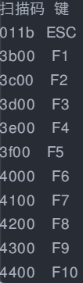

时钟信号的CPHA相位和CPOL极性

SPI_CR寄存器的CPOL和CPHA位,能够组合成四种可能的时序关系。CPOL(时钟极性)位控制在没有数据传输时时钟的空闲状态电平,此位对主模式和从模式下的设备都有效。如果CPOL被清'0', SCK引脚在空闲状态保持低电平;如果CPOL被置'1', SCK引脚在空闲状态保持高电平。如果CPHA(时钟相位)位被置'1', SCK时钟的第二个边沿(CPOL位为0时就是下降沿, CPOL位为'1'时就是上升沿)进行数据位的采样,数据在第二个时钟边沿被锁存。如果CPHA位被清'O',SCK时钟的第一边沿(CPOL位为'O'时就是下降沿,CPOL位为'1'时就是上升沿)进行数据位采样,数据在第一个时钟边沿被锁存。CPOL时钟极性和CPHA时钟相位的组合选择数据捕捉的时钟边沿。

CPOL是设置没有数据时时钟空闲状态电平,CPHA是设置第几个边沿被采集。

CPOL = 1 时钟空闲状态是低电平CPHA =1 时是第二个边沿被采集,所以就是上升沿采集

CPOL = 0 时钟空闲状态是高电平CPHA =1 时是第二个边沿被采集,所以就是下升沿采集

CPOL = 1 时钟空闲状态是低电平CPHA =0 时是第一个边沿被采集,所以就是下升沿采集

CPOL = 0 时钟空闲状态是高电平CPHA =0 时是第一个边沿被采集,所以就是上升沿采集

数据帧格式

根据SPI_CR1寄存器中的LSBFIRST位,输出数据位时可以MSB在先也可以LSB在先。根据SPI_CR1寄存器的DFF位,每个数据顿可以是8位或是16位。所选择的数据顿格式对发送和/或接收都有效。

状态标志

应用程序通过3个状态标志可以完全监控SPI总线的状态。

发送缓冲器空闲标志(TXE)

此标志为'1'时表明发送缓冲器为空,可以写下一个待发送的数据进入缓冲器中。当写入SPI_DR时,TXE标志被清除。

接收缓冲器非空(RXNE)

此标志为'1'时表明在接收缓冲器中包含有效的接收数据。读SPI数据寄存器可以清除此标志。忙(Busy)标志

BSY标志由硬件设置与清除(写入此位无效果),此标志表明SPI通信层的状态。

SPI中断

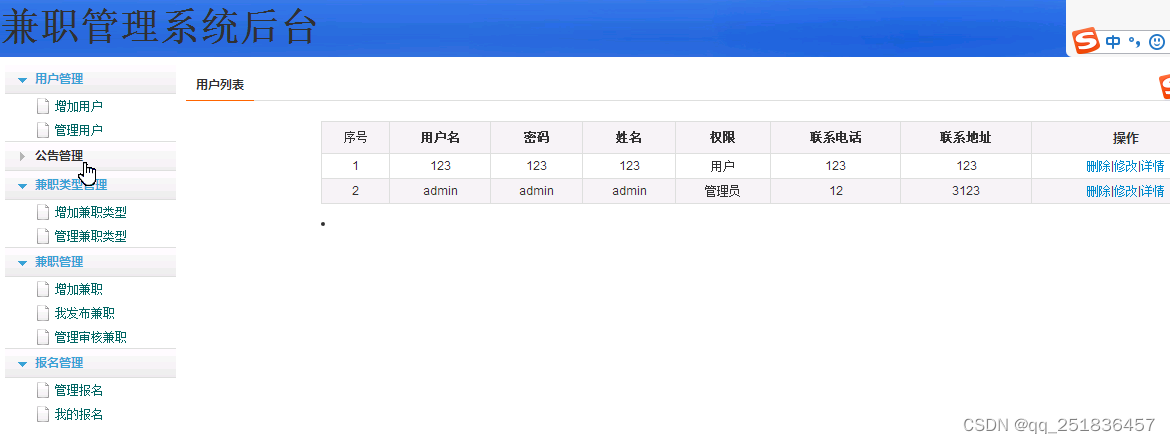

SPI引脚配置

程序配置过程

1.配置相关引脚的复用功能,使能SPlx时钟

void GPIO Init(GPIO_TypeDef* GPIOx, GPIO InitTypeDef* GPIO_InitStruct);2.初始化SPIx,设置SPIx工作模式

void SPI_Init(SPL TypeDef* SPIx, SPI Init TypeDef* SPL InitStruct);3.使能SPIx

void SPI Cmd(SPI TypeDef* SPIx, FunctionalState NewState);4.SPI传输数据

void SPI_I2S_SendData(SPITypeDef* SPIx, uint16 Data);

uint16 SPI_I2S_ReceiveData(SPI TypeDef* SPlx);5.查看SPI传输状态

SPI_I2S_GetFlagStatus(SPI2, SPI_2S FLAGRXNE);

![[附源码]计算机毕业设计基于web的羽毛球管理系统Springboot程序](https://img-blog.csdnimg.cn/e83325d0fd36455c8d3bc89b246709e5.png)