RISCV - 2 “Zicsr“, CSR Instructions

- 1 CSR Instructions

- 2 CSR Access Ordering

- 3 CSR指令集类型

CSR:Control and Status Register

RISCV - 1 RV32/64G指令集清单

RISC-V defines a separate address space of 4096 Control and Status registers associated with each hart. This chapter defines the full set of CSR instructions that operate on these CSRs.

RISC-V 定义了由 4096 个控制和状态寄存器组成的独立地址空间,这些寄存器与每个 Hart 相关联。本章定义了在这些 CSR 上运行的全套 CSR 指令。

Note:

While CSRs are primarily used by the privileged architecture, there are several uses in unprivileged code including for counters and timers, and for floating-point status.

虽然 CSR 主要由特权架构使用,但在非特权代码中也有一些用途,包括计数器和定时器以及浮点状态。

The counters and timers are no longer considered mandatory parts of the standard base ISAs

计数器和定时器不再被视为标准基本 ISA 的必备部分。

1 CSR Instructions

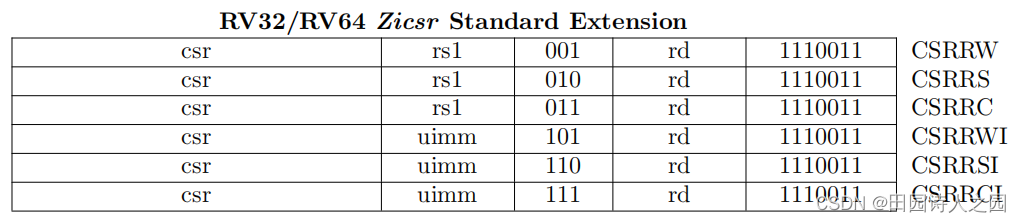

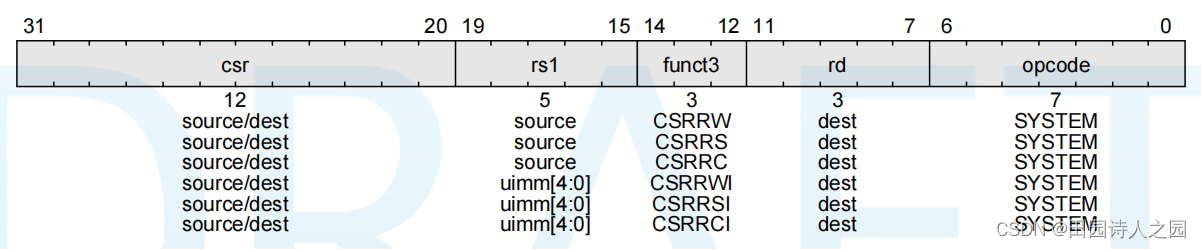

All CSR instructions atomically read-modify-write a single CSR, whose CSR specifier is encoded in the 12-bit csr field of the instruction held in bits 31-20. The immediate forms use a 5-bit zero-extended immediate encoded in the rs1 field.

所有 CSR 指令都以原子方式读取-修改-写入单个 CSR,其 CSR 指示符在指令的 12 位 csr 字段中编码,该字段位在 31-20 位。立即数形式使用 rs1 字段编码的 5 位零扩展立即数编码。

The CSRRW (Atomic Read/Write CSR) instruction atomically swaps values in the CSRs and integer registers. CSRRW reads the old value of the CSR, zero-extends the value to XLEN bits, then writes it to integer register rd. The initial value in rs1 is written to the CSR. If rd=x0, then the instruction shall not read the CSR and shall not cause any of the side effects that might occur on a CSR read.

CSRRW(原子读/写 CSR)指令原子交换 CSR 和整数寄存器Rd中的值。CSRRW 读取 CSR 的旧值,将其零扩展到 XLEN 位,然后写入整数寄存器 rd。rs1 中的初始值被写入 CSR。如果 rd=x0,则指令不会读取 CSR,也不会导致读取 CSR 时可能出现的任何副作用。

The CSRRS (Atomic Read and Set Bits in CSR) instruction reads the value of the CSR, zero-extends the value to XLEN bits, and writes it to integer register rd. The initial value in integer register rs1 is treated as a bit mask that specifies bit positions to be set in the CSR. Any bit that is high in rs1 will cause the corresponding bit to be set in the CSR, if that CSR bit is writable. Other bits in the CSR are not explicitly written.

CSRRS(原子读取并设置 CSR 中的位数)指令读取 CSR 的值,将其零扩展到 XLEN 位,并写入整数寄存器 rd。整数寄存器 rs1 中的初始值被视为位掩码,用于指定 CSR 中要设置的位位置。如果 CSR 位可写,rs1 中的任何高位都将导致 CSR 中的相应位被设置。CSR 中的其他位不会被明确写入。

The CSRRC (Atomic Read and Clear Bits in CSR) instruction reads the value of the CSR, zero-extends the value to XLEN bits, and writes it to integer register rd. The initial value in integer register rs1 is treated as a bit mask that specifies bit positions to be cleared in the CSR. Any bit that is high in rs1 will cause the corresponding bit to be cleared in the CSR, if that CSR bit is writable. Other bits in the CSR are not explicitly written.

CSRRC(原子读取并清除 CSR 中的位数)指令读取 CSR 的值,将其零扩展到 XLEN 位,并写入整数寄存器 rd。整数寄存器 rs1 中的初始值被视为位掩码,用于指定 CSR 中要清除的位位置。如果 CSR 位可写,rs1 中的任何高位都将导致 CSR 中相应位被清零。CSR 中的其他位不会被明确写入。

For both CSRRS and CSRRC, if rs1=x0, then the instruction will not write to the CSR at all, and so shall not cause any of the side effects that might otherwise occur on a CSR write, nor raise illegal instruction exceptions on accesses to read-only CSRs. Both CSRRS and CSRRC always read the addressed CSR and cause any read side effects regardless of rs1 and rd fields. Note that if rs1 specifies a register holding a zero value other than x0, the instruction will still attempt to write the unmodified value back to the CSR and will cause any attendant side effects. A CSRRW with rs1=x0 will attempt to write zero to the destination CSR.

对于 CSRRS 和 CSRRC,如果 rs1=x0,则指令根本不会写入 CSR,因此不会导致 CSR 写入时可能出现的任何副作用,也不会在访问只读 CSR 时引发非法指令异常。无论 rs1 和 rd 字段如何,CSRRS 和 CSRRC 始终会读取寻址的 CSR 并产生任何读取副作用。需要注意的是,如果 rs1 指定的寄存器除 x0 外的值为零,该指令仍将尝试将未修改的值写回 CSR,并会导致任何相应的副作用。rs1=x0 的 CSRRW 将尝试向目标 CSR 写入零值。

The CSRRWI, CSRRSI, and CSRRCI variants are similar to CSRRW, CSRRS, and CSRRC respectively, except they update the CSR using an XLEN-bit value obtained by zero-extending a 5-bit unsigned immediate (uimm[4:0]) field encoded in the rs1 field instead of a value from an integer register. For CSRRSI and CSRRCI, if the uimm[4:0] field is zero, then these instructions will not write to the CSR, and shall not cause any of the side effects that might otherwise occur on a CSR write, nor raise illegal instruction exceptions on accesses to read-only CSRs. For CSRRWI, if rd=x0, then the instruction shall not read the CSR and shall not cause any of the side effects that might occur on a CSR read. Both CSRRSI and CSRRCI will always read the CSR and cause any read side effects regardless of rd and rs1 fields.

CSRRWI、CSRRSI 和 CSRRCI 变体分别与 CSRRW、CSRRS 和 CSRRC 类似,但它们更新 CSR 时使用的是通过将 rs1 字段中编码的 5 位无符号立即值(uimm[4:0])字段置零而获得的 XLEN 位值,而不是整数寄存器中的值。对于 CSRRSI 和 CSRRCI,如果 uimm[4:0] 字段为零,则这些指令不会写入 CSR,也不会导致 CSR 写入时可能出现的任何副作用,也不会在访问只读 CSR 时引发非法指令异常。对于 CSRRWI,如果 rd=x0,则指令不会读取 CSR,也不会导致读取 CSR 时可能出现的任何副作用。CSRRSI 和 CSRRCI 将始终读取 CSR 并导致任何读取副作用,与 rd 和 rs1 字段无关。

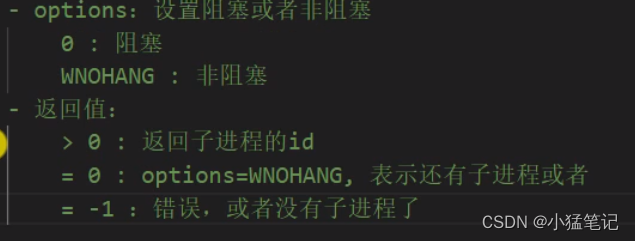

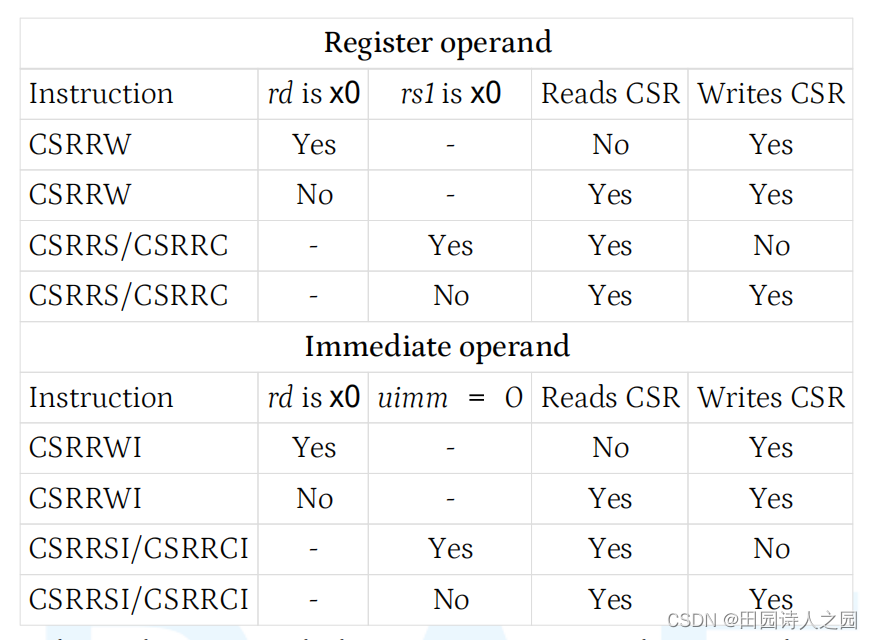

Conditions determining whether a CSR instruction reads or writes the specified CSR:

决定 CSR 指令读取或写入指定 CSR 的条件

Table summarizes the behavior of the CSR instructions with respect to whether they read and/or write the CSR.

表中总结了 CSR 指令在读取和/或写入 CSR 时的行为。

For any event or consequence that occurs due to a CSR having a particular value, if a write to the CSR gives it that value, the resulting event or consequence is said to be an indirect effect of the write. Indirect effects of a CSR write are not considered by the RISC-V ISA to be side effects of that write.

对于因 CSR 具有特定值而产生的任何事件或后果,如果对 CSR 的写入使其具有该值,则所产生的事件或后果被称为写入的间接影响。RISC-V ISA 不会将 CSR 写入的间接影响视为写入的副作用。

Note:

An example of side effects for CSR accesses would be if reading from a specific CSR causes a light bulb to turn on, while writing an odd value to the same CSR causes the light to turn off. Assume writing an even value has no effect. In this case, both the read and write have side effects controlling whether the bulb is lit, as this condition is not determined solely from the CSR value. (Note that after writing an odd value to the CSR to turn off the light, then reading to turn the light on, writing again the same odd value causes the light to turn off again. Hence, on the last write, it is not a change in the CSR value that turns off the

light.)

访问 CSR 副作用的一个例子是,如果从特定 CSR 读取会导致灯泡打开,而向同一 CSR 写入奇数值会导致灯泡熄灭。假设写入偶数值没有影响。在这种情况下,读取和写入都会产生控制灯泡是否点亮的副作用,因为这一条件并不完全由 CSR 值决定。(请注意,向 CSR 写入奇数值关灯后,再读取奇数值开灯,再次写入相同的奇数值会导致灯再次熄灭。因此,在最后一次写入时,并不是 CSR 值的变化使灯熄灭。

On the other hand, if a bulb is rigged to light whenever the value of a particular CSR is odd, then turning the light on and off is not considered a side effect of writing to the CSR but merely an indirect effect of such writes.

另一方面,如果在某个 CSR 的值为奇数时安装一个灯泡,那么灯的亮与灭并不被认为是写入 CSR 的副作用,而只是写入 CSR 的间接作用。

More concretely, the RISC-V privileged architecture defined in Volume II specifies that certain combinations of CSR values cause a trap to occur. When an explicit write to a CSR creates the conditions that trigger the trap, the trap is not considered a side effect of the write but merely an indirect effect.

更具体地说,第二卷中定义的 RISC-V 特权架构规定,CSR 值的某些组合会导致陷阱发生。当对 CSR 的显式写入产生了触发陷阱的条件时,陷阱并不被视为写入的副作用,而只是一种间接影响。

Standard CSRs do not have any side effects on reads. Standard CSRs may have side effects on writes. Custom extensions might add CSRs for which accesses have side effects on either reads or writes.

标准 CSR 对读取没有任何副作用。标准 CSR 可能会对写入产生副作用。自定义扩展可能会添加对读取或写入都有副作用的 CSR。

Some CSRs, such as the instructions-retired counter, instret, may be modified as side effects of instruction execution. In these cases, if a CSR access instruction reads a CSR, it reads the value prior to the execution of the instruction. If a CSR access instruction writes such a CSR, the write is done instead of the increment. In particular, a value written to instret by one instruction will be the value read by the following instruction.

某些 CSR(如指令退役计数器 instret)可能会因指令执行的副作用而被修改。在这种情况下,如果 CSR 访问指令读取 CSR,则会在指令执行前读取该值。如果 CSR 存取指令写入这样的 CSR,则是写入而不是递增。特别是,一条指令写入 instret 的值将成为下一条指令读取的值。

The assembler pseudoinstruction to read a CSR, CSRR rd, csr, is encoded as CSRRS rd, csr, x0. The assembler pseudoinstruction to write a CSR, CSRW csr, rs1, is encoded as CSRRW x0, csr, rs1, while CSRWI csr, uimm, is encoded as CSRRWI x0, csr, uimm.

读取 CSR 的汇编伪指令 CSRR rd, csr 编码为 CSRRS rd, csr, x0。写入 CSR 的汇编伪指令 CSRW csr, rs1 编码为 CSRRW x0, csr, rs1,而 CSRWI csr, uimm 编码为 CSRRWI x0, csr, uimm。

Further assembler pseudoinstructions are defined to set and clear bits in the CSR when the old value is not required: CSRS/CSRC csr, rs1; CSRSI/CSRCI csr, uimm.

此外,还定义了一些汇编伪指令,用于在不需要旧值时设置和清除 CSR 中的位: CSRS/CSRC csr、rs1;CSRSI/CSRCI csr、uimm。

2 CSR Access Ordering

Each RISC-V hart normally observes its own CSR accesses, including its implicit CSR accesses, as performed in program order. In particular, unless specified otherwise, a CSR access is performed after the execution of any prior instructions in program order whose behavior modifies or is modified by the CSR state and before the execution of any subsequent instructions in program order whose behavior modifies or is modified by the CSR state. Furthermore, an explicit CSR read returns the CSR state before the execution of the instruction, while an explicit CSR write suppresses and overrides any implicit writes or modifications to the same CSR by the same instruction.

每个 RISC-V hart 通常按照程序顺序执行自己的 CSR 访问,包括隐式 CSR 访问。具体而言,除非另有规定,否则 CSR 访问是在执行程序顺序中任何其行为修改或被 CSR 状态修改的先前指令之后,以及执行程序顺序中任何其行为修改或被 CSR 状态修改的后续指令之前进行的。此外,显式 CSR 读取会在指令执行前返回 CSR 状态,而显式 CSR 写入会抑制和覆盖同一指令对同一 CSR 的任何隐式写入或修改。

Likewise, any side effects from an explicit CSR access are normally observed to occur synchronously in program order. Unless specified otherwise, the full consequences of any such side effects are observable by the very next instruction, and no consequences may be observed out-of-order by preceding instructions. (Note the distinction made earlier between side effects and indirect effects of CSR writes.)

同样,显式 CSR 访问产生的任何副作用通常都会按程序顺序同步发生。除非另有规定,否则任何此类副作用的全部后果都可以在下一条指令中观察到,而前面的指令则不能观察到任何非顺序后果。(注意前面对 CSR 写入的副作用和间接影响所做的区分)。

For the RVWMO memory consistency model (Chapter 17), CSR accesses are weakly ordered by default, so other harts or devices may observe CSR accesses in an order different from program order. In addition, CSR accesses are not ordered with respect to explicit memory accesses, unless a CSR access modifies the execution behavior of the instruction that performs the explicit memory access or unless a CSR access and an explicit memory access are ordered by either the syntactic dependencies defined by the memory model or the ordering requirements defined by the Memory-Ordering PMAs section in Volume II of this manual. To enforce ordering in all other cases, software should execute a FENCE instruction between the relevant accesses. For the purposes of the FENCE instruction, CSR read accesses are classified as device input (I), and CSR write accesses are classified as device output (O).

对于 RVWMO 内存一致性模型(第 17 章),默认情况下 CSR 访问是弱排序的,因此其他 Harts 或设备可能会观察到 CSR 访问的顺序与程序顺序不同。此外,除非 CSR 访问修改了执行显式内存访问的指令的执行行为,或者 CSR 访问和显式内存访问根据内存模型定义的语法依赖关系或本手册第二卷内存排序 PMA 部分定义的排序要求排序,否则 CSR 访问相对于显式内存访问不排序。为了在所有其他情况下执行排序,软件应在相关访问之间执行 FENCE 指令。就 FENCE 指令而言,CSR 读取访问被归类为设备输入 (I),CSR 写入访问被归类为设备输出 (O)。

Note:

Informally, the CSR space acts as a weakly ordered memory-mapped I/O region, as defined by the Memory-Ordering PMAs section in Volume II of this manual. As a result, the order of CSR accesses with respect to all other accesses is constrained by the same mechanisms that constrain the order of memory-mapped I/O accesses to such a region.

正如本手册第二卷 "内存排序 PMA "部分所定义的那样,CSR 空间是一个弱排序的内存映射 I/O 区域。因此,相对于所有其他访问,CSR 访问的顺序受制于限制内存映射 I/O 访问顺序的相同机制。

These CSR-ordering constraints are imposed to support ordering main memory and memory-mapped I/O accesses with respect to CSR accesses that are visible to, or affected by, devices or other harts. Examples include the time, cycle, and mcycle CSRs, in addition to CSRs that reflect pending interrupts, like mip and sip. Note that implicit reads of such CSRs (e.g., taking an interrupt because of a change in mip) are also ordered as device input.

实施这些 CSR 排序约束,是为了支持对主存储器和内存映射 I/O 访问进行排序,使其与设备或其他硬件可见或受其影响的 CSR 访问保持一致。例如时间、周期和 mcycle CSR,以及反映待处理中断的 CSR,如 mip 和 sip。需要注意的是,对此类 CSR 的隐式读取(例如,因 mip 发生变化而进行中断)也会被排序为设备输入。

Most CSRs (including, e.g., the fcsr) are not visible to other harts; their accesses can be freely reordered in the global memory order with respect to FENCE instructions without violating this specification.

大多数 CSR(包括 fcsr 等)对其他 harts 都是不可见的;它们的访问可以根据 FENCE 指令在全局内存中自由重新排序,而不会违反本规范。

The hardware platform may define that accesses to certain CSRs are strongly ordered, as defined by the Memory-Ordering PMAs section in Volume II of this manual. Accesses to strongly ordered CSRs have stronger ordering constraints with respect to accesses to both weakly ordered CSRs and accesses to memory-mapped I/O regions.

根据本手册第二卷 "内存排序 PMA "部分的定义,硬件平台可定义对某些 CSR 的访问为强排序。与访问弱排序 CSR 和访问内存映射 I/O 区域相比,访问强排序 CSR 具有更强的排序约束。

3 CSR指令集类型