本文介绍Image Sensor的FSIN/VSYNC。

产品开发过程(比如3D成像)中,有时会遇到需要2个及以上的Image Sensor同步采集,因此,Image Sensor厂家对于他们的产品都提供了同步功能,也就是我们经常所见的FSIN/VSYNC(OV),XVS(Sony IMX3系列)引脚,这里提一下,对于Sony的IMX2系列是通过控制XVS和XHS来实现同步采集的(通常会使用FPGA去采)。

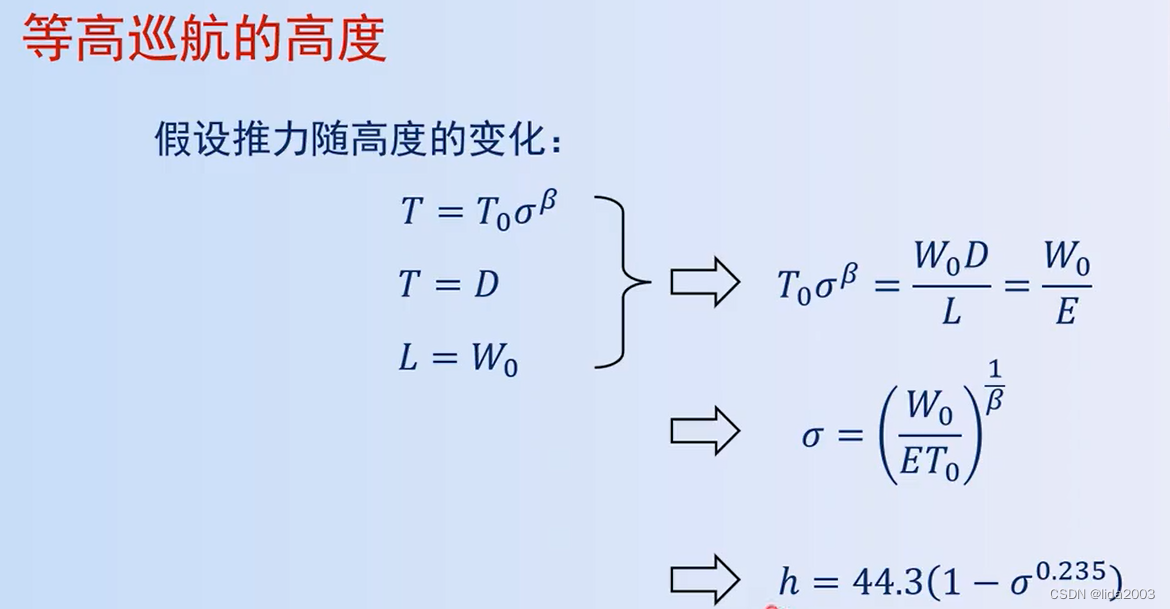

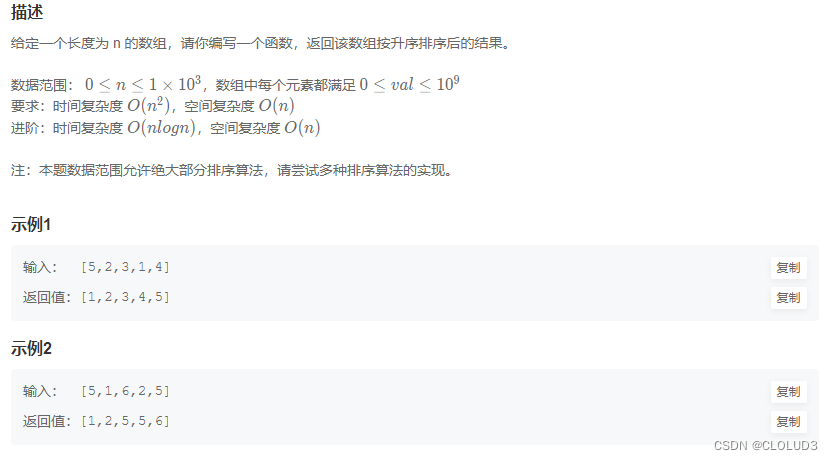

1.工作原理

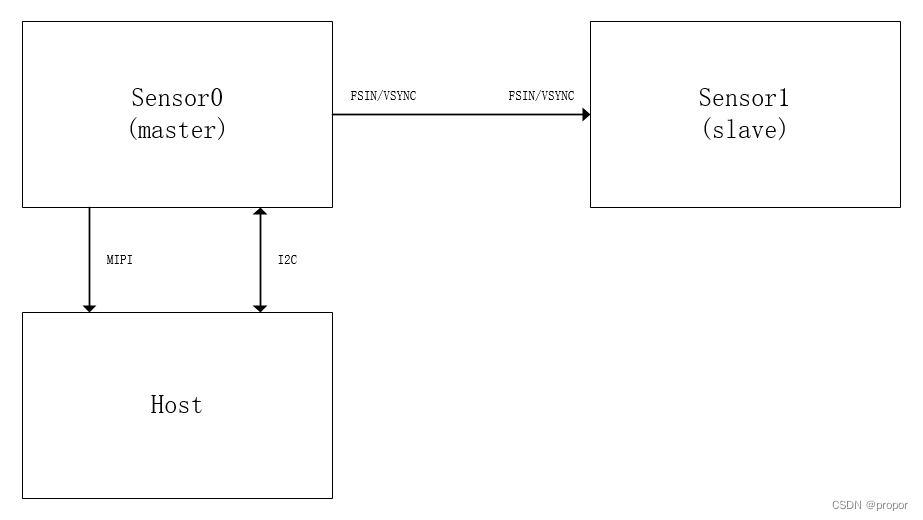

想要实现2个Image Sensor同步采集,主要有2种方式,如下图,Host通常为SoC或FPGA,图中省略了Host和Sensor1的MIPI和I2C连接(不太好画),实际连接和Sennsor0的是一样的。

1)方式1

方式1是各厂家推荐的同步方式,Sensor0配置为master模式(FSIN/VSYNC为输出),sensor1配置为slave模式(FSIN/VSYNC为输入),因Host在启动图像采集时,Sensor0会先发VSYNC(内部信号),然后启动数据采集,这里将VSYNC信号通过FSIN/VSYNC输出,而Sensor1的FSIN/VSYNC作为输入,并受此引脚控制,这样就实现2路Image Sensor图像的同步采集。

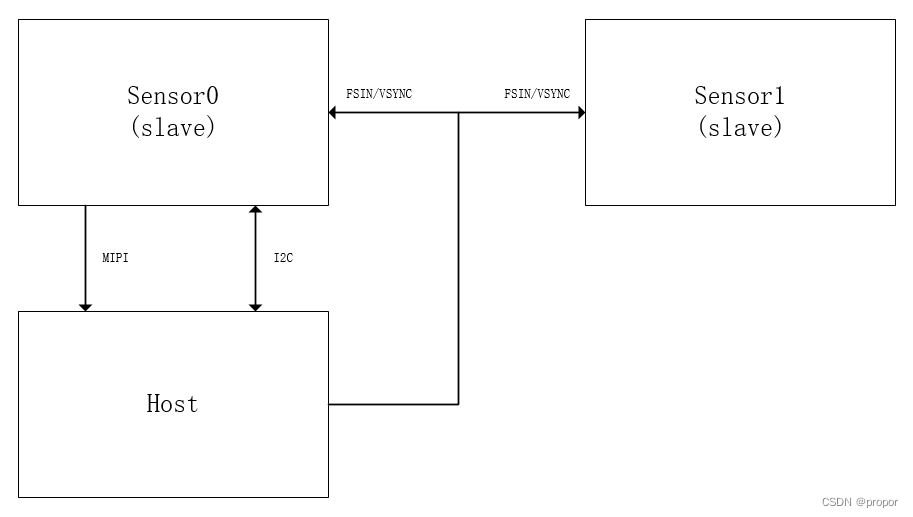

2)方式2

方式2,同时将2路Sensor配置为Slave模式(FSIN/VSYNC为输入),这样它们内部的数据采集就由Host完全控制了,按相应的时序要求在FSIN/VSYNC引脚上输出VSYNC信号,2个Sensor就采集一帧图像。

上面只是简单介绍了下工作原理,实际上还涉及到FSIN/VSYNC相关时序的修改,比如对于模式0,可以使Sensor0的FSIN/VSYNC延迟触发Sensor1的图像采集,以达到想要的功能。

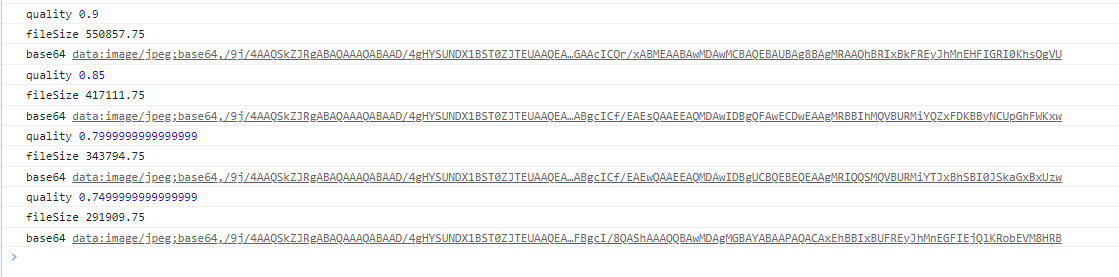

2.涉及寄存器修改

这里以OV的FSIN/VSYNC寄存器修改为例,简单介绍下如何配置,至于相应的时序配置,这里就不详细介绍了,Sony的IM3系列配置类似。

1)配置FSIN/VSYNC

![]()

master:配置VSYNC output enable为输出

slave:配置VSYNC output enable为输入

2)使能外部FSIN/VSYNC

master:配置ext_vs_en为禁能

slave:配置ext_vs_en为使能,即VSYNC由外部FSIN/VSYNC来进行控制

总结,本文介绍了Image Sensor同步采集的2种方法及工作原理,并简单介绍了下相关寄存器的配置。