功耗影响

便携性

功耗越低,同等电量下电子产品工作时间越长,便携性设备的电池容量和体积设计的困难度也会降低。例如,手机越做越薄,性能还不受影响,就是因为低功耗设计发挥了至关重要的作用。

性能

功耗越大,耗能越多,产生的热量越多,各器件的工作性能就会受到影响。例如,手机使用时间较长时,会感觉手机发热,而且各应用软件也会出现卡顿的现象。

成本

不考虑低功耗设计时,一个功能的实现方法可能较为繁琐,实现的器件增多,产品面积增大;同时,功耗过大时,就要考虑散热装置,这又增加了组装成本。 总之,低功耗设计有很多的优点,也是以后数字设计的发展趋势。

功耗类型

功耗类型一般可分为动态功耗、静态功耗和浪涌功耗。

浪涌电流:

指器件上电时产生的最大瞬时输入电流,称为启动电流;浪涌电流与设备相关;

浪涌功耗不是我们需要关注的地方,因此这里只是说明有这个功耗存在。

静态功耗:也称待机功耗,静态功耗主要由晶体管的漏电流所导致的功耗;

动态功耗:包括开关功耗或者称为翻转功耗、短路功耗或者称为内部功耗。

动态功耗影响因素:门寄生电容、时钟翻转率、时钟频率、供电电压;

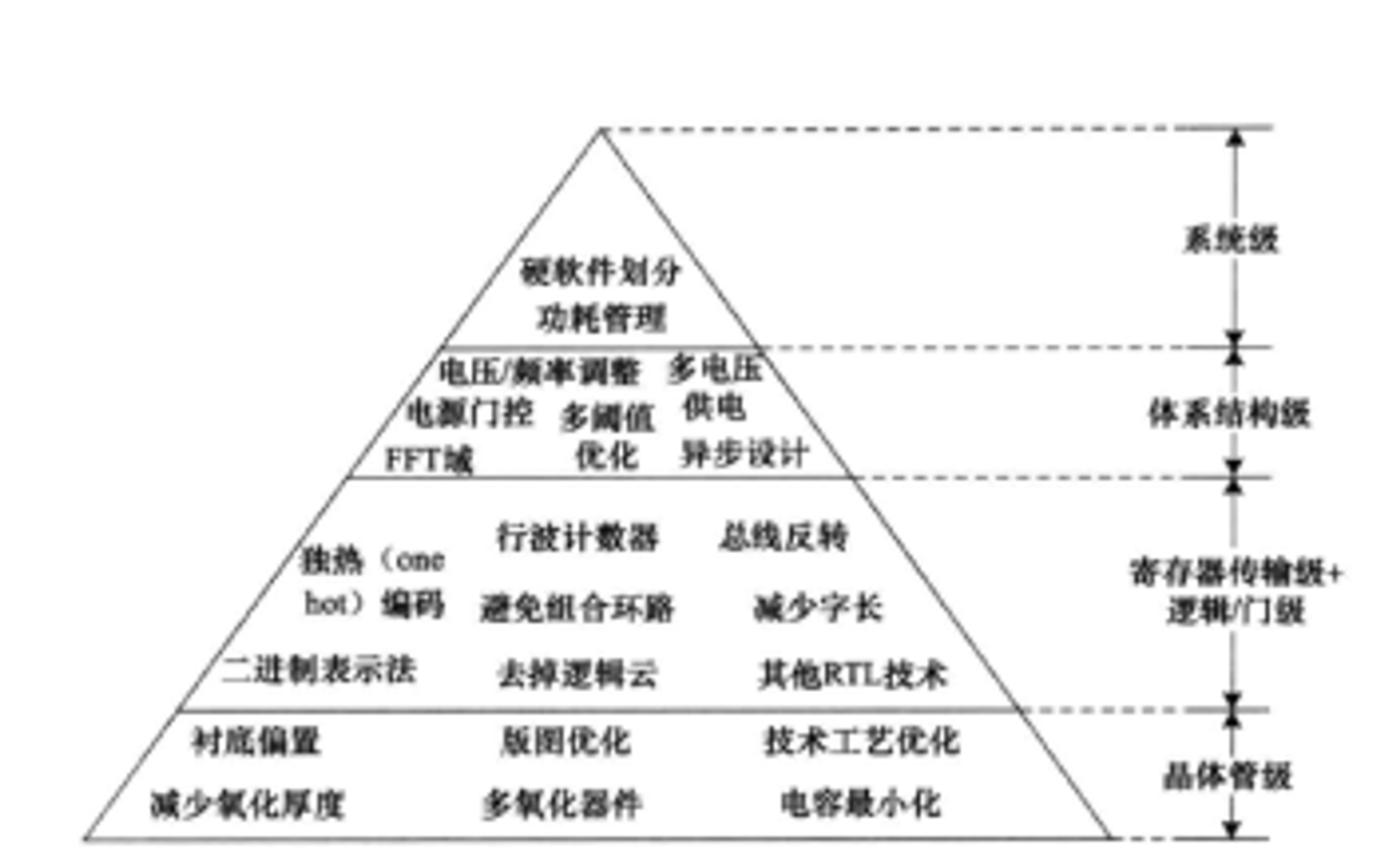

降低功耗:应当在所有设计层次上进行,即系统级、逻辑级和物理级,层次越高对功耗降低越有效;

在系统和体系结构级可以达到最大的降低效果;

下表显示了在数字设计的各个层次上可减少功耗的百分比。RTL 级之后,功耗的减少量已经非常有限。

| 设计层次 | 改善程度 |

|---|---|

| 系统级 | 50% ~ 90% |

| RTL 级 | 20% ~ 50% |

| 门级 | 10% ~ 15% |

| 晶体管级 | 5% ~ 10% |

| 版图级 | < 5% |

低功耗设计

系统级降低功耗技术

- 片上系统方法

- 硬件/软件划分:对系统性能进行仿真建模,决定哪一部分使用硬件来实现,哪一部分使用软件来实现,从而达到性能和功耗最佳平衡

- 使用低功耗软件

- 选择合适的处理器

- ip 或单元库选择

体系结构级降低功耗技术:

- 多电压设计技术(Multi-VDD):

包括电压控制单元:

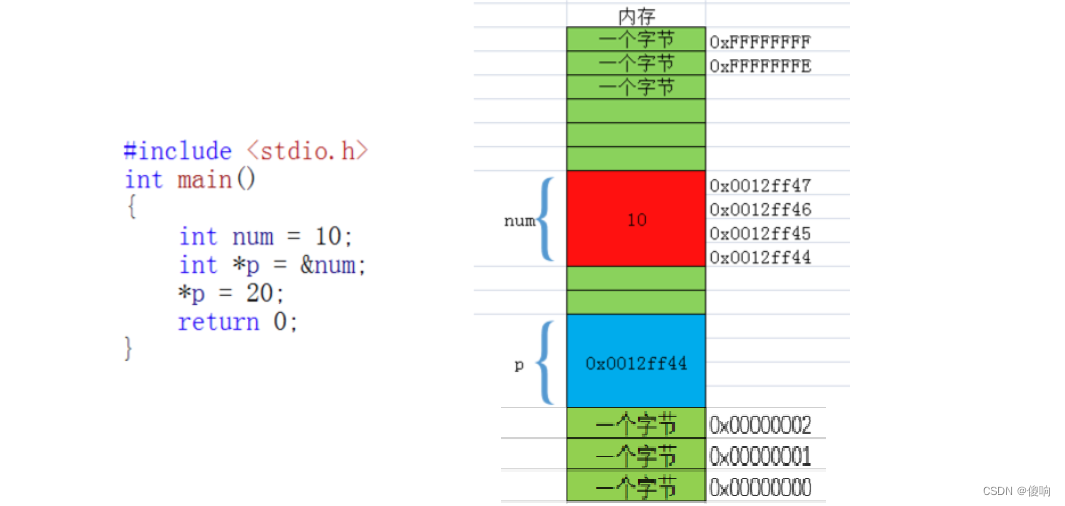

电平转换器(level shifter):把高(低)电压区域的信号转换到低(高)电压区域。信号通常包括数据、时钟、扫描链数据等。电平转换器的示意图如下所:

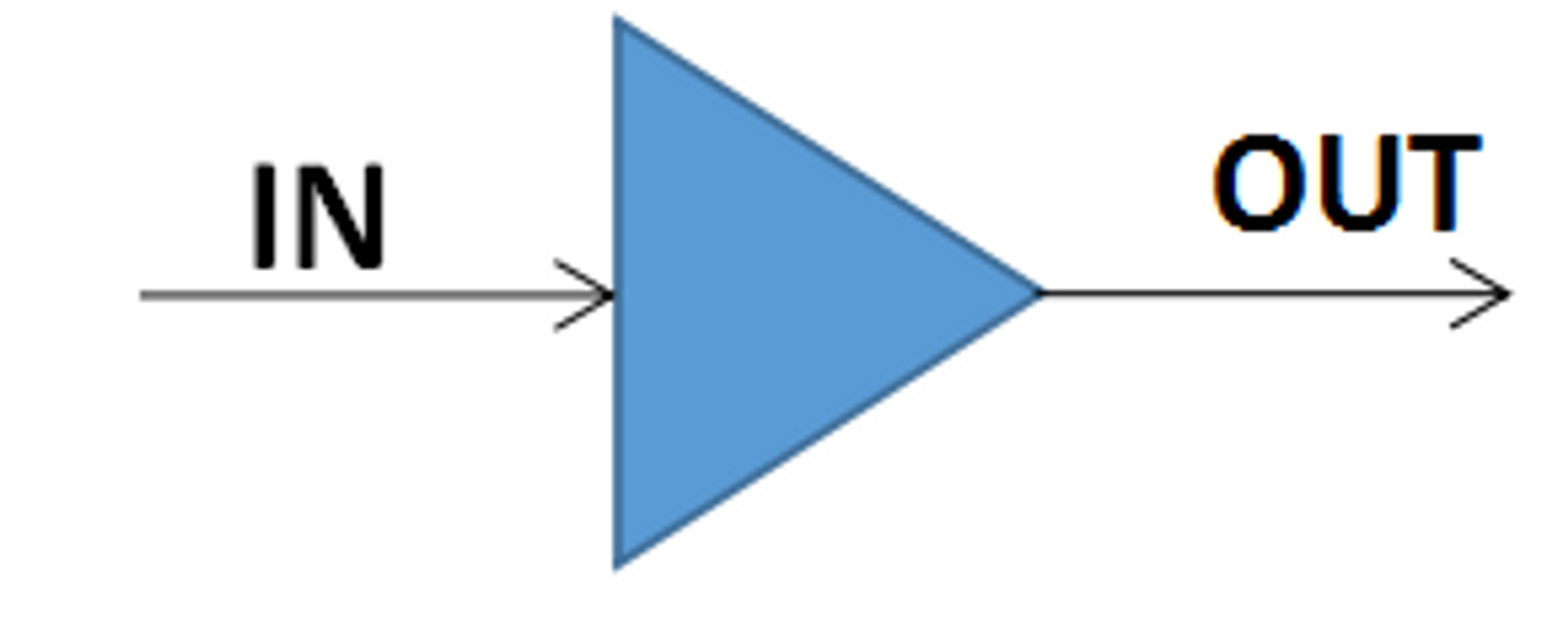

电源隔离单元(power isolation cell):主要用于模块的输入、输出。它可以关掉电源时,将信号保持为常数,从而避免单元的输入悬空。电源隔离单元如下图所示:

保持寄存器(retention register):在不工作的情况下,将寄存器的状态保留下来。

- **动态电压、频率调节(DVFS技术):**自适应时钟速率和供电电压

- 电源门控Power Gating:(静态功耗)指芯片中某个区域的供电电源被关掉,即该区域内的逻辑电路的供电电源断开(在模块不使用时将其关闭),为了最小化漏电流,门控电源晶体常使用高阀值电压单元;

- 基于缓存的系统体系结构: 使用小范围的缓存

- 对数FFT体系结构: 基于对数系统实现FFT

- 高级门控时钟Clock Gating: 使用时序门控时钟

- 异步(无时钟)设计: 移除时钟

- **高阀值电压HVT:**提高阈值电压,可以减小漏电流;

- 存储器电源门控:在不使用存储器时将其关闭(静态功耗)

RTL级降低功耗:

- **并行与流水:**采用并行处理,可以降低系统工作频率,从而可能降低功耗

- **状态机编码和解码:**格雷码最适合低功耗设计,格雷码比用二进制码翻转更少,可以降低开关活动,功耗更低。

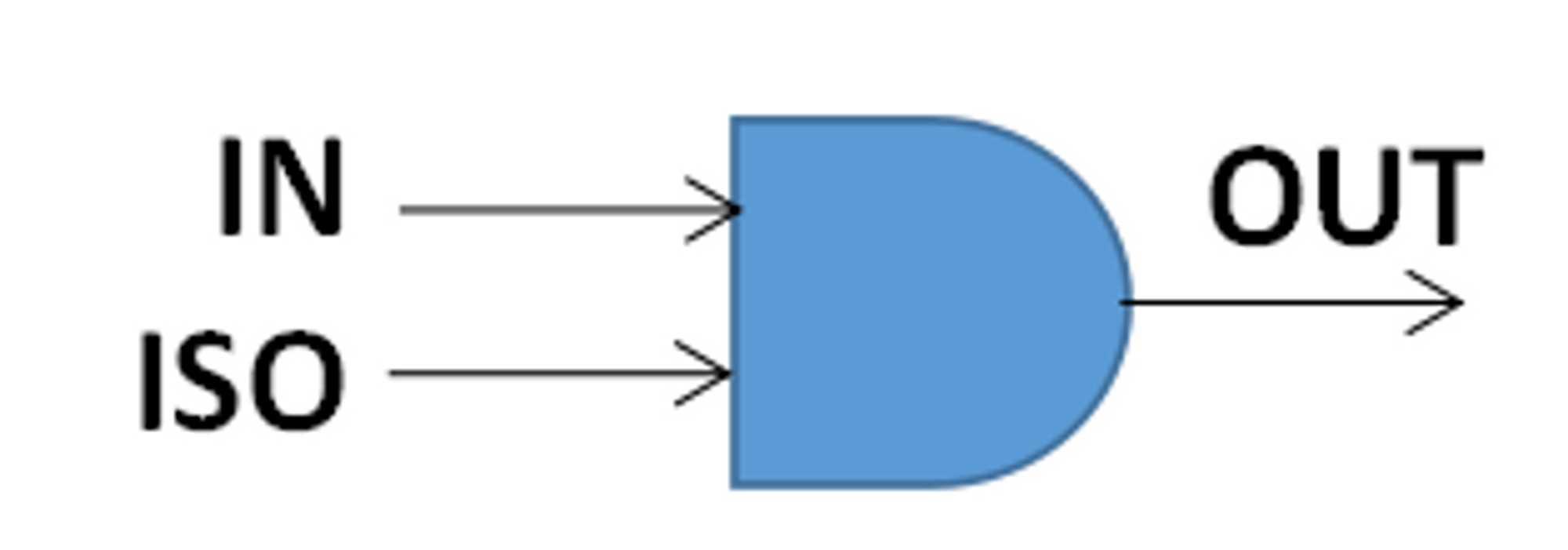

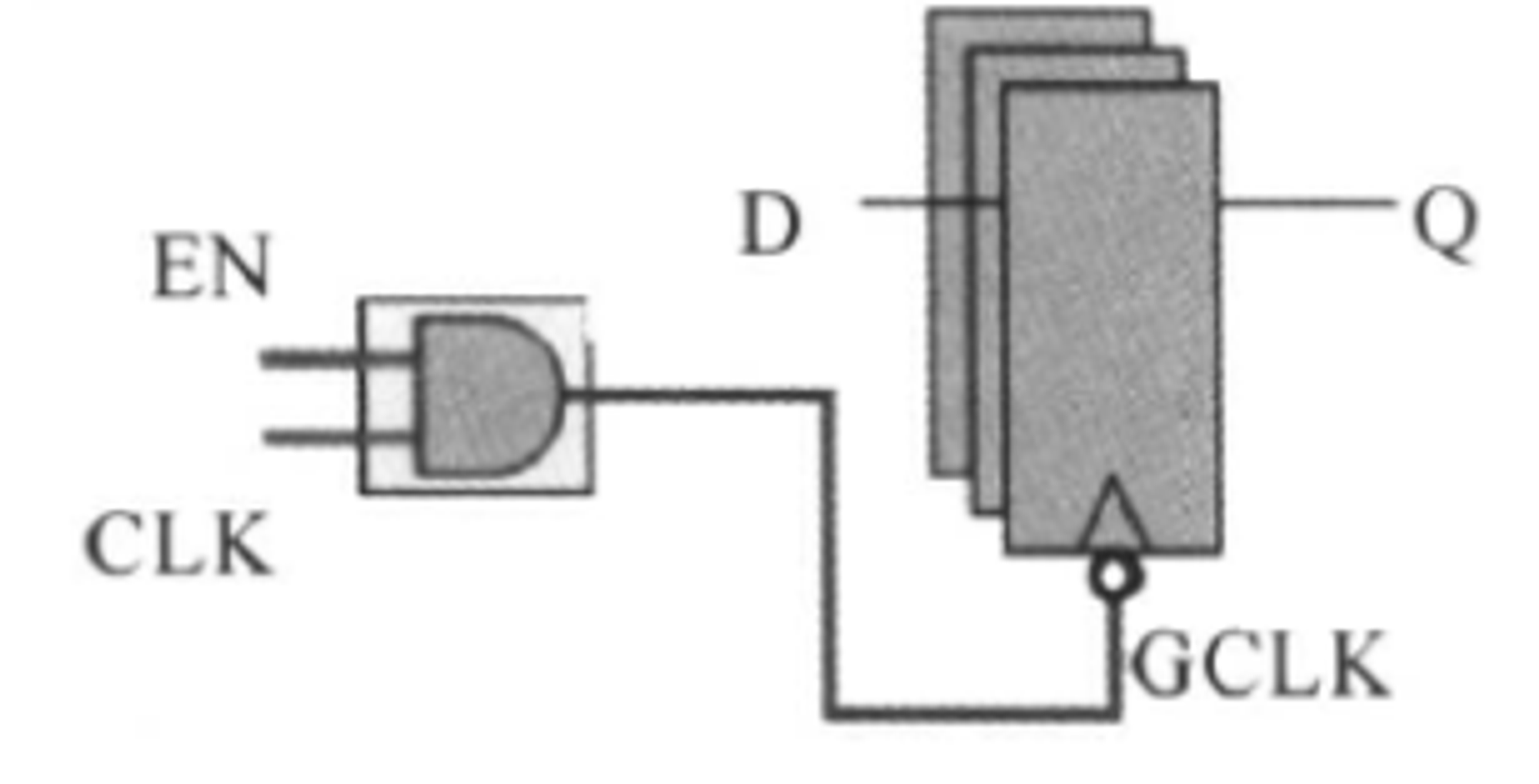

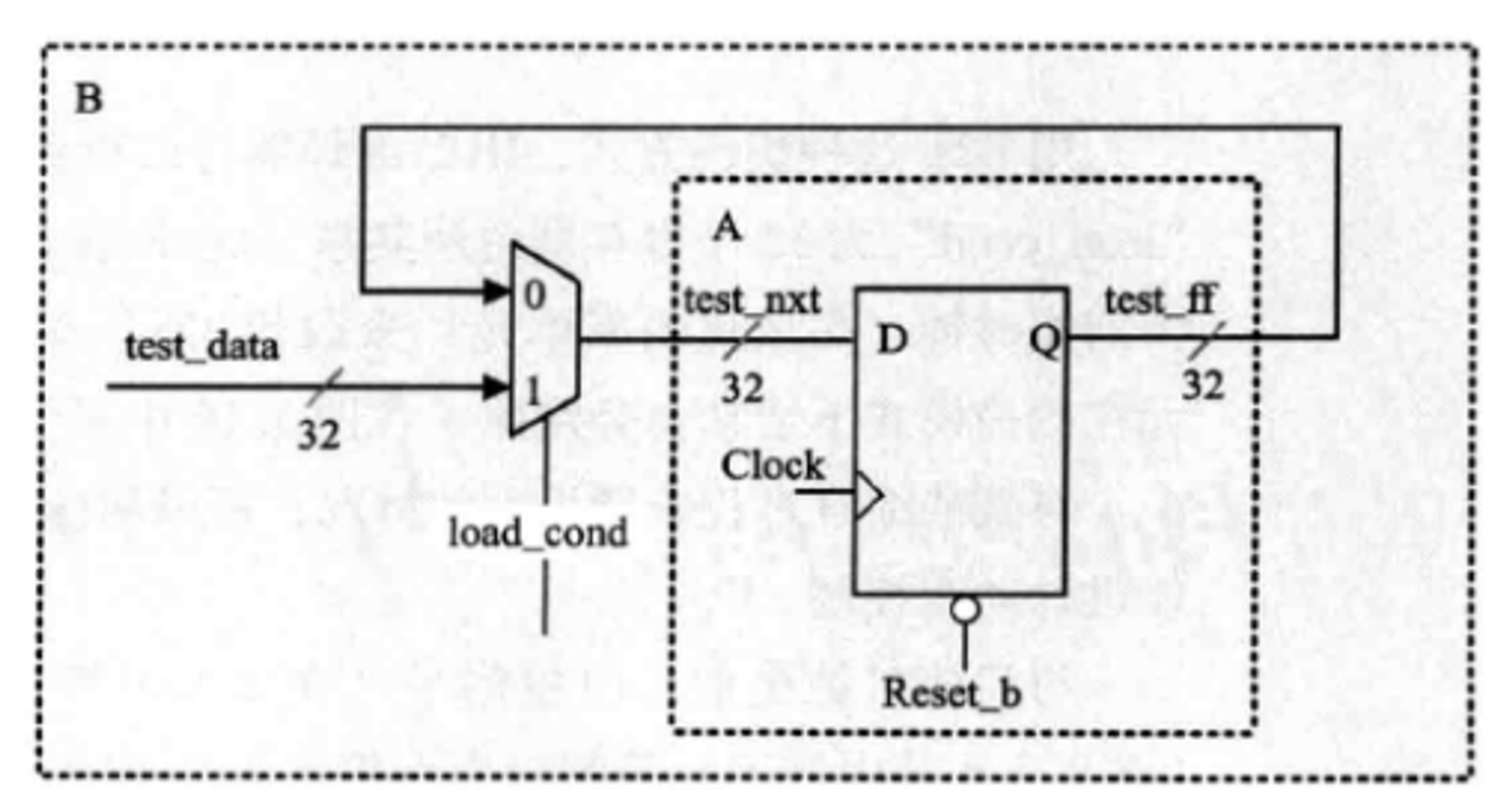

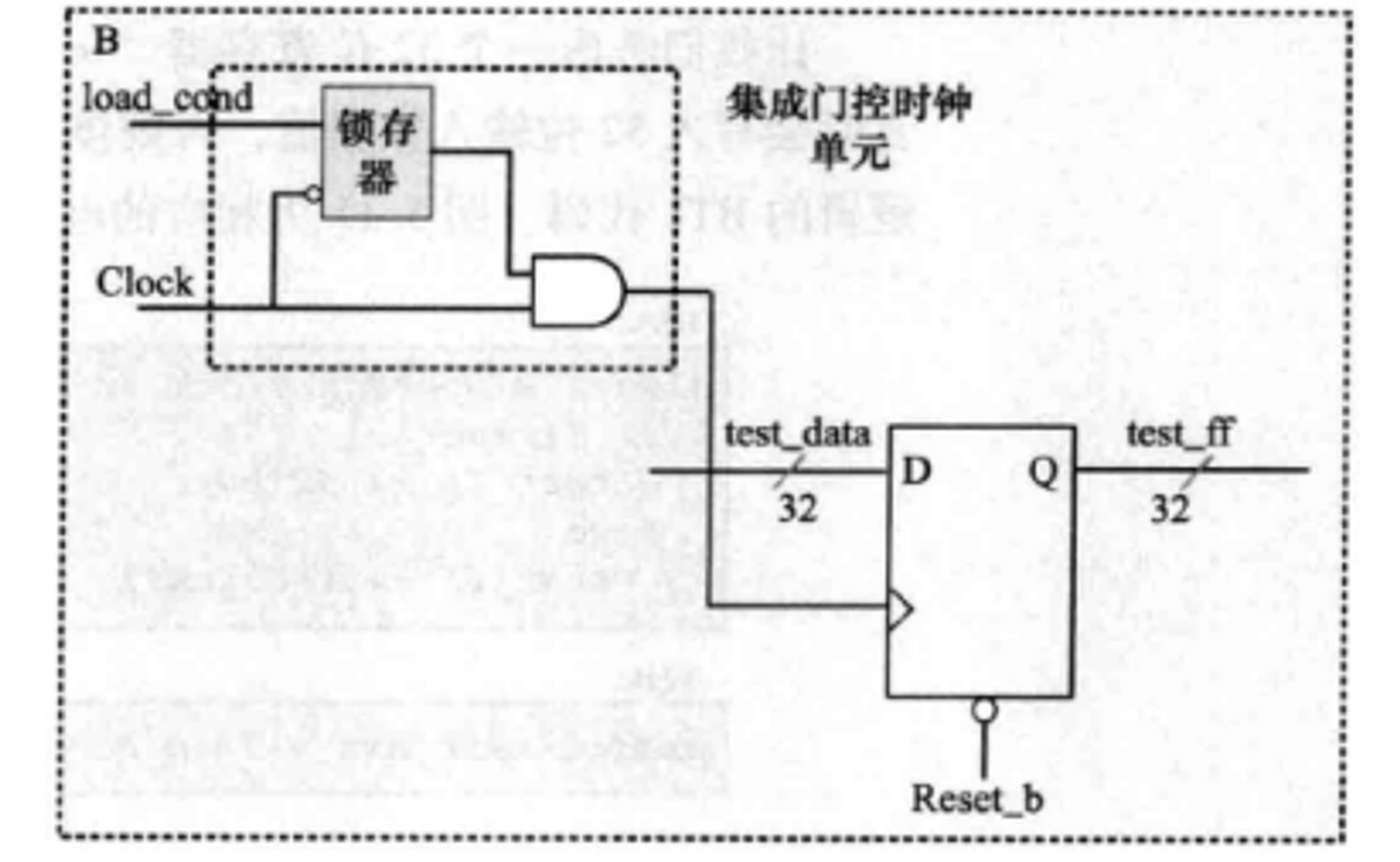

- 门控时钟:

上述电路图中,将控制信号(EN)直接与时钟信号(CLK)进行与操作,以完成门控。门控后的时钟信号GCLK送到寄存器中,当EN为0时,该时钟被关掉。

不使用门控时钟:

always@(posedege clock or negedge reset_b)

if(!reset_b)

test_ff<=32’b0;

else

test_ff<=test_nxt;

assign test_nxt=load_cond?Test_data:test_ff;

使用门控时钟:

always@(posedege clock or negedge reset_b)

if(!reset_b)

test_ff<=32’b0;

else if(load_cond)

test_ff<=test_data;

- 独热码多路器:独热编码方式比二进制编码方式,输出更快更稳定,可以在初期将未选中总线掩藏掉,实现低功耗效果;

- 除掉多余的转换

- **资源共享:**资源共享降低功耗,有同样的操作在多处使用,可以避免相同的运算逻辑在多个位置重复出现。

- 使用行波计数器来降低功耗(可减小漏电流并降低功耗,但使用必须非常小心)

- **总线翻转编码技术:**在当前数据和下一个数据之间的汉明距离大于N/2(N是总线宽度),就将下一个数据反向后输出,以减少总线上的转换次数;对于减少大容量总线上的转换次数很有效;

- 高活跃度网络:将活跃度较高的网络和活跃度较低的网络区分开,然后置于逻辑云中尽可能深的位置;

- 启用和禁用逻辑云

- **操作数隔离:**类似电源隔离单元

物理级低功耗技术

- 技术水平:通过先进的硅处理技术,可额外降低功耗;

- **版图优化:**优化布线,长布线会增加功耗

- 衬底偏压:也称反偏压,能减小漏电功耗

- 减少氧化层厚度

- 多氧化层厚度

- 设计减小电容

- 对于设计中翻转活动很频繁的节点,采用低电容的金属层进行布线;

- 使高翻转率的节点尽可能地短;

- 对于高负载的节点与总线,采用低电容的金属层;

- 对于特别宽的器件,采用特殊的版图技术,以得到更小的漏极结电容。

- 在有些布局布线工具中,可以将功耗作为优化目标来生成时钟树。

【某笔试题】

1.下列功耗措施哪个可以降低峰值功耗

A 静态模块级Clock Gating

B Memory Shut Down

C Power Gating

D 大幅度提高HVT比例

解析:首先峰值功耗是属于动态功耗中的短路功耗,即NMOS和PMOS同时导通所引起的峰值电流,最终带来的功耗。这个功耗和电源电压,时钟翻转率,以及峰值电流有关。

A选项静态门控时钟,所以A选项不正确。

B选项存储关闭。即不被访问的时候,关闭存储器,因而也是降低静态功耗。

C选项电源门控技术,即模块不工作的时候,关闭电源,模块睡眠,工作时候再启动电源,是降低静态功耗。

D选项即采用高阈值电压的晶体管,阈值电压增加的效果在于降低亚阈值漏电电流,并且短 路 功 耗 公 式 为 :Pshort = τAshortVdd = τAβ(Vdd-Vth)3 , 只 跟 Vth 有 关 , 而 D 选 项 中 大 幅 提 高 HVT ( High Voltage

Value)带入短路功耗公式中会使短路功耗变小,从而降低动态功耗中的峰值功耗。所以D选项正确。

2.逻辑电路低功耗设计中,无效的方法是

A 采用慢速设计

B 减少信号翻转

C 采用较慢速的时钟

D 提高阈值电压

解析:A选项说采用慢速设计并不一定会降低功耗,所以A选项不正确。

B选项减少信号翻转可以降低动态功耗。

C选项采用较慢速时钟也相对的降低了信号的翻转,所以也是降低动态功耗。

D选项即采用高阈值电压的晶体管,阈值电压增加的效果在于降低亚阈值漏电电流,因而降低静态功耗。

3.在RTL设计阶段,降低功耗的常用设计方法是

A 门级电路的功耗优化

B 门控时钟

C 降低电路漏电流

D 多阈值电压

解析:这四个选项都是可以降低功耗的常用设计方法,但是有个前提,那就是在RTL设计阶段,也就是我们编写代码时可以控制的阶段,可以在代码中加入门控时钟,所以B选项正确。

4.某个状态下,不关心某个寄存器的输出值,那么将其设计为输出0,可以降低功耗(错误)

解析:比起设计为输出0,降低功耗更好的做法是保持寄存器原值。因为功耗来自于信号toggle,如果在上一状态寄存器输出为1,下一状态下输出为0,即便0不使用,也产生了0到1的跳变,同样会有功耗,既然不关心,还不如保持输出为1。

5.isolation cell是下面哪种低功耗技术必须的 B

A.Clk gating

B.Multi VDD

C.power gating

D.Multi VT

解析:如上介绍

**6.以下哪个不是影响芯片功耗的基本要素:湿度

电压 温度 工艺 湿度