作者的话

之前的文章里有写到如何使用CCES来进行DSP的flash program,那都是单核的DSP,而ADI还有很多双核甚至三核DSP,这些DSP应该如何操作呢,会有哪些不同?我再写一个文档来说一下。

跟单核DSP一样,在 CCES 平台下,使用仿真器对目标板上的 SPI Flash 进行程序加载,要先将工程编译生成.ldr 文件;生成 ldr 文件是调用 CCES 的 elfloader.exe(在 CCES 安装目录下可以找到)完成的,这个步骤通过 CCES 工程属性设置和编译就可以完成;而用 cldp.exe(在 CCES 安装目录下可以找到)下载程序到 SPI flash,需要在 CMD 里面进行。

硬件准备

ADSP-BF609-CORE开发板

AD-HP530ICE仿真器:ADI DSP专用仿真器(非常好用)

软件准备

CCES软件

如何生成双核.ldr 文件

-

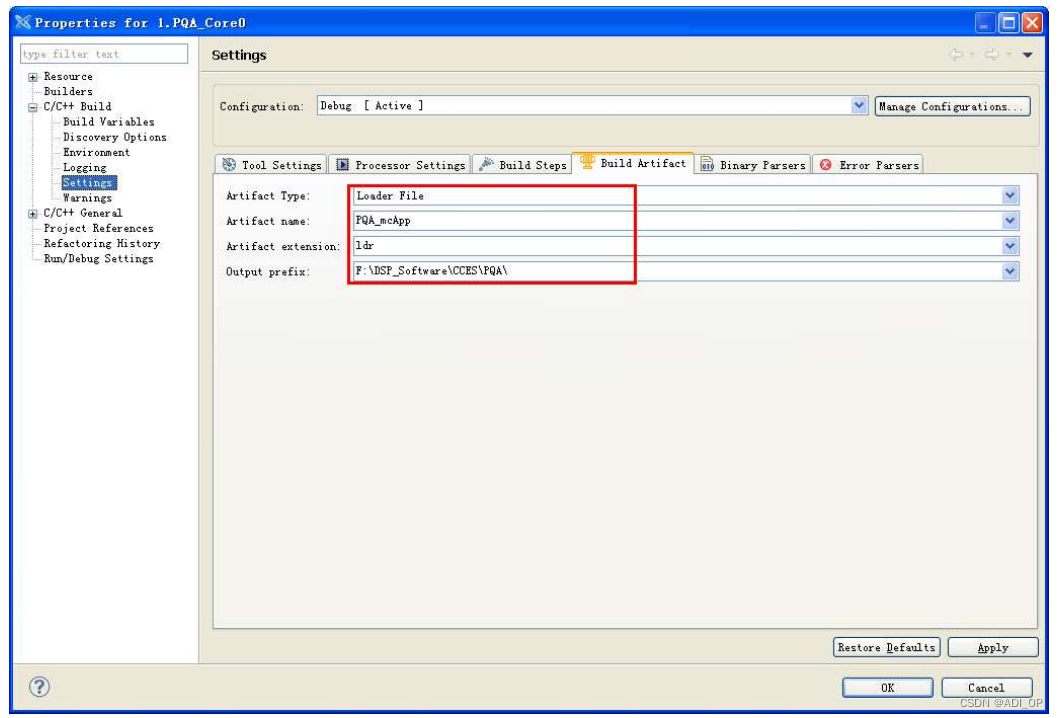

在 Project Properties—settings—Build Artifact 中设置相应选项,如图:

Artifact Type: 工程的输出文件类型;

Artifact name: 输出文件的名称,注意不能有空格;

Output prefix: 输出目录;

-

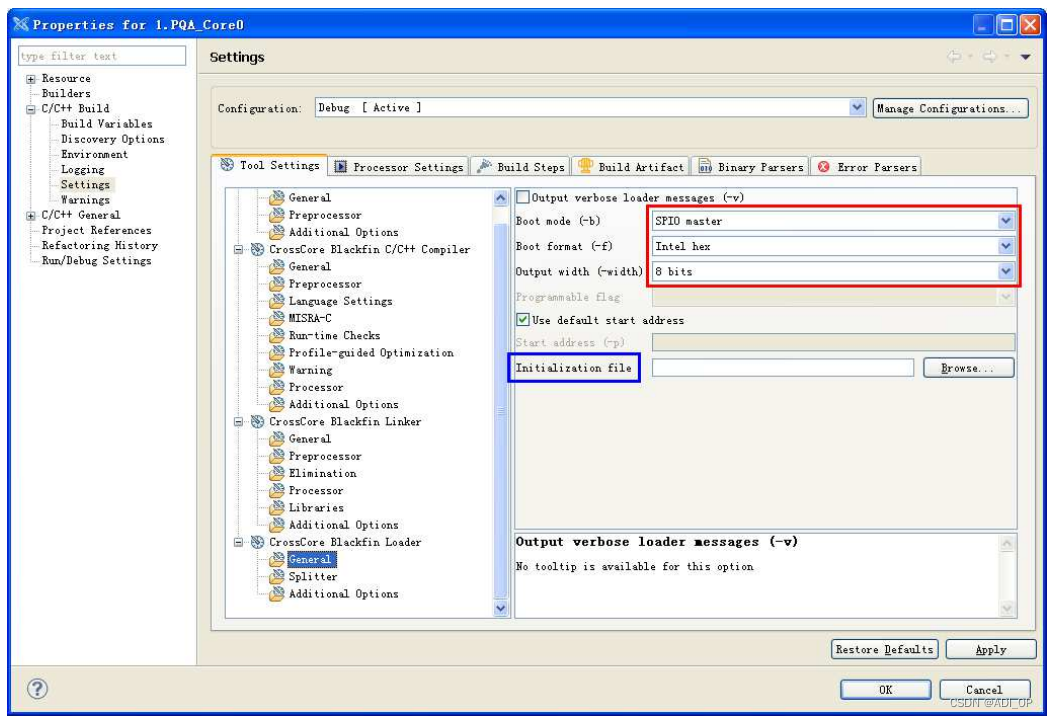

完成步骤 1 后,在 Tool Settings 会出现 CressCore Blackfin Loader 选项,在 General 中设置相应项,如图:

Initialization file: 初始化代码,用来初始化 DDR,主频率等来提高启动速度;

在 ADI 官方文档《EE-240 ADSP-BF533 Blackfin 加载过程》page5 有详细讲解 Initialization file 的作用;

-

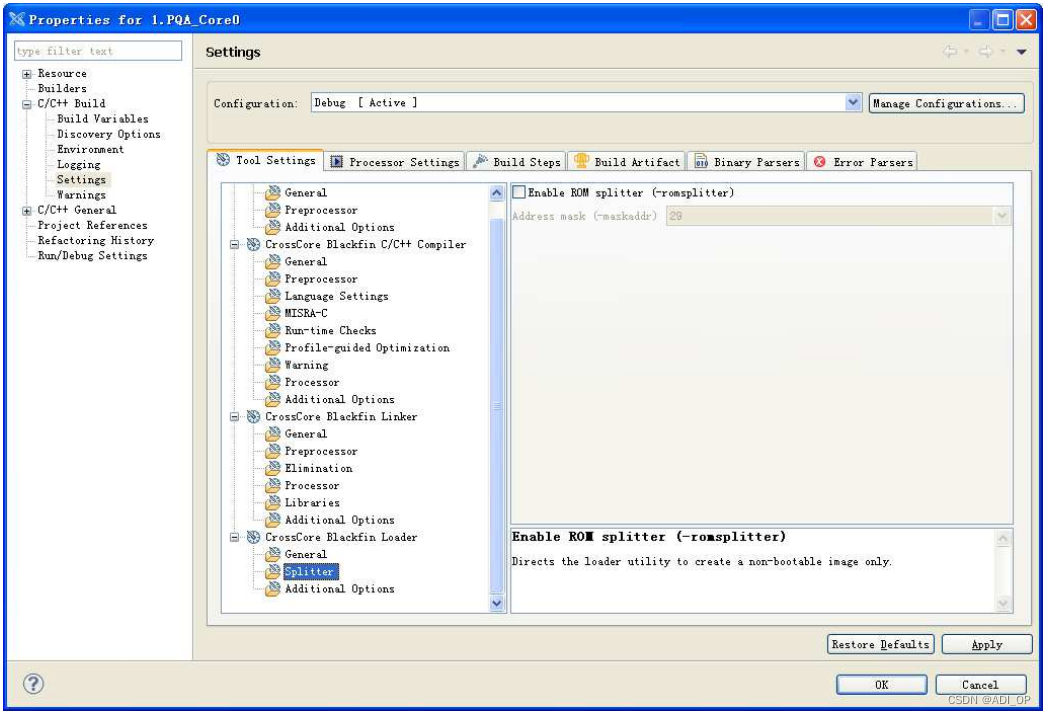

Splitter 为可选项,disable 即可;

-

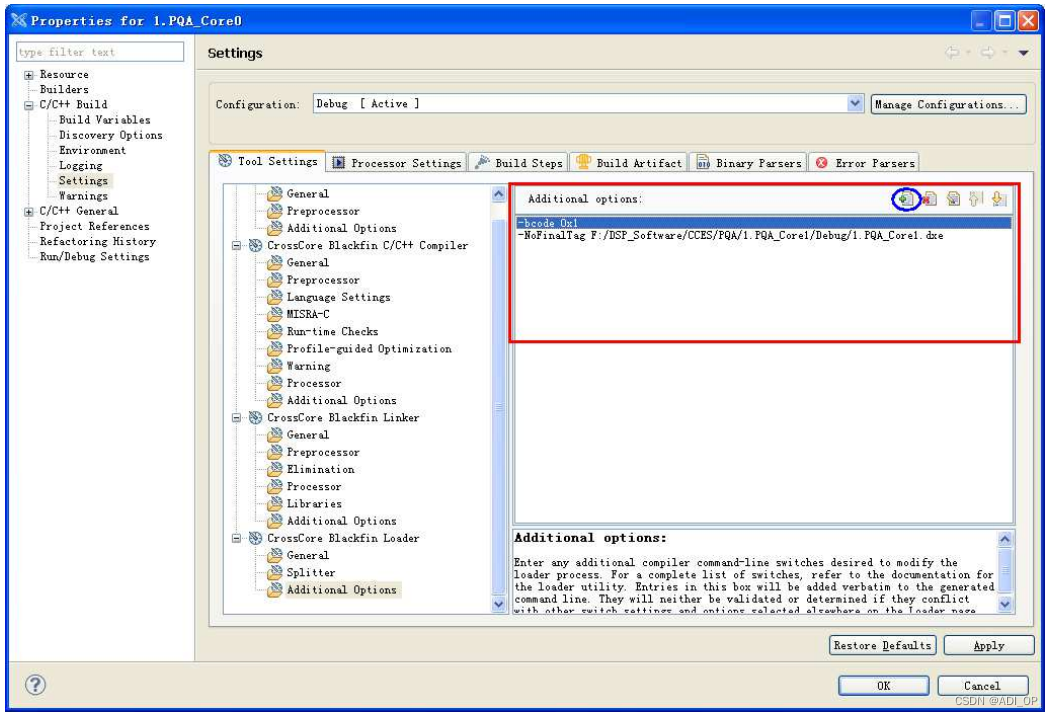

Additional Options 需要添加两项 Options

-bcode 0x1 设置 SPI clk 分频系数,0x1 表示 SPI SCLK = SCLK0/32;

详见手册《BF60x _hwr_man_rev0.41.pdf》page2229;

NoFinalTag 用来将 core1(或 coreB)的代码一起注入到.ldr;

注意路径必须用’/ ’,被关联文件必须是.dxe 文件;

详见 ADI 官方文档《CCESv1.0.1_loader_man._rev.1.1.pdf》page133;

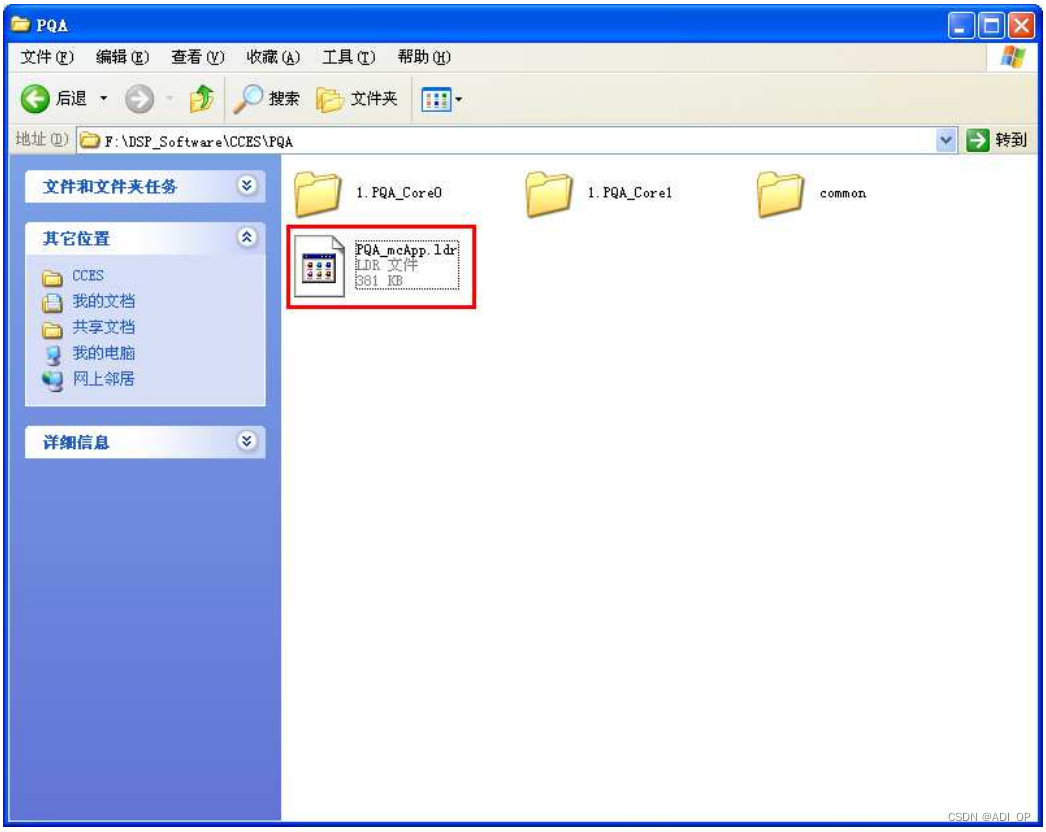

- 完成以上步骤,F7 编译即可生产双核.ldr 文件,如图:

如何加载.ldr 文件到目标板

这个烧写的过程,其实我之前已经在文章中写过了,这里再简单复述一下把。

在 CMD 中进入到 CCES 安装目录,如图:

调用 cldp, 输入命令行:

cldp -proc ADSP-BF609 -emu 1000 -driver “C:\Analog Devices\ADI BF60x EZ-BOARD Software v1.0.0\ADSP-BF609_EZ-Board\Examples\Device_Programmer\serial\w25q32bv_dpia\Debug\w25q32bv_dpia.dxe” -cmd prog -erase affected -offset 0 -format hex -file “F:\DSP_Software\CCES\PQA\PQA_mcApp.ldr” -proc –driver –emu –cmd –erase –format –file

命令的含义可通过 –help 命令获得;相关文档详见 ADI 官方文档《CCESv1.0.1_loader_man._rev.1.1.pdf》page135;

具体命令的意思我就不再复述了,之前的文章里有详细的说明。

- 出现 done,至此加载完成,复位 board,开始运行 SPI Flash 的程序;注意确保 BOOT MODE 已经设置为SPI Flash 启动;

![[附源码]JAVA毕业设计体检系统(系统+LW)](https://img-blog.csdnimg.cn/7c2f1352fa2d46859dfd0c7149f7fb61.png)

![[论文解析] HeadNeRF: A Realtime NeRF-based Parametric Head Model](https://img-blog.csdnimg.cn/d74f02afb29944c192942102f90f7066.png)

![[附源码]计算机毕业设计JAVA中达小区物业管理系统](https://img-blog.csdnimg.cn/7fbe4f764ddb471d8fb9128812b2faa0.png)