目录

概要

整体架构流程

技术名词解释

技术细节

1.低阻输出,以减小误差

2.抗混叠

3.电源级保护

小结

概要

提示:这里可以添加技术概要

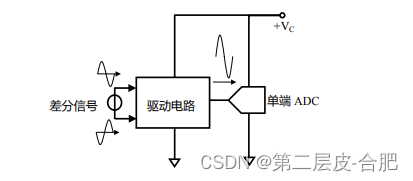

一个模拟电压信号,在进入ADC 的输入端之前,一般都需要增加一级驱动电路(Driver]。但是,也有一些ADC,它具有“设计极为贴心”的输入端,就无需在前级增加驱动电路了。因此︰给ADC输入端增加驱动电路是必须的,除非你确保驱动电路是不必要的。

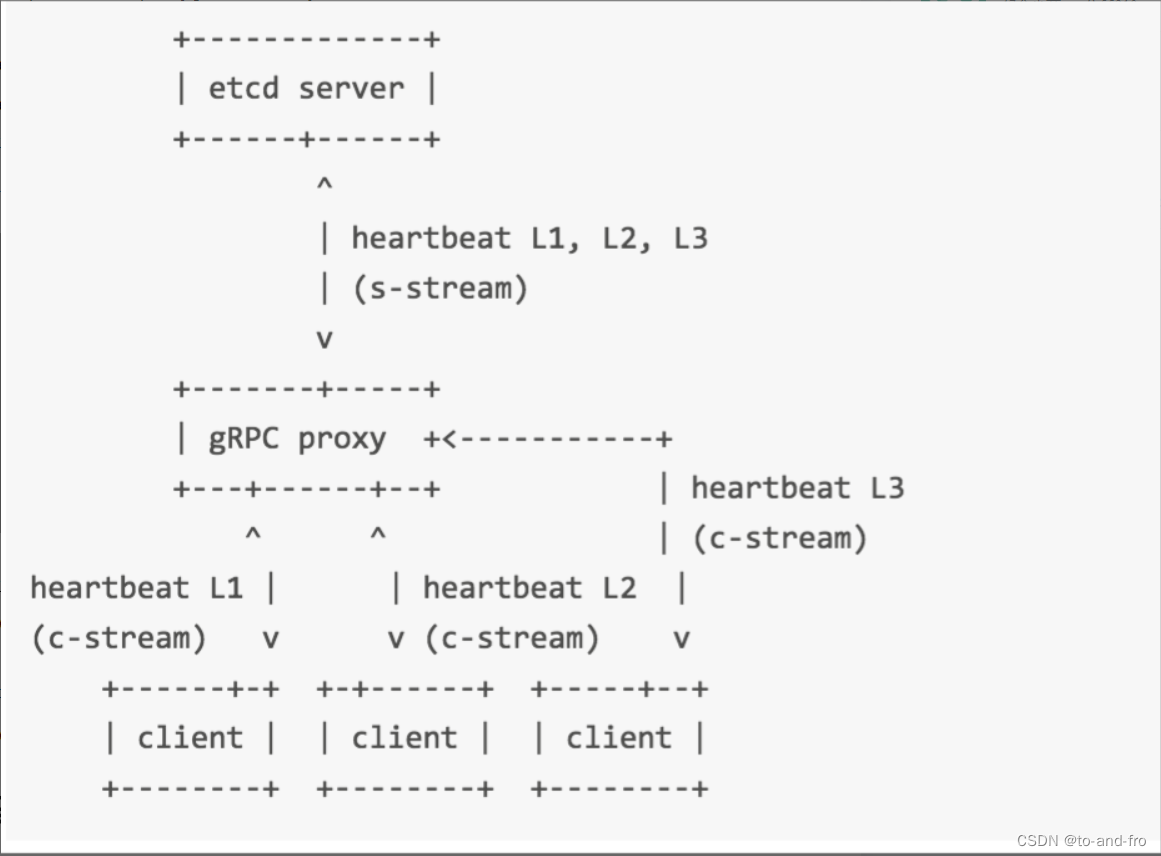

整体架构流程

提示:这里可以添加技术整体架构

本文接着上文。继续分享其他几个原因。

技术名词解释

ADC:模拟数字转换器即A/D转换器,或简称ADC,通常是指一个将模拟信号转变为数字信号的电子元件。通常的模数转换器是将一个输入电压信号转换为一个输出的数字信号。由于数字信号本身不具有实际意义,仅仅表示一个相对大小。故任何一个模数转换器都需要一个参考模拟量作为转换的标准,比较常见的参考标准为最大的可转换信号大小。而输出的数字量则表示输入信号相对于参考信号的大小

技术细节

提示:这里可以添加技术细节

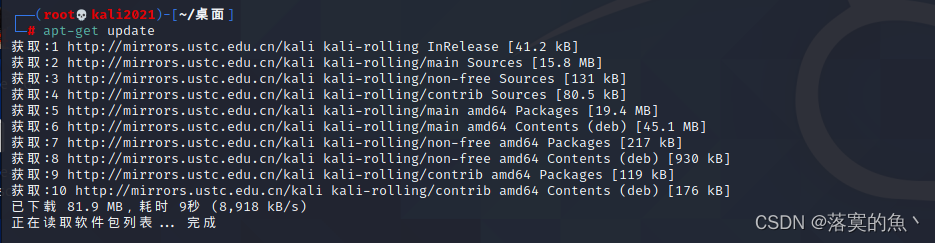

1.低阻输出,以减小误差

有些原始信号,具有一定阻值的输出电阻。将这样的信号直接接入 ADC,会带来测量误差。误差的根源是:

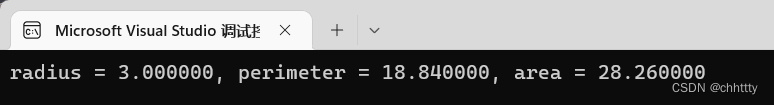

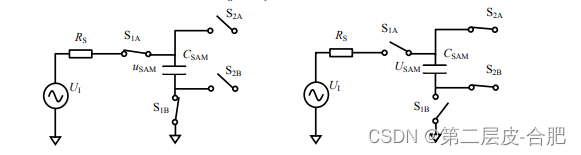

多数 ADC内部都有采样电容,以实现采样保持功能。这种 ADC 的内部结构一般如图和-3所示。它由两组开关,一个采样电容Cs,以及后续没有画出的转换电路组成。ADC 整个工作分为两个阶段[phase],以下以一个直流电压输入u为例。

1)采样阶段∶开关SiA、Sie闭合,开关Saa、Sz断开,输入信号通过电阻Rs给电容

充电,以完成对输入信号的采样。此时电容电压用usat]表示,它将越来越逼近于u。采样阶段持续时间为Ts

2)转换阶段

采样阶段结束,立即进入转换阶段,此时开关断开,开关S2A、S2闭合,电容上保持有Tsam时间内充电的结果,用U表示,有:![]()

而ADC内部的采样电容是确定的,一般都是10pF数量级。这就要求外部串联的源电阻不得大于某个值。源电阻包括ADC内部开关的导通电阻,以及信号源的输出电阻。

当信号源内阻较大时,形成是时间常数可能不满足式要求,直接接入ADC一定会造成采样误差。这就需要增加一级驱动电路,比如电压跟随器,以达到信号输出电阻很小的目的。

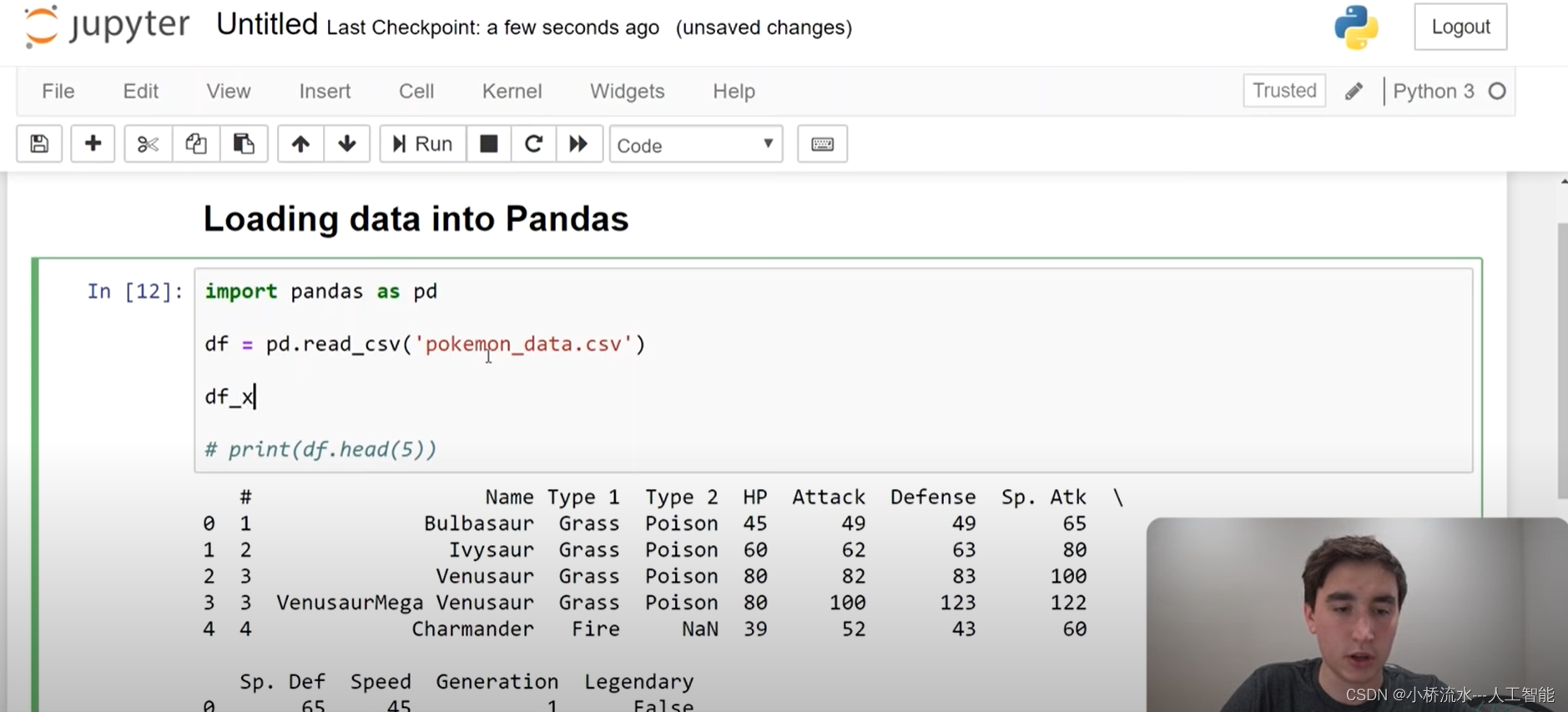

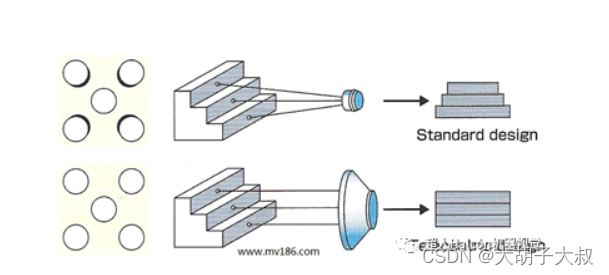

2.抗混叠

当输入被测信号频率为f,那么按照奈奎斯特定律,要想完整采集信号,采样率f必须大于2f。当采样率小于2f时,一定会出现混叠现象,即采集的波形中出现很低的混叠频率。图Section124-4演示了混叠频率的出现原因。图中输入信号为黑色的高频信号,当采样率小于2f时,我们获得的采样点形成了红色的波形,其频率不是信号频率,而是混叠频率,很低。混叠现象欺骗了我们,因此我们不希望出现这种现象。一旦在数据中出现混

叠频率,后期即便增加软件滤波,也是难以剔除的。

唯一的方法就是让大于fs/2的频率信号,不要出现在ADC的入端,或者这种频率分量在ADC入端只有很小的幅度。因此,增加驱动电路,以滤除或者减小高于f./2的频率信号,就成为必须。

常见的方法是,给ADC入端之前,增加一级截止频率为f币的无源低通电路,以实现抗混叠滤波。

其中,fu>>fsignal,是让有用信号fsignat尽量不被伤害。而fn<是为了将大于的信号尽量滤除干净。对于无法实现砖墙式滤波(非1即О式的,小于截止频率,系数为1;大于截止频率,系数为О)的一阶RC低通滤波器来说,这是一个矛盾,顾此就会失彼。在此情况下,截止频率到底取多少,取决于你到底重视哪一项︰你侧重于保护被测有用信号不被伤害,就尽量增大截止频率,而你倾向于剔除混叠信号,就尽量减小截止频率。

这样看起来,f像个夹板丈夫,左边是媳妇,右边是母亲......,有时候,严谨枯燥的科学设计,也需要一些艺术。

言归正传,信号在进入ADC 之前,做必要的低通滤波,以避免混叠现象,是必要的。低通滤波的截止频率选择,,自己做斟酌吧。

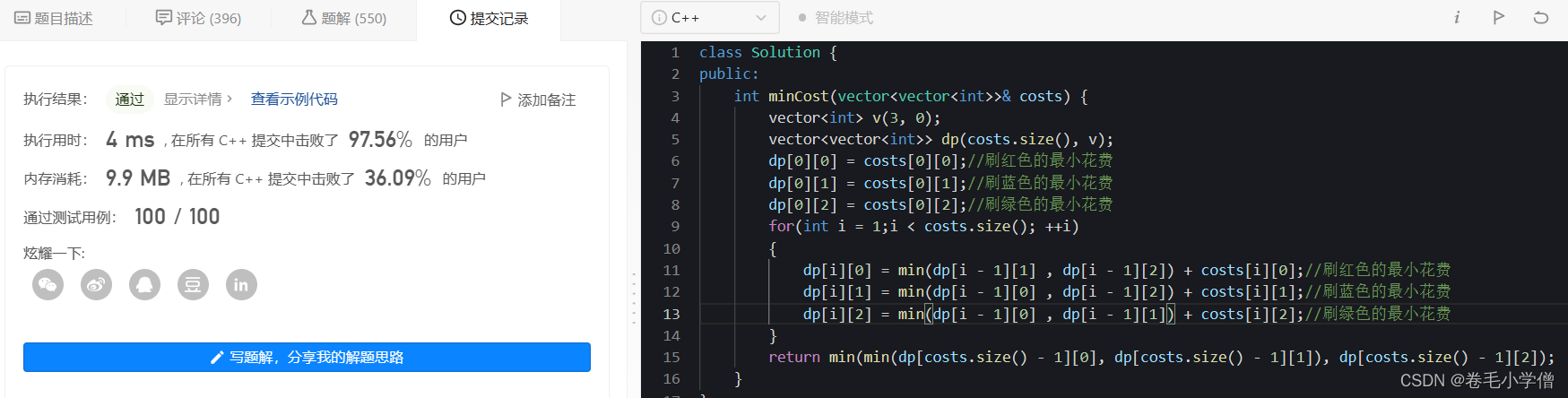

3.电源级保护

一般来说,ADC的价格(几美元到几十美元甚至更高)会高于前端放大器价格。用廉

价的东西保护昂贵的东西,是-一个常用的方法。而ADC的前级驱动电路,就可以实现这种

保护。

将ADC前端的驱动电路,用一个安全的供电电压,就可以实现对ADC的电源级保护。

所谓的电源级保护,是指驱动电路的输出,不可能超过电源电压。这样,只要选择电源电

压在ADC输入端认可的安全范围内,就可以保证ADC的输入端不会超限。

多数ADC输入端承受最高电压,就是其电源电压。因此,将ADC的供电电压与前端

驱动电路的供电电压,选择成一致的,就可以实现对ADC入端的电源级保护。

小结

提示:这里可以添加总结

通过两篇文章学习了ADC的驱动电路。