目录

一、新建工程

二、时序报告分析

1、打开时序报告界面

2、时序报告界面介绍

3、时序路径分析

三、总结

FPGA开发过程中,vivado和quartus等开发软件都会提供时序报告,以方便开发者判断自己的工程时序是否满足时序要求。

本文将详细介绍如何读懂Vivado时序报告,包括报告的基本结构和如何分析报告。

一、新建工程

使用vivado创建一个新的工程,添加verilog代码文件,内容如下:

module xdc_test

(

input wire clk,

input wire reset,

output reg [3:0] data_cnt

);

always @(posedge clk or posedge reset)begin

if(reset)

data_cnt <= 'b0;

else

data_cnt <= data_cnt + 1'b1;

end

endmodule创建xdc文件,并添加时序约束:

create_clock -period 6.6667 -name clk -waveform {0.000 5.000} [get_ports clk]如果需要了解时序约束如何添加,可以看下上一篇文章。

点击“generate bitestream”,开始综合、布线和生成bit文件。

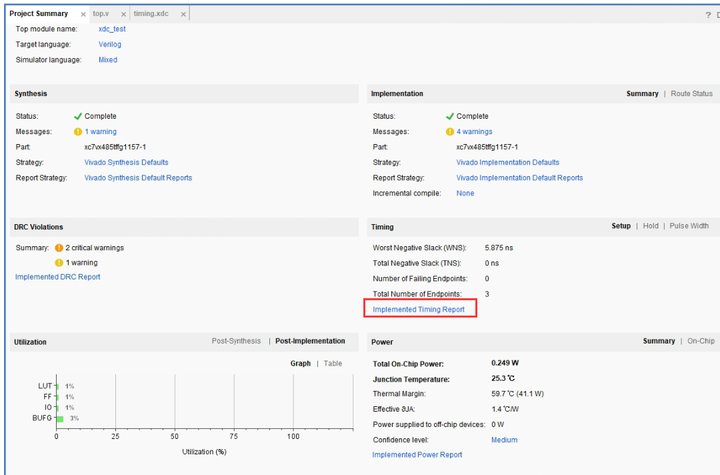

综合完成后,可以在“Design run”界面,看到整个工程时序满足情况,主要资源消耗、编译时间等等信息,如下图。

二、时序报告分析

1、打开时序报告界面

(1)方法1

点击“实现implementation”下的“report timing summary”选项。

出时序显示设置界面,如下图所示,点击OK。

(2)方法2

点击功能栏“∑”,在“Timing”界面下,点击“Implementation Timing Report”。

2、时序报告界面介绍

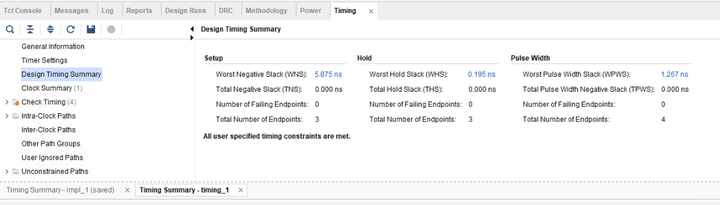

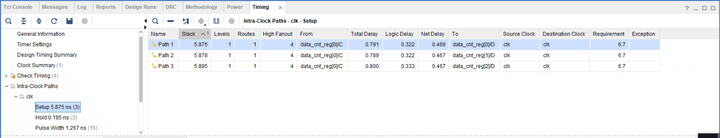

Timing界面左侧是时序信息总览、时钟和时序路径分类,右侧是时序信息总览详细信息,包括Setup、Hold以及Pulse Width检查最差的各10条路径。

这里有几个重要的参数信息名称:

WNS (Worst Negative Slack) :最差负时序裕量

TNS(Total Negative Slack) :总的负时序裕量 ,也就是负时序裕量路径之和。

WHS (Worst Hold Slack) :最差保持时序裕量

THS (Total Hold Slack) :总的保持时序裕量,也就是负保持时序裕量路径之和。

这些参数如果为负或者颜色变为红色,则表示出现了时序违例,否则表示时序正常。

3、时序路径分析

点击时序报告界面中WNS的数值,如上面报告中的“5.875ns”,则会直接跳转到时序最差路径的界面。

主要参数信息含义如下:

slack:时间裕量

level:逻辑级数,表示两个寄存器之间存在的组合逻辑层数

fanout:扇出数,表示一个信号驱动的所有接收端的数量

from:路径起始位置,包含HDL代码中的起始寄存器

to:路径结束位置,包含HDL代码中的起始寄存器的下一级寄存器

Total Delay:整个路径的总体延时

Logic Delay:整个路径的逻辑延时

Source Clock:路径起始寄存器的时钟

Destination Clock:路径终点寄存器的时钟

Requirement:时钟周期,即路径延时最大值

如果slack出现红色值,且为负值,则表示出现了时序违例。

另外通过看level和fanout,可以看到路径时序违例的原因,level值过大,则表示逻辑层数太多,需要考虑将这条路径对应HDL代码分成几拍完成;如果fanout值过大,则表示该寄存器的扇出过大。

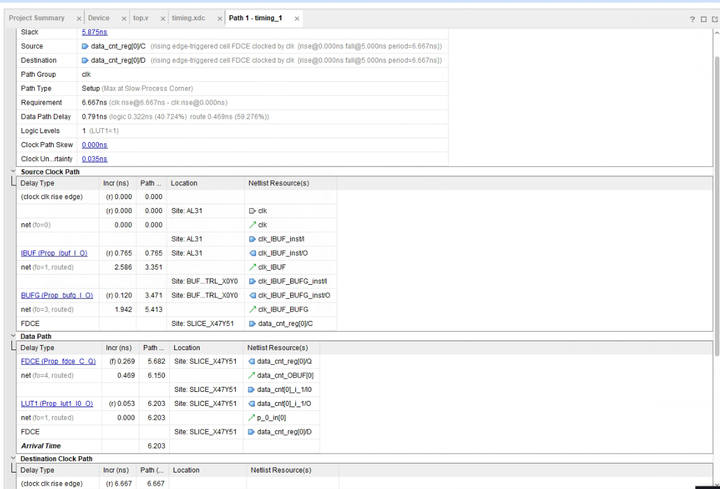

双击任意一条时序路径,以“path1”为例,即可进入该路径的时序具体信息,主要包括summary(总览)、Source Clock Path(源时钟路径)、Data Path(数据路径)、Destination Clock Path(目的时钟路径)。

这里可以查看到具体的时序布线情况,以及时序违例的原因。

三、总结

时序报告是Vivado中必不可少的工具,它可以帮助我们了解电路的时序性能,并找出潜在的时序问题。通过分析时序报告,我们可以确定关键路径延迟、slack和每个信号路径的延迟等信息,并找到需要优化和调整的地方。如果存在时序问题,我们可以通过修改代码、时序约束或重新布局/重分配电路来进行优化。

本文将不断定期更新中,码字不易,点⭐️赞,收⭐️藏一下,不走丢哦

本文由FPGA入门到精通原创,有任何问题,都可以在评论区和我交流哦

您的支持是我持续创作的最大动力!如果本文对您有帮助,请给一个鼓励,谢谢。