第一章 验证导论

1、基本测试平台的功能

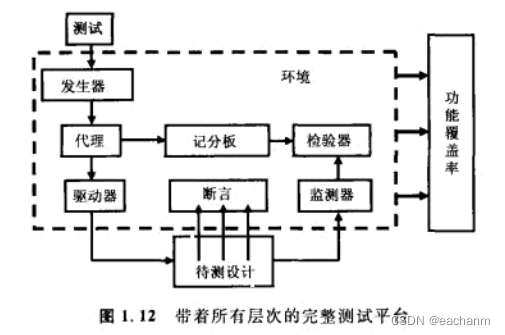

测试平台的用途在于确定待测设计的正确性。包含下列步骤:

(1)产生激励。

(2)把激励施加到DUT上.

(3)捕捉响应。

(4)检验正确性。

(5)对照整个验证目标测算进展情况。

2、方法学基础

本书使用如下原则:

(1)受约束的随机激励。

(2)功能覆盖率。

(3)使用事务处理器的分层测试平台。

(4)对所有测试通用的测试平台,

(5)独立于测试平台之外的个性化测试代码。

3、随机化对象

1、考虑设计输入

(1)设备配置。

(2)环境配置。

(3)输入数据。

(4)协议异常。

(5)错误和违例。

(6)时延

4、测试平台

5、建立一个分层的测试平台

1、创建一个简单的驱动器

首先,来仔细看看其中的一个模块一驱动器。图1.13所示的驱动器接收来自代理的命令。驱动器可能会注人错误或者增加时延,然后再把命令分解成一些信号的变化,例如总线请求或握手。这样一个测试平台模块通常被称为“事务处理器(transactor)”,它的核心部分是一个循环:有关事务处理器的示范代码如例1.4所示。

task tun ();

done = 0;

while (! done) begin

//获取事务

//变换

//发送事务

end

endtask2、仿真环境

三个基本阶段: 建立 、 运行、 收尾。

1、建立

(1)生成配置:把待测设计的配置和周围的环境随机化。

(2)建立环境:基于配置来分配和连接测试平台构件。测试平台构件指的是存在于测试平台中的部分,注意与设计中的物理构件区分开,后者是采用RTL代码描述的。例如,如果配置选择了三个总线驱动器,那么测试平台应该在这个阶段对它们进行分配和初始化。

(3)对待测设计进行复位。

(4)配置待测设计:基于第一步中生成的配置,载入待测设计的命令寄存器。

2、运行阶段是指测试实际运行的阶段,可分为以下步骤。

(1)启动环境:运行测试平台构件,例如各种BFM和激励发生器。

(2)运行测试:启动测试然后等待测试完成。

3、收尾

(1) 清空:在最下层完成以后,你需要等待待测设计清空最后的事务。

(2)报告:一且待测设计空闲下来,你就可以清空遗留在测试平台中的数据了。

第二章 数据类型

System Verilog引进了一些新的数据类型,它们具有如下优点。

(1)双状态数据类型:更好的性能,更低的内存消耗。

(2)队列、动态和关联数组:减少内存消耗,自带搜索和分类功能。

(3)类和结构:支持抽象数据结构。

(4)联合和合并结构:允许对同一数据有多种视图(view)。

(5)字符串:支持内建的字符序列。

(6)枚举类型:方便代码编写,增加可读性。

一、内建数据类型

1、逻辑(logic)类型

S V对经典的reg数据类型进行了改进,使得它除了作为一个变量以外,还可以被连续赋值、门单元和模块所驱动。为了与寄存器类型相区别,这种改进的数据类型被称为logic。任何使用线网的地方均可以使用logic,但要求logic不能有多个结构性的驱动,例如在对双向总线建模的时候。此时,需要用线网