目录

写在前面

1. 概念介绍

2. 高速度结构设计

2.1 高流量

2.2 低延时

2.3 优时序

2.3.1 组合逻辑插寄存器

2.3.2 并行结构

2.3.3 展平逻辑结构

2.3.4 寄存器平衡

2.3.5 重新安排路径

3. 总结

写在前面

本博客为阅读书籍《高级FPGA设计》的部分读书笔记,主要侧重于前几章的内容。

1. 概念介绍

在进行 Verilog 设计中,一般会考虑三个基本参数:速度、面积、功耗。

- 速度:即设计的系统尽可能支持更大的时钟频率。

- 面积:即设计的系统面积越小,也就是使用的资源越少。

- 功耗:即设计的系统运行功耗尽可能的低。

在设计中,这三个参量不可能完全顾及到,这时候就需要根据实际的设计需求进行合理的变换,达到一个合理的平衡。比如常见的有:面积换速度,速度换面积等。

2. 高速度结构设计

在高速度的设计中,同样有是三个指标:流量(throughout)、延时(latency)、时序(timing)。

- 流量:即在单位时间内可处理的数据量,这个数据量用位宽表示。

- 延时:即数据输入与数据输出之间的时间,数据处理的时间。

- 时序:即建立时间余量和保持时间余量的,越大表示时序越好。

2.1 高流量

举个例子,在一个设计中,完成一次计算操作需要花费3个时钟周期,当前计算完成后再进行下一次的计算的操作,这样持续进行。这样的设计存在问题就是数据处理过慢,当完全处理一个时间再去处理下一个事件,这样就大大拉长了处理时间。使用流水线设计可以加快处理速度,就像工厂中的流水线一样,完成一件物品的组装需要3个步骤,如果让一个员工完成,需要三个周期,而流水线的操作就可以使用三个员工,每个人完成一个步骤,当第一个员工完成第一个步骤后,给到第二个员工完成第二个步骤,紧接着第三个员工完成最后一步,这样物件就可以持续输入进行组装,速度是之间的三倍。在Verilog流水线设计也是一样,通过使用更多的资源加快数据的处理。

这就是最常见的面积换速度的设计。

2.2 低延时

低延时设计是通过最小化中间处理的延时来尽可能快速地把数据从输入端传递到输出端的设计。通常,低延时设计将要求并行性、去除流水线、缩短逻辑,可能减少设计中的流量或降低最大时钟速度。

这样的设计一方面会减小数据输入到输出的时间,另一方面,也会增加寄存器之间的组合逻辑,进一步会影响时序,在一般的设计中不建议采用这种设计。

2.3 优时序

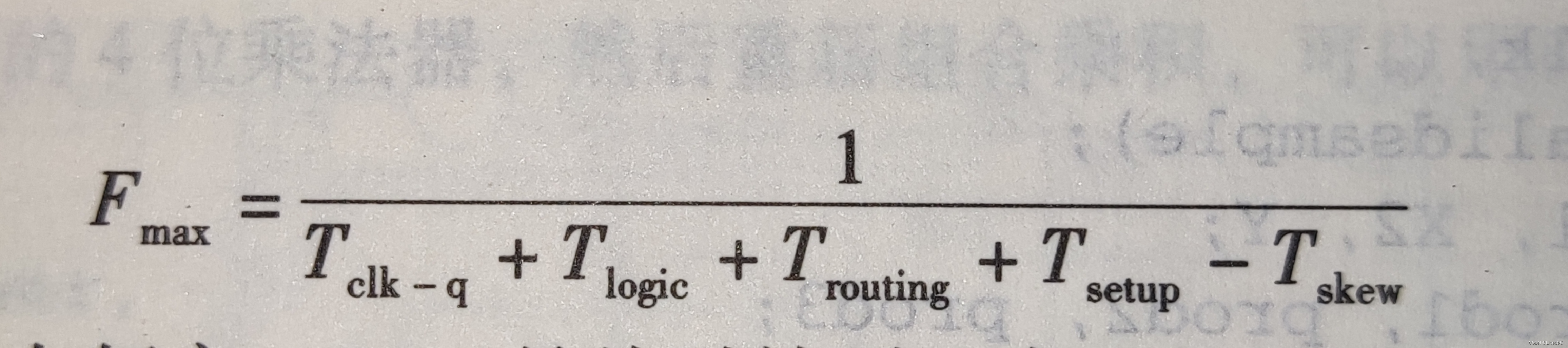

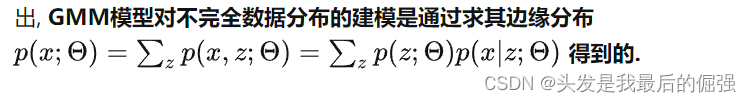

时序指的是设计的时钟速度。在设计中任何两个时序元件之间的最大延时将决定最大的时钟速度。最高速度或最大频率可以通过最大频率公式计算( 不管时钟到时钟的抖动):

其中Fmax是时钟可允许的最大频率,Tclk-q是从时钟到达直至数据到达Q端的时间,Tlogic是逻辑通过触发器之间的传播延时,Trouting是触发器之间的布线延时,Tsetup建立时间,Tskew是启动触发器和捕捉触发器之间时钟的传播延时。

下面介绍几种优化时序的方法。

2.3.1 组合逻辑插寄存器

当某两个寄存器之间的逻辑过长,比如大位宽的加、乘法,这时由于组合逻辑过长导致时序变得很差,通过在组合逻辑之间插入寄存器可以减小关键路径的组合逻辑延时,达到优化时序的效果。

2.3.2 并行结构

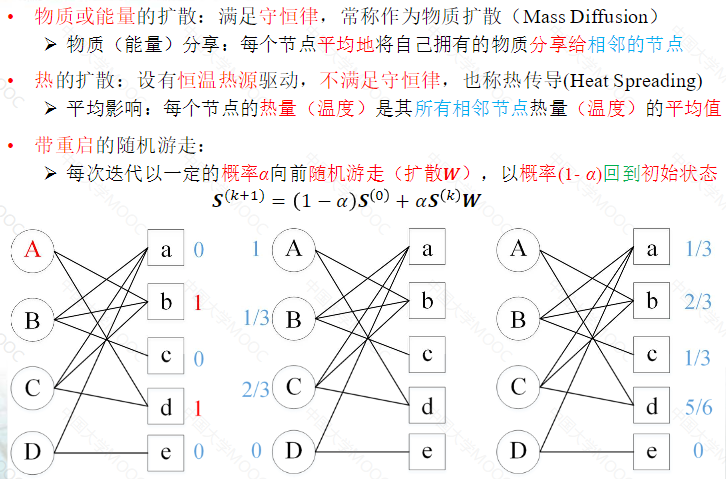

第二个结构的时序改进策略是重新组织关键路径,以致并行地实现逻辑结构。当串联的逻辑计算可以分为并行的逻辑计算时,就应该利用这个技术。

比如以下情况,当大位宽数据进行乘法运算时,如果仅仅使用一个周期去完成计算,可能会导致串联逻辑过长,这时可以将乘数分解成两个数的拼接,然后再进行相乘,相当于将一次串行长运算分解成三次并行短运算,可以进一步优化时序。

![]()

2.3.3 展平逻辑结构

在设计中,多重的if-else if-else if...有先后优先级,会导致在较后条件的逻辑延时过长影响时序,可以去除优先级设计,使用if-if-if或者case语句。

2.3.4 寄存器平衡

第4个方法称为寄存器平衡。概念上讲,这个方法是平等地重新分布寄存器之间的逻辑,减少任何两个寄存器之间最坏条件的延时。这个技术应该随时利用在关键路径和相邻路径之间逻辑高度不平衡时。因为时钟速度只由最坏条件路径来决定,可以做小的改变而成功地重新平衡关键逻辑。

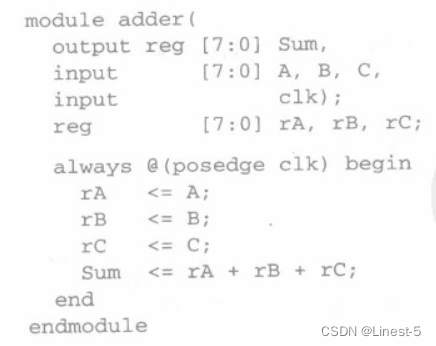

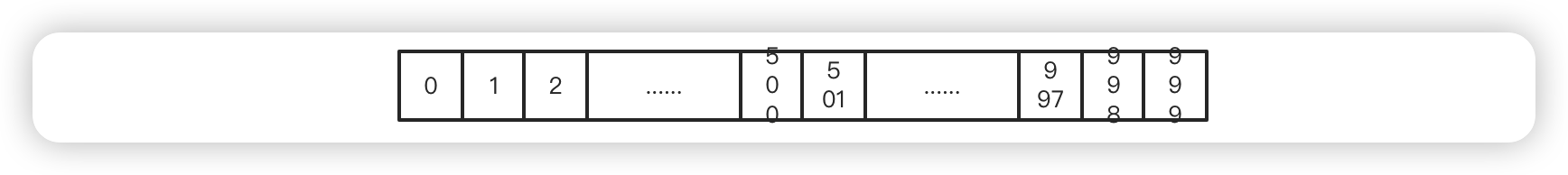

如下情况,对三个位宽为8的数据进行相加操作。

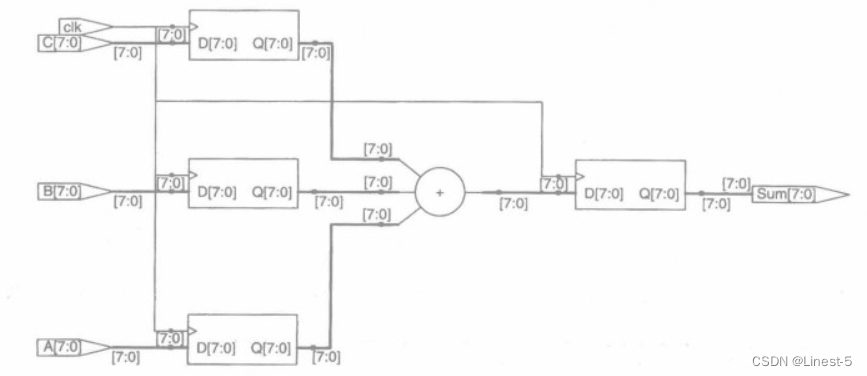

使用这种设计方法得到的综合图,在两个寄存器中间存在三个数的激发逻辑链,这样会影响此条路径的延时,进而影响时序。

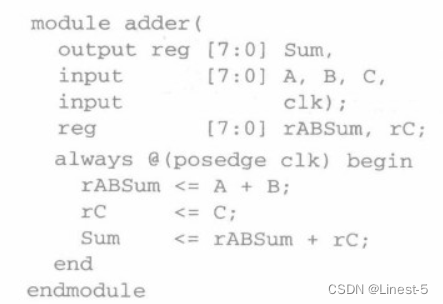

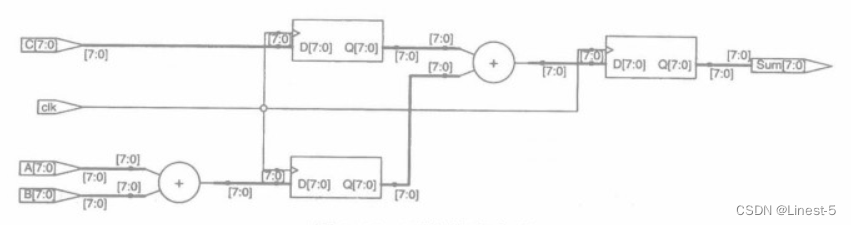

使用寄存器平衡的设计方法,对三个数进行依次两两相加。

使用这种设计方法得到的综合图,可以看到任意两个寄存器之间最多只有两个数的相加,相对于第一种方法减小了逻辑延时。

2.3.5 重新安排路径

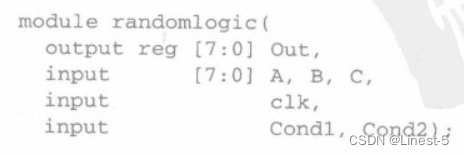

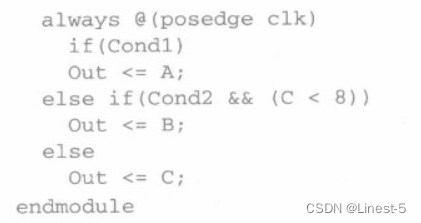

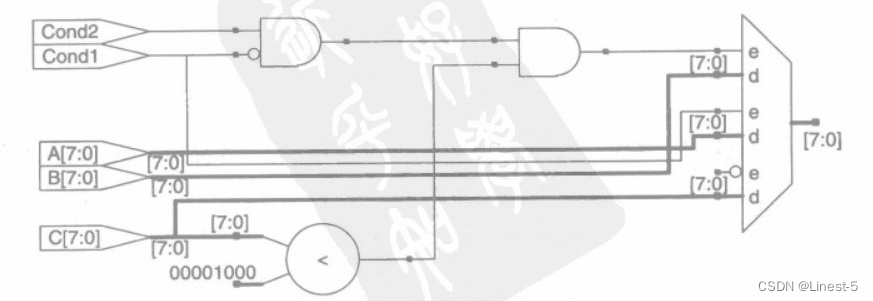

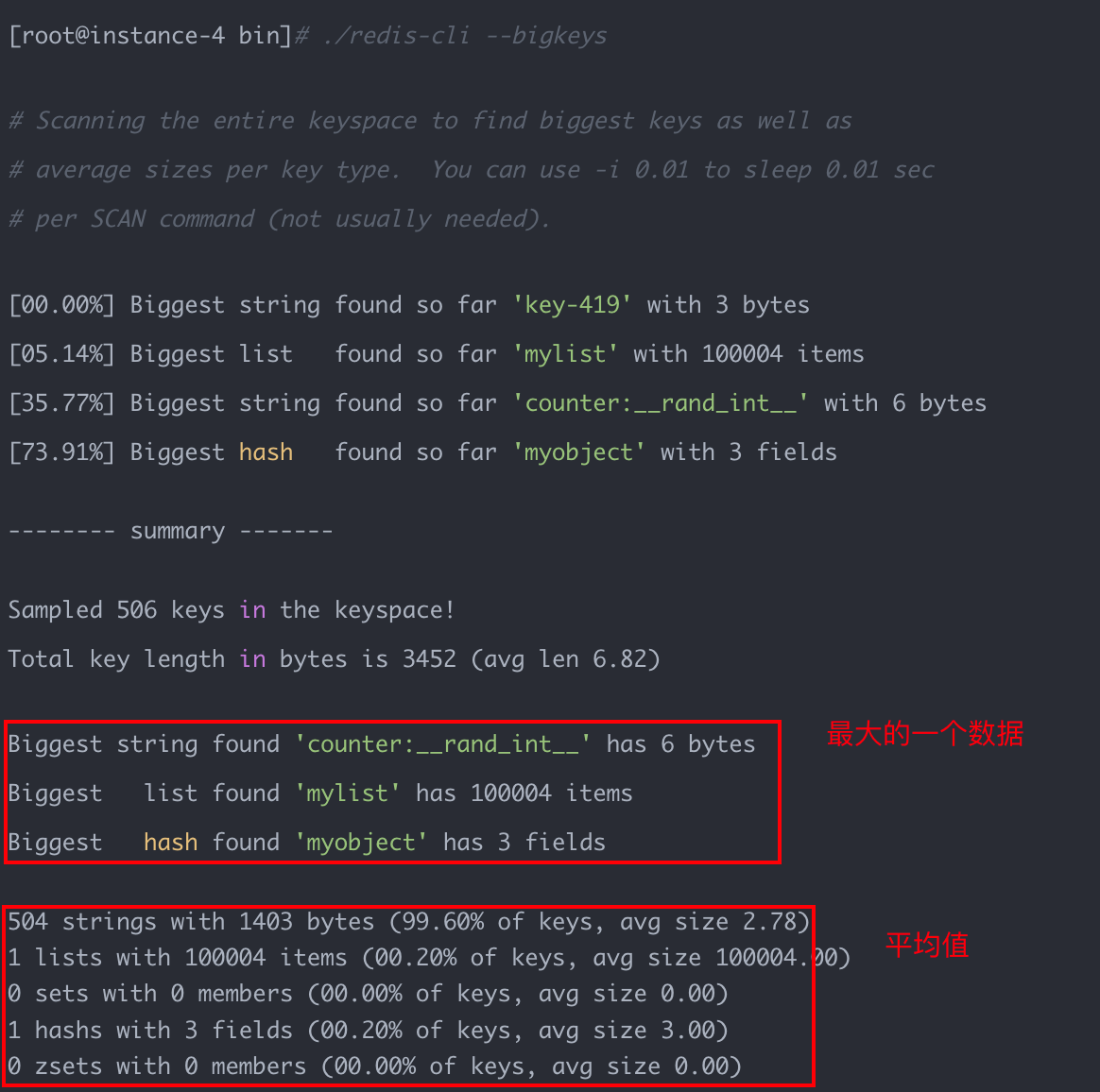

第5个方法是在数据流中重新安排路径使关键路径最小化。当多个路径与关键路径组合时应该利用这个技术,组合路径可以重新安排以致关键路径可以移动到更接近目的寄存器。利用这个策略,将只涉及任何给定的一组寄存器之间的逻辑路径。考虑以下的模块:

得到的综合图,可以看到关键路径在C和out之间,有一个比较器和两个门串联组成,放在mux之前。

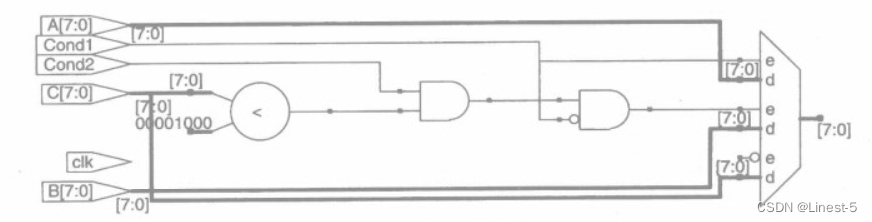

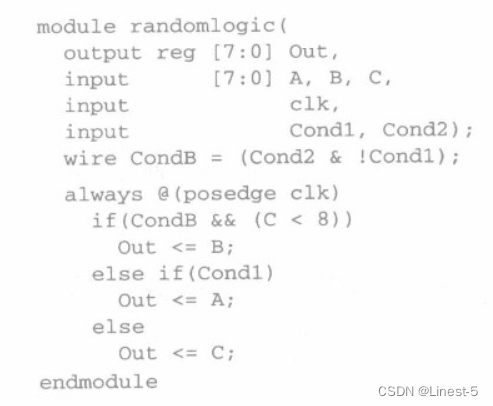

重新安排路径

得到的综合图

重新组织代码,已经从与比较器串联的关键路径移去一个门,如下图所示。因此要特别注意,实际的函数是如何编码的,这对时序性能有直接的影响。

3. 总结

- 高流量结构是每秒可以被设计处理的位数最大化的结构。

- 拆开一个迭代环路会增加流量

- 为拆开一个迭代环路的代价是成比例地增加面积。

- 低时滞结构是从模块输入端到输出端延时最小化的结构。

- 可以通过移去流水线寄存器来减少时滞。

- 移去流水线寄存器的损失是增加寄存器之间的组合延时。

- 时序定义为设计的时钟速度。当设计中任何2个时序元件之间的最大延时比最小时钟周期更小时,设计满足时序要求。

- 把关键路径分成两个更小延时的路径,添加寄存器层次改进时序。

- 把一个逻辑功能分成大量可以并行估值的更小的功能,减少路径延时为子结构的最长延时。

- 去除不需要的特权编码,展平逻辑结构,减少路径延时。

- 从关键路径移动组合逻辑到相邻路径,寄存器平衡改善时序。

- 可以重新安排与关键路径组合的路径来改善时序,方法是关键路径的--些逻辑放置到接近目的寄存器。

![[附源码]Python计算机毕业设计Django酒店物联网平台系统](https://img-blog.csdnimg.cn/4ae069ba4c634d789d13f94019738230.png)