一. 简介

针对已经完成的Vivado在Linux下的安装与运行,本文主要通过一个LED灯闪烁的案例对Vivado和HLS在Linux操作系统下的运行流程进行介绍,并对已安装软件功能进行一个简单的测试。

HLS将C代码的编译综合为Verilog或VHDL代码,本文对HLS生成的代码进行简单的分析,同时也对编译过程中可能出现的报错 “Failed to generate IP”进行解决。

二. Vivado_HLS生成IP核

- 运行Vivado_HLS:

Vivado_HLS的运行过程在Vivado在Linux下的安装与运行中已做介绍,运行以下命令shell脚本即可打开HLS:

source /opt/Xilinx/Vivado/2017.4/settings64.sh ##Vivado在Linux下的安装路径

vivado_hls

打开界面如下图所示:

- 创建新工程 Create New Project,将工程建立在Documents下的workplace工作文件夹内以便查找:

- 顶层模块命名 Top Function:

- 选择FPGA型号 Part Selection,与选用的型号保持一致即可:

- 新建.cpp文件,代码内容很简单,即每隔50M个时钟周期LED灯闪烁一次,编译生成IP核:

IP核如图所示:

三. Vivado工程调用IP核

- 运行Vivado:

Vivado的运行过程在Vivado在Linux下的安装与运行中已做介绍,运行以下命令shell脚本即可打开Vivado:

source /opt/Xilinx/Vivado/2017.4/settings64.sh ##Vivado在Linux下的安装路径

vivado

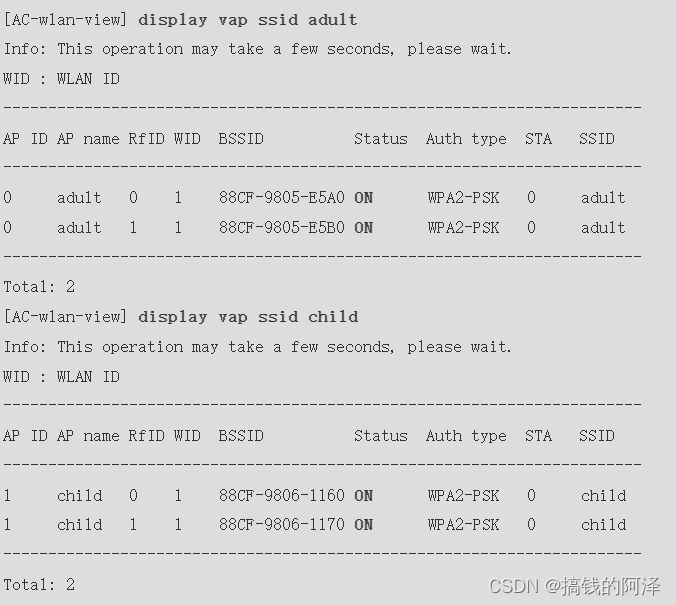

- 新建工程后,在IP Catalog中增加HLS工程所在路径,可以看到HLS生成的IP核成功导入:

- 新建bd(Block Design)工程,导入IP核,ap_rst始终拉低,ap_clk和led_V接口外接:

- ap_clk和led_V分别约束到晶振时钟输出和LED接口:

- 综合成功后生成bit流文件:

- 由于采用时钟为50MHz,因此program device后可以看到LED每秒闪烁一次:

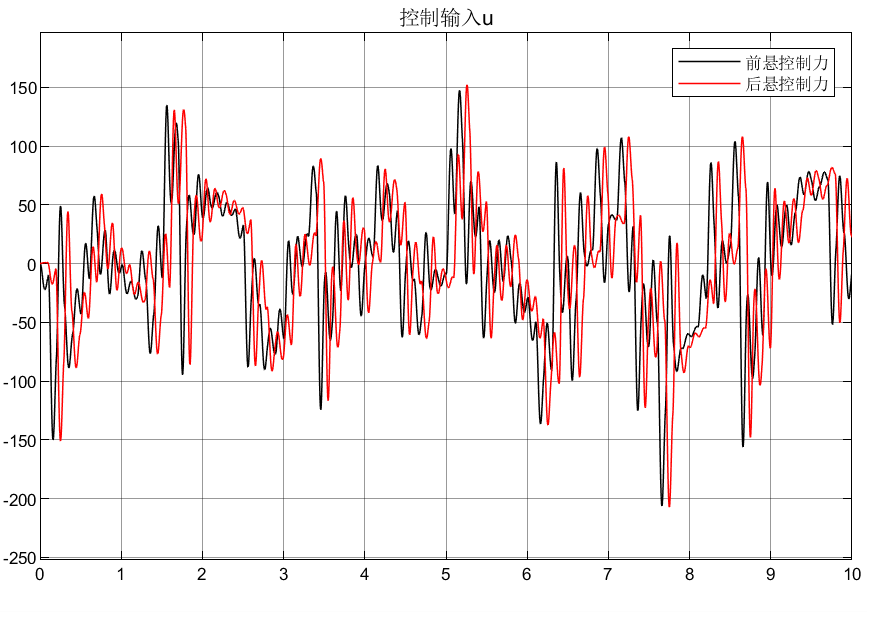

四. HLS生成Verilog代码分析

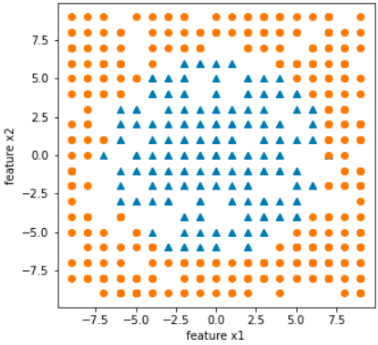

将HLS生成的IP核打开可以看到编译后的Verilog代码如下图:

其中命名较为复杂混乱,但由LED灯的工作原理,可以从输入输出接口入手简单分析:

计数器i_reg_39与i_1_fu_56_p2基本等价,相互赋值完成依赖于输入时钟的计数器功能,通过与25M比较完成led_V输出接口的翻转,实现每50M个时钟周期完成一次闪烁的功能;

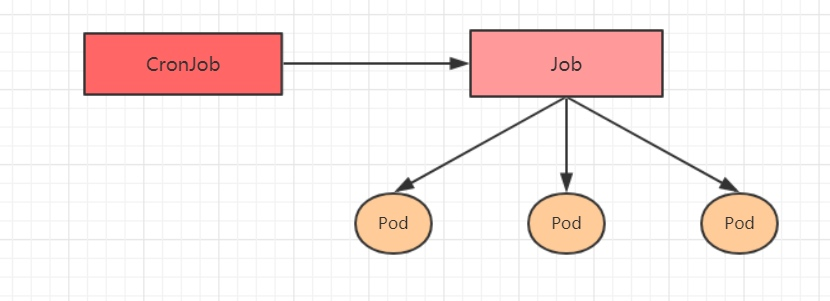

五. HLS运行过程出现的问题与解决

出现问题:

HLS在编译综合工程生成IP核的过程中可能会出现“Failed to generate IP”的报错,如下图所示:

解决方法:

这一问题通常是由于HLS版本较早导致,例如本工程使用的是2017.4版本的HLS,因此需要将系统时间改到2018年之前即可成功生成IP核:

![[附源码]计算机毕业设计JAVA医院门诊信息管理系统](https://img-blog.csdnimg.cn/65e4336648804aed8122d7f01173bc46.png)

![[LeetCode解题报告] 1610. 可见点的最大数目](https://assets.leetcode-cn.com/aliyun-lc-upload/uploads/2020/10/04/5010bfd3-86e6-465f-ac64-e9df941d2e49.png)