(1条消息) 芯片设计全流程知识点总结_GGbao_的博客-CSDN博客

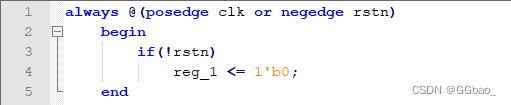

异步复位同步释放在always语句块里为:

当异步复位信号到来时,寄存器 reg_1 会被直接拉低,这是不会产生问题的,当rstn下降沿和clk上升沿同时到来时,如果rstn比clk先到来一瞬间,且原来的reg_1信号为1,reg_1会被拉低为0,后一瞬间,clk来了,因为前一瞬间的reg_1值被拉低了,所以在clk到来时,一定有set_up不满足要求...

但是,一进always 语句块后,由于rstn是0,所以reg_1会被赋值为0,还是0。也就是说不管我reg_1的set_up / hold满不满足要求,reg_1都会被重置到0,不会有任何问题,如图所示:

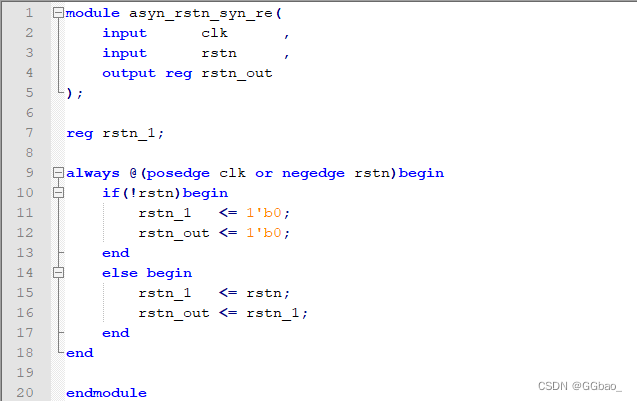

综上所述,异步复位信号是不会产生问题的,但是为什么要同步释放?是释放信号会出问题吗?

答:是的,当rstn释放的时候(从0变1)时,如果rstn释放边沿和clk释放边沿很接近,那么就会出现亚稳态,而亚稳态在电路里面是非常致命的,在亚稳态采样到的数据是不准确的,而电路中一个不准确的值,会导致这后面的所有值都不准确。

当rstn释放的时候,寄存器的输入端D可能因为某个组合逻辑电路和rstn有关系,导致D随rstn同步拉高。那在clk上升沿到来的时候,就会有D的set_up不满足,出现亚稳态,边沿采样的时候,输出reg_1不知道该采D=0的信号还是D=1的信号,所以不妨打两拍,不着急在rstn释放的时候采样,用两个寄存器来延迟两个周期,等到数据D稳定了之后再同步拉高rstn采样。

原文链接:https://blog.csdn.net/qq_57502075/article/details/127073686

![CodeForces.1786A2.发牌.[中等][flg标识][数学规律][双色牌]](https://img-blog.csdnimg.cn/8137059c129646c0887c16f8199edc50.png)