数据寄存器是一个中转站

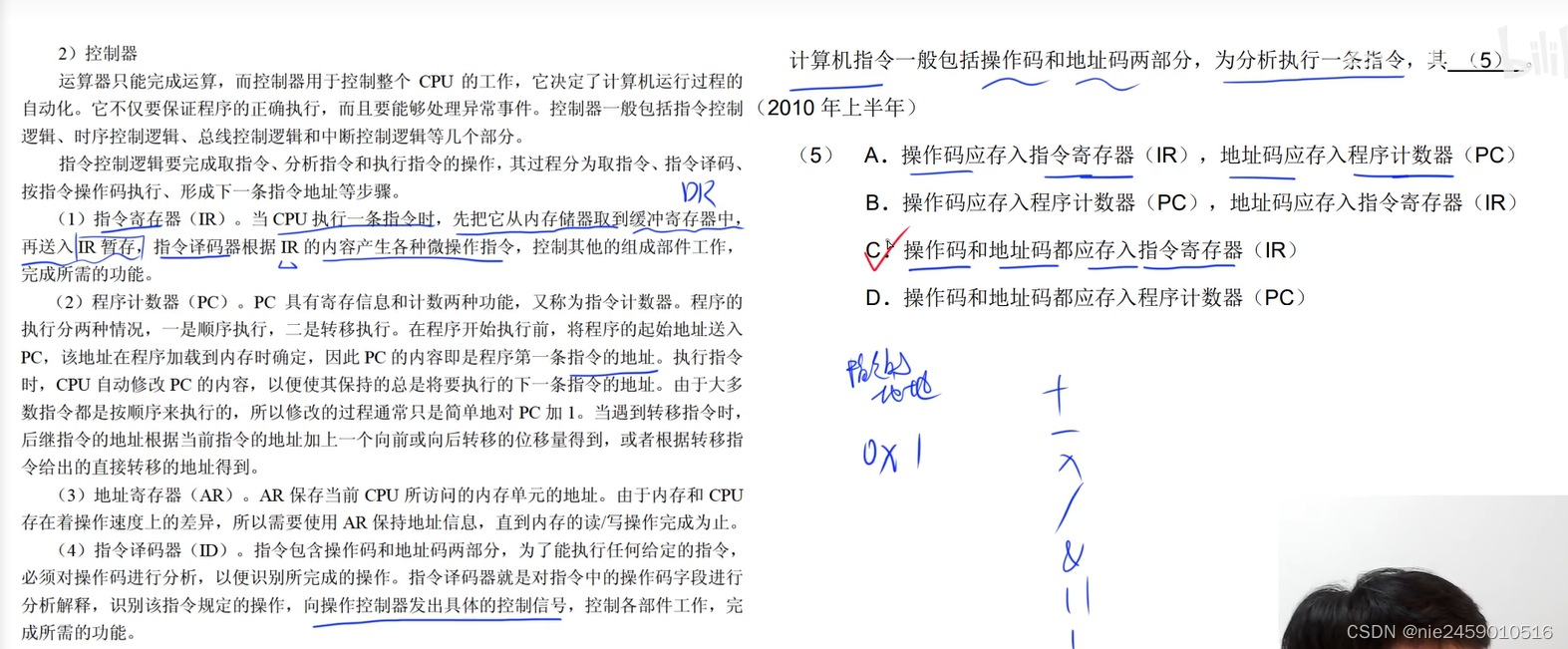

指令寄存器 ir 保存暂存指令(操作码加地址吗等于指令)

地址寄存器 保存当前cpu所访问的内存单元地址

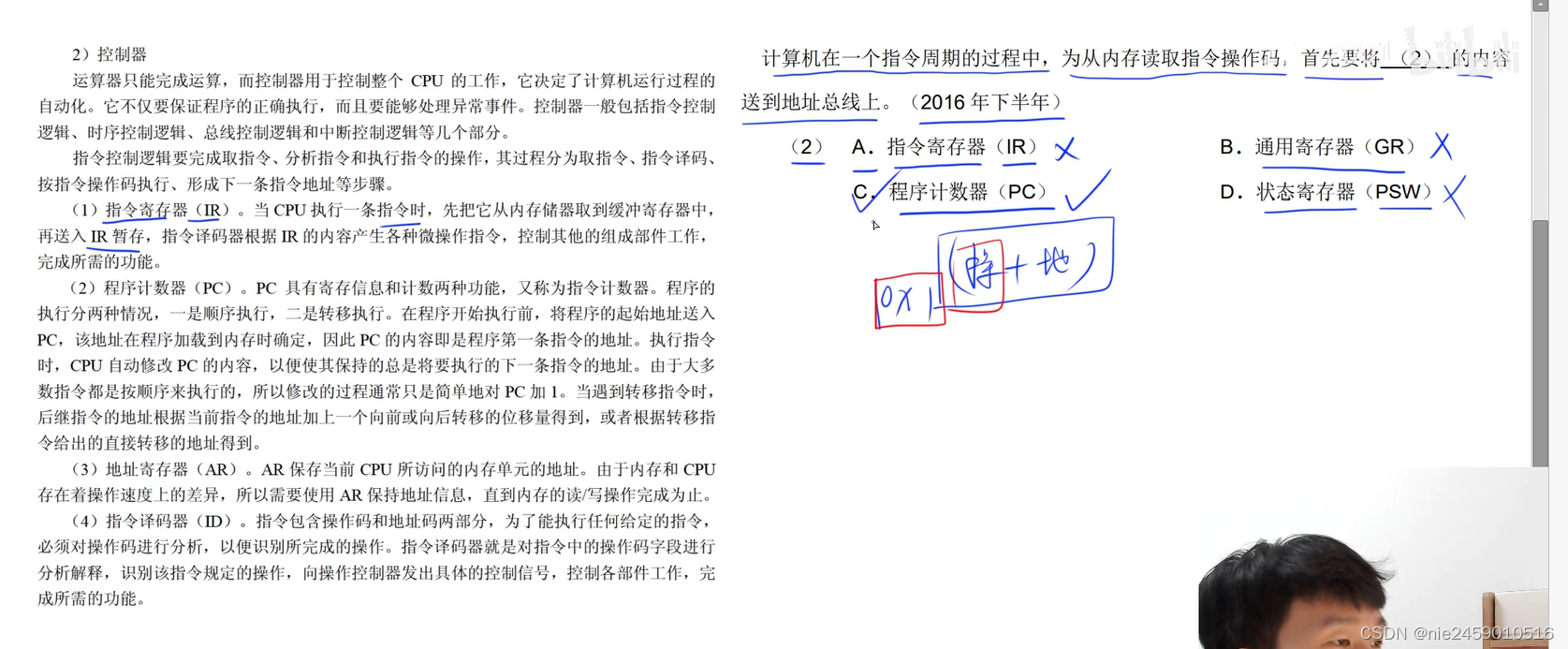

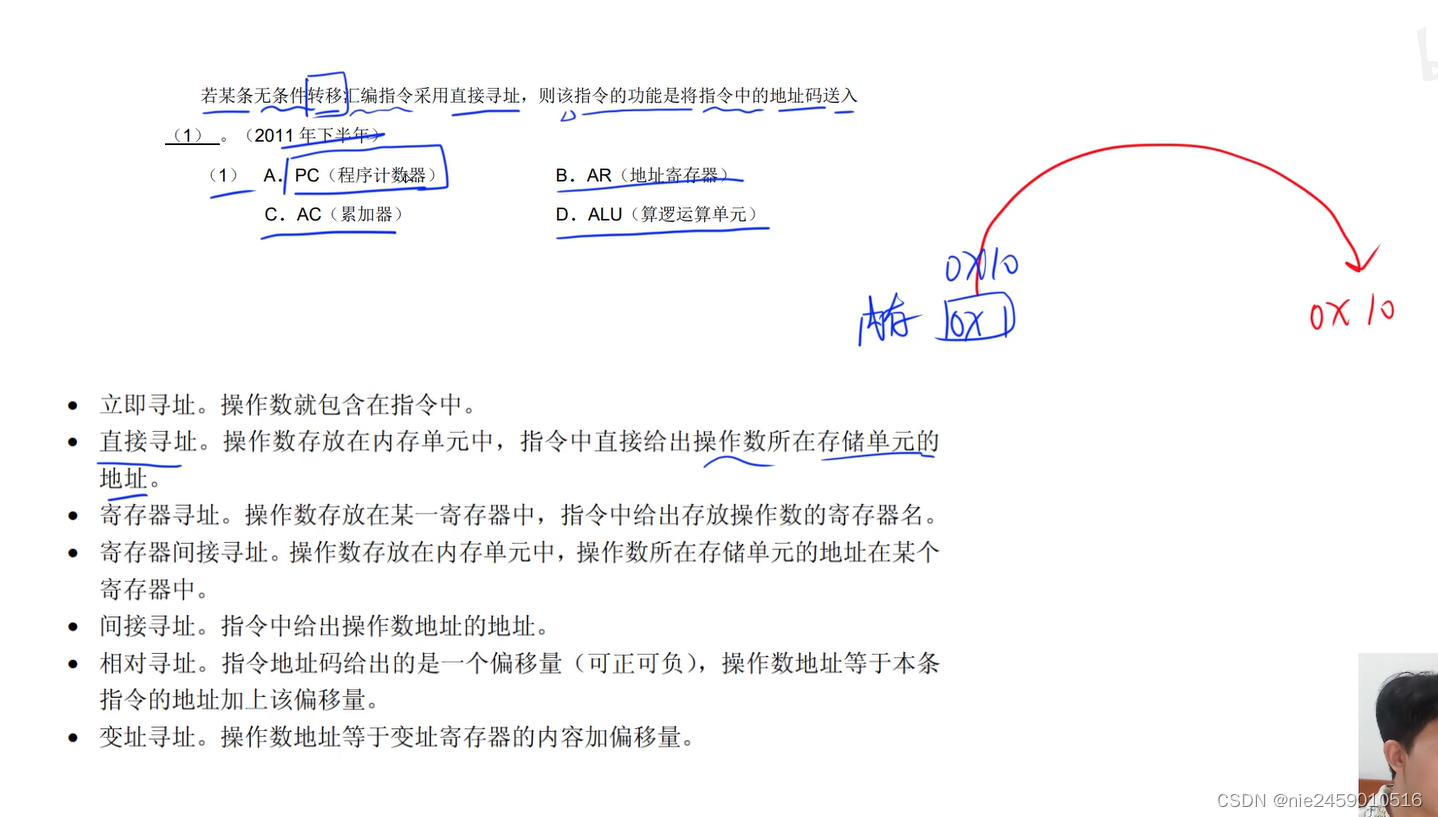

程序计数器 保存的是下一条指令的地址

状态寄存器 标志运算的结果 类似 0()状态寄存器是运算器中的部件, 主要是标志运算的结果 进位/溢出等

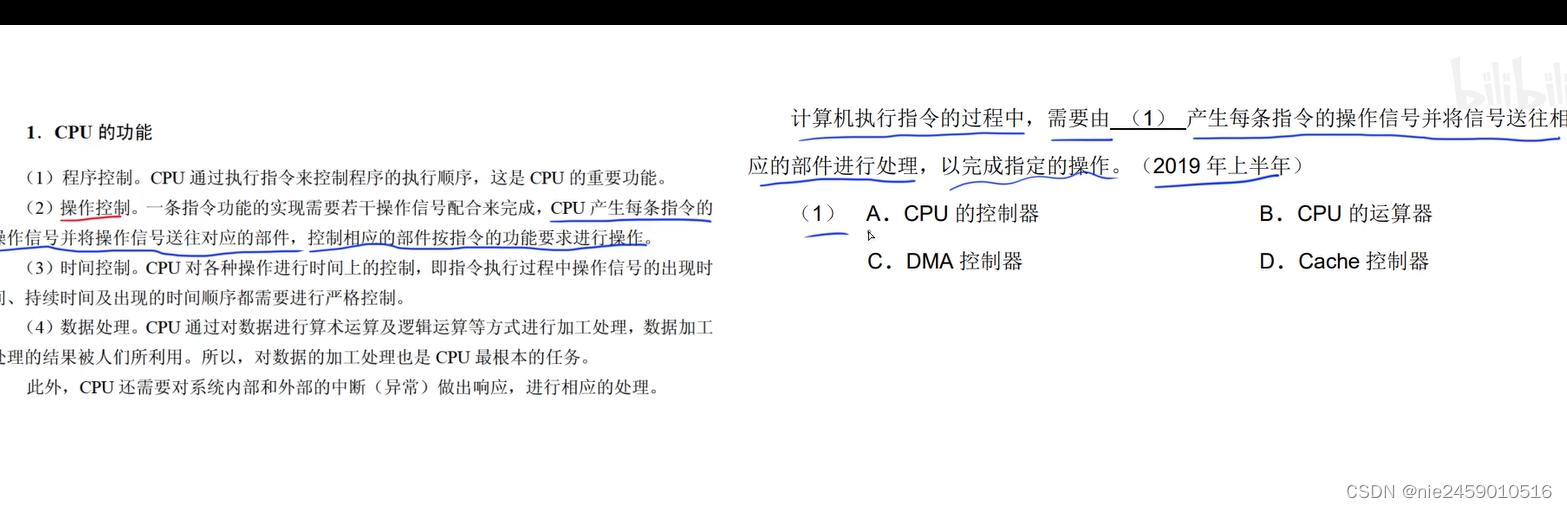

CPU 根据 PC 从内存中取出指令放在DR中 再送入IR暂存 AR保存CPU当前访问的内存单元的地址 ID负责分析解释IR中的指令 并向操作控制器发出具体控制信号

指令=操作码+地址码

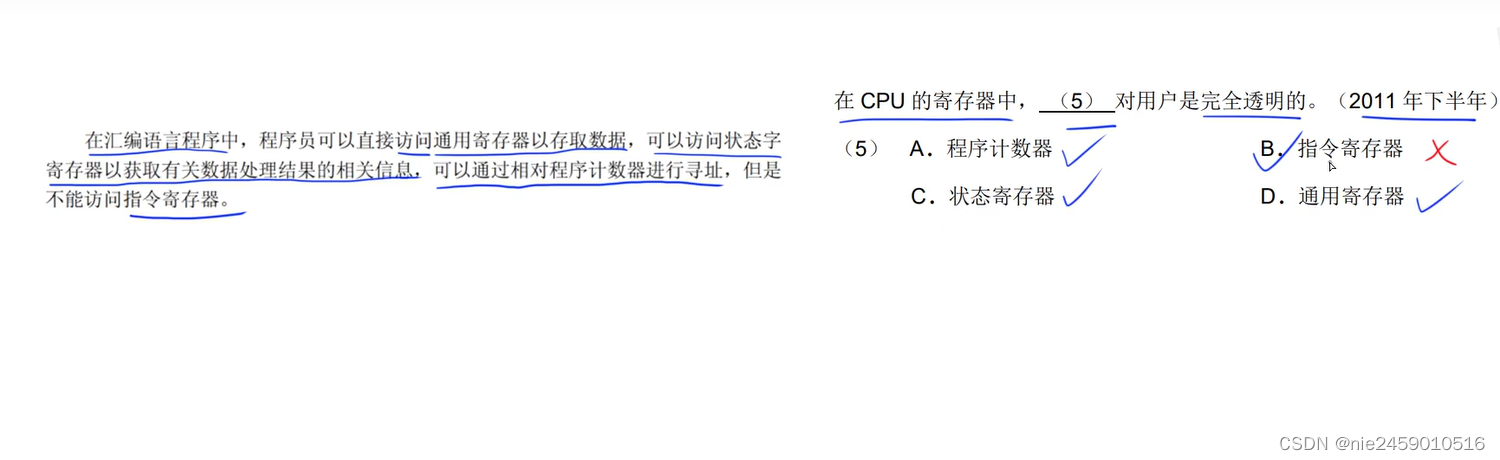

**用户可见:通用寄存器组、程序状态字寄存器(PSW)、程序计数器(PC)、累加寄存器(AC) 用户不可见:指令寄存器(IR)、暂存寄存器(DR)、存储器地址寄存器(MAR)存储器数据寄存器(MDR)

**

译码器是对指令进行译码

运算器只做运算,其他一律控制器来做

数据寄存器是内存和cpu的中转站,把内存保存下来给cpu

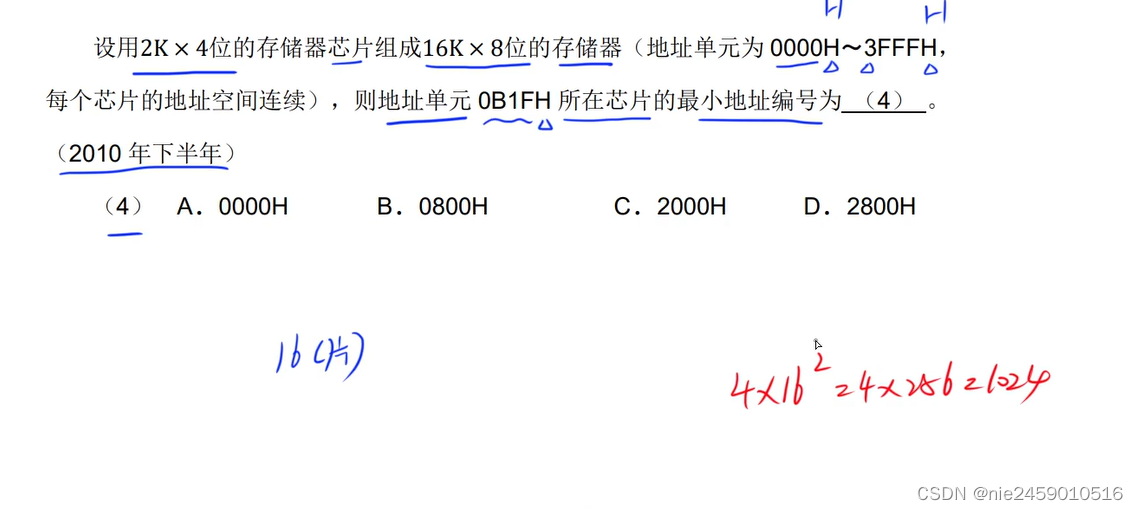

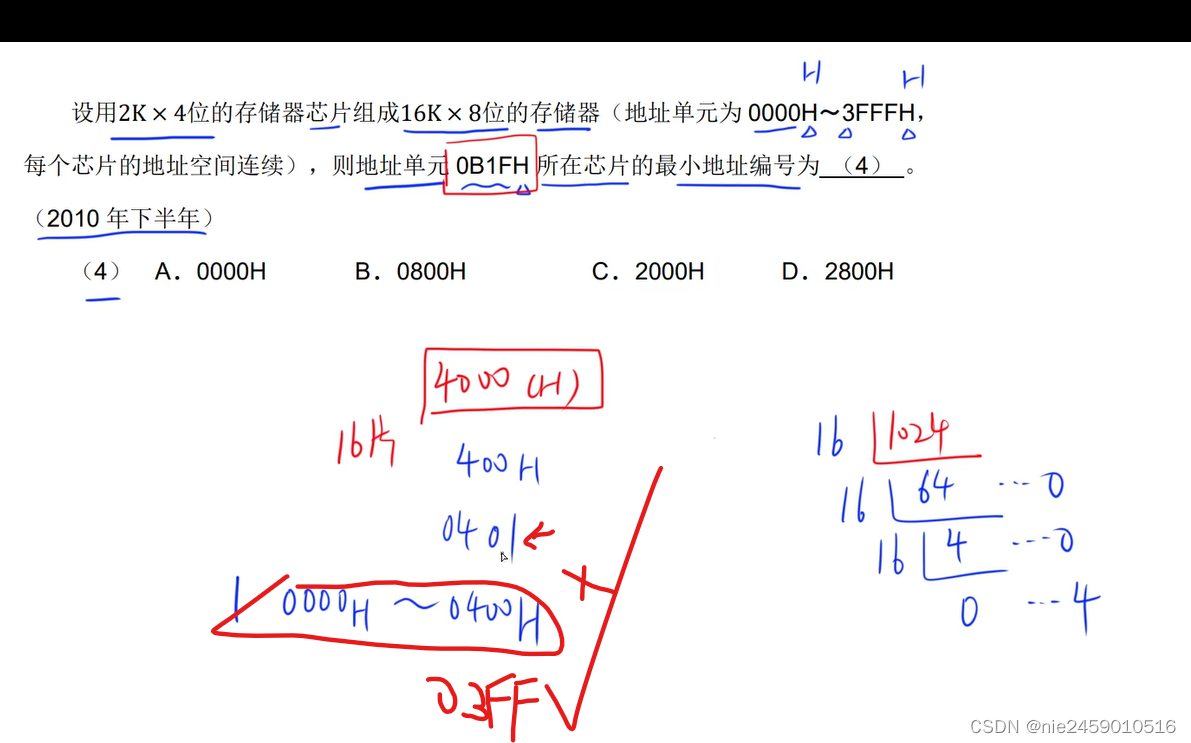

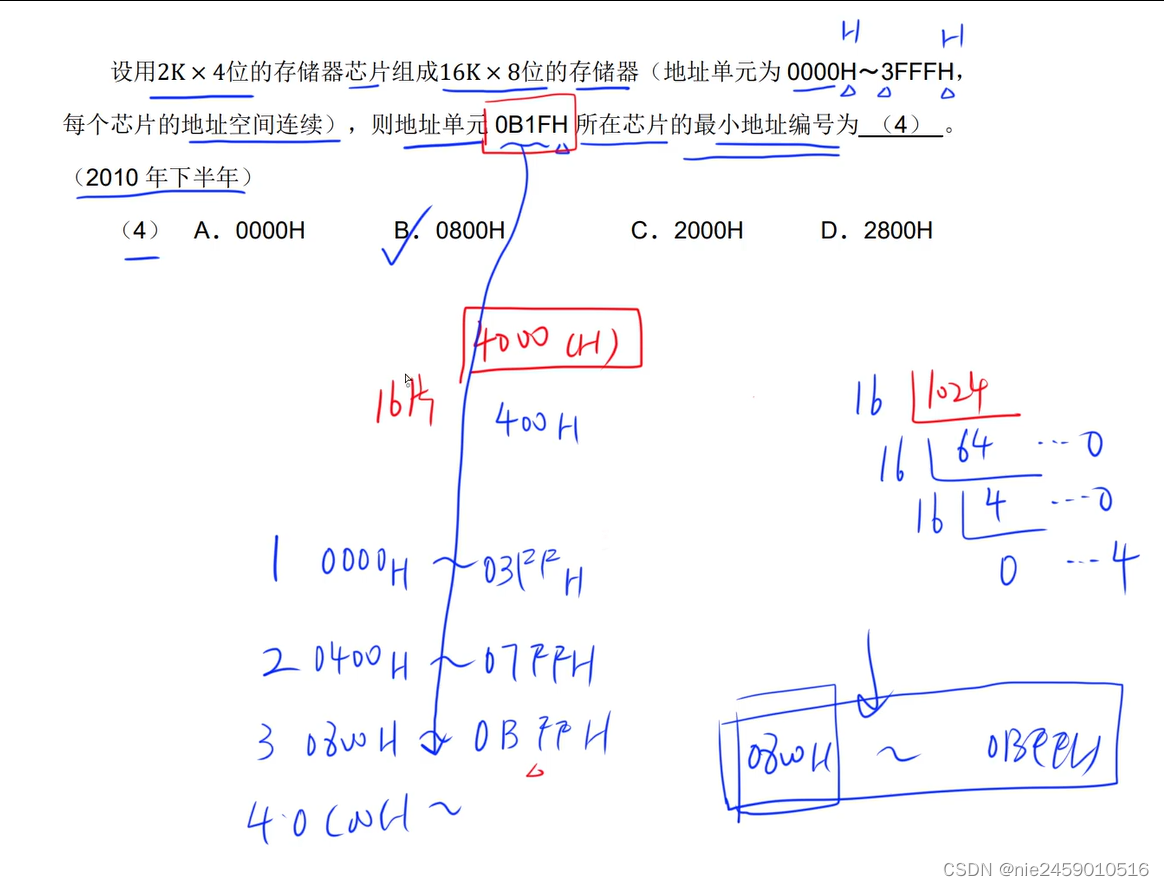

1024是每篇的大小,除16是转换为16进制,得到每篇的地址400h

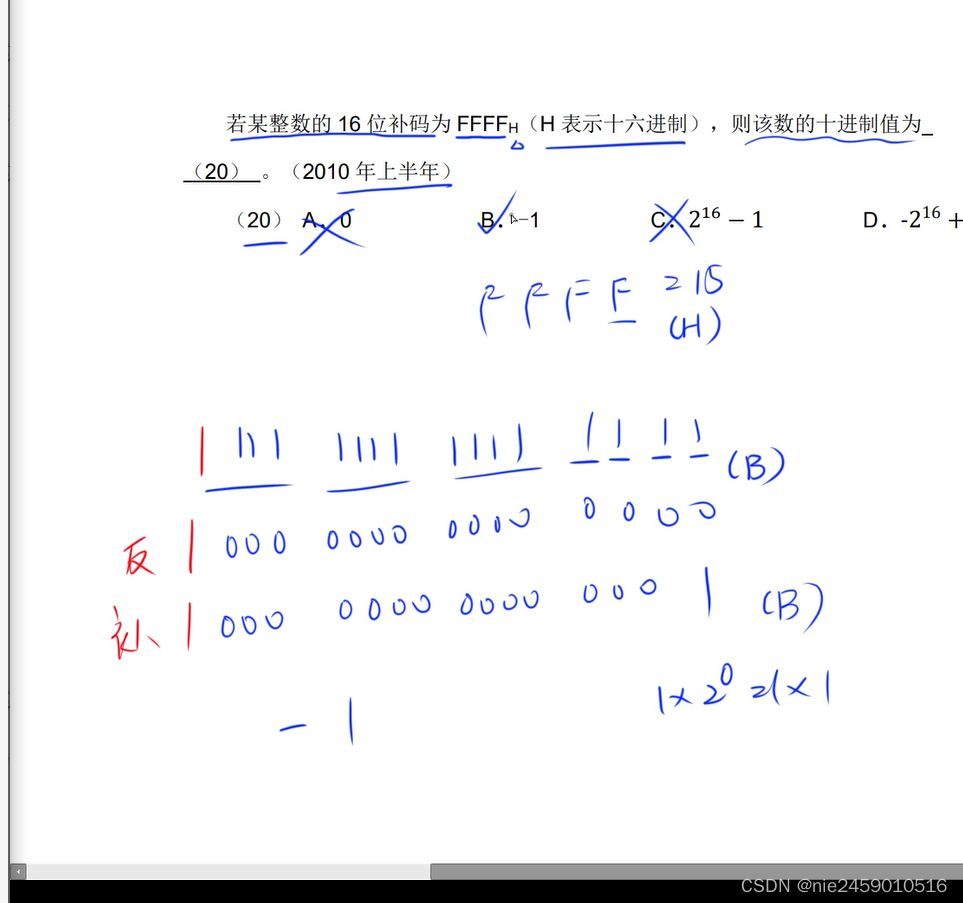

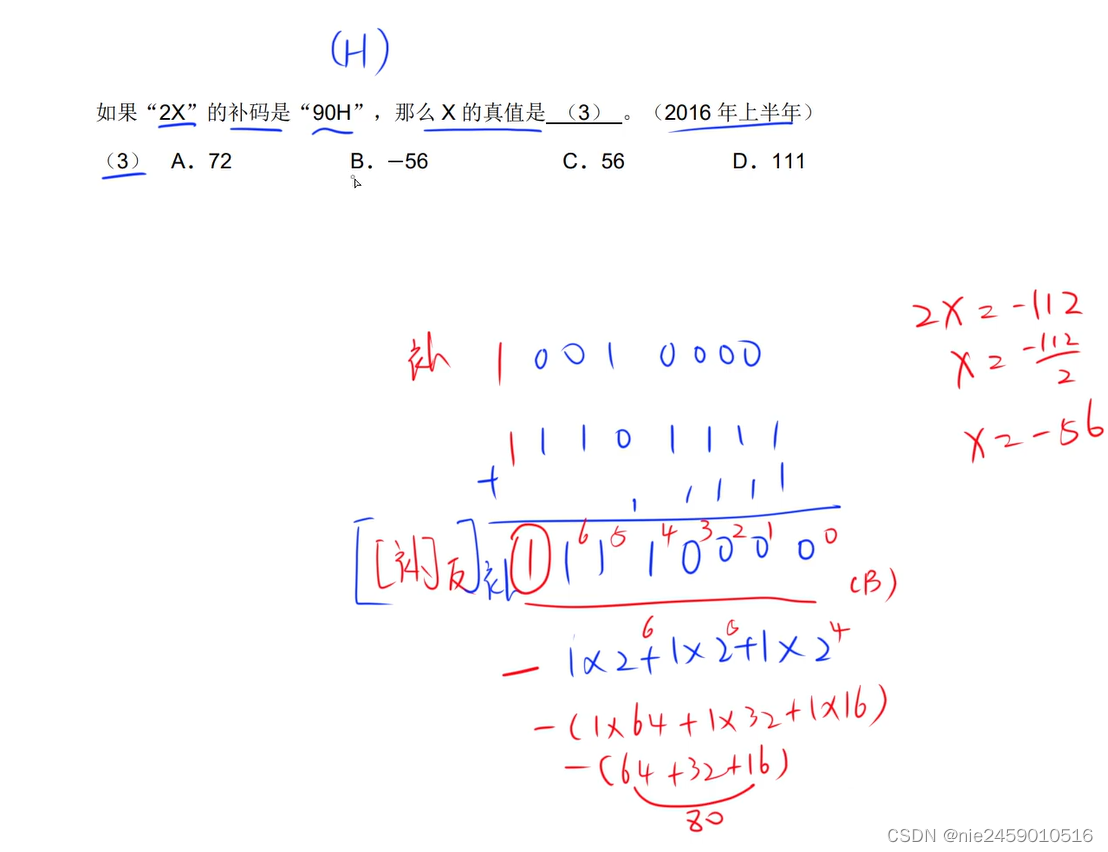

根据题意补码+1取反求得原码,然后转换为十进制,符号位不变

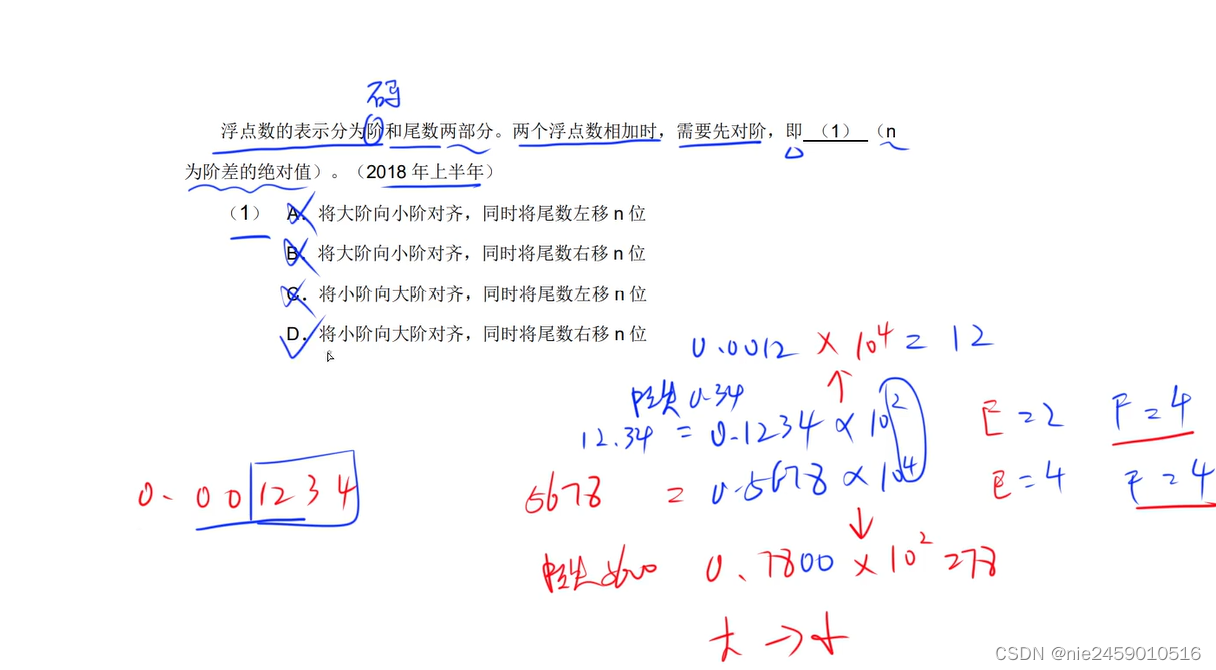

右移是因为移动的整个数字1234

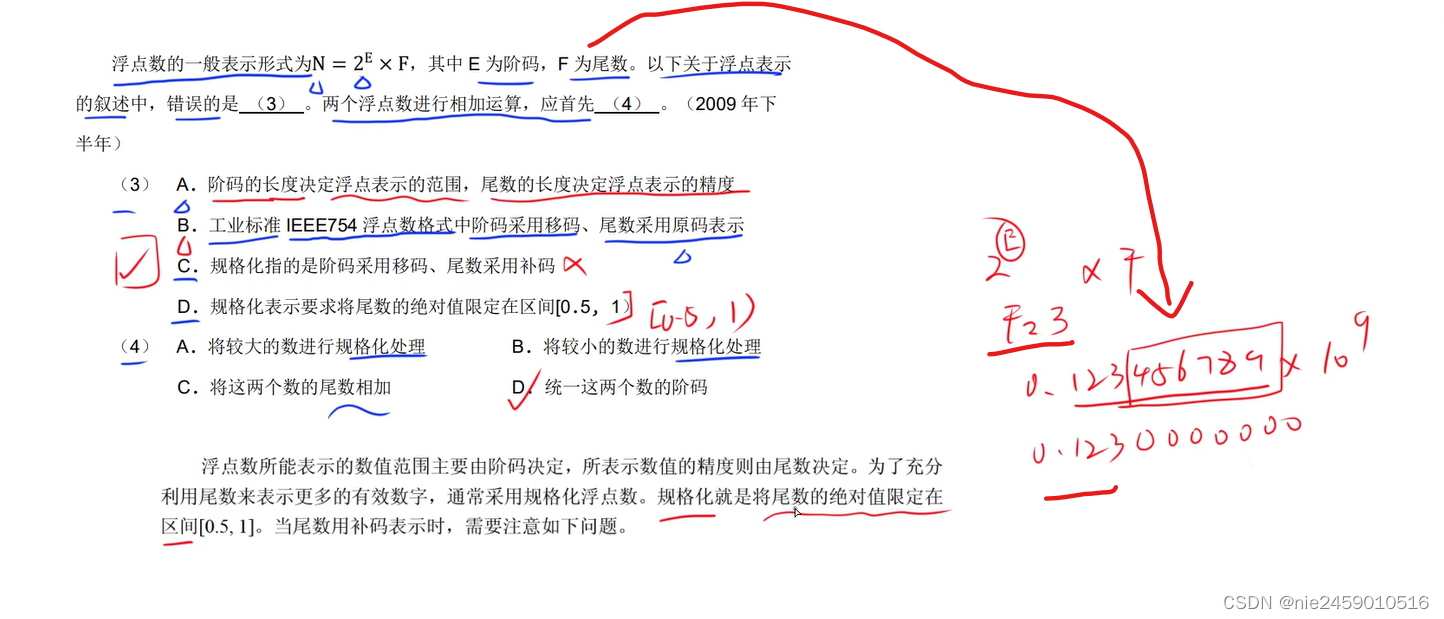

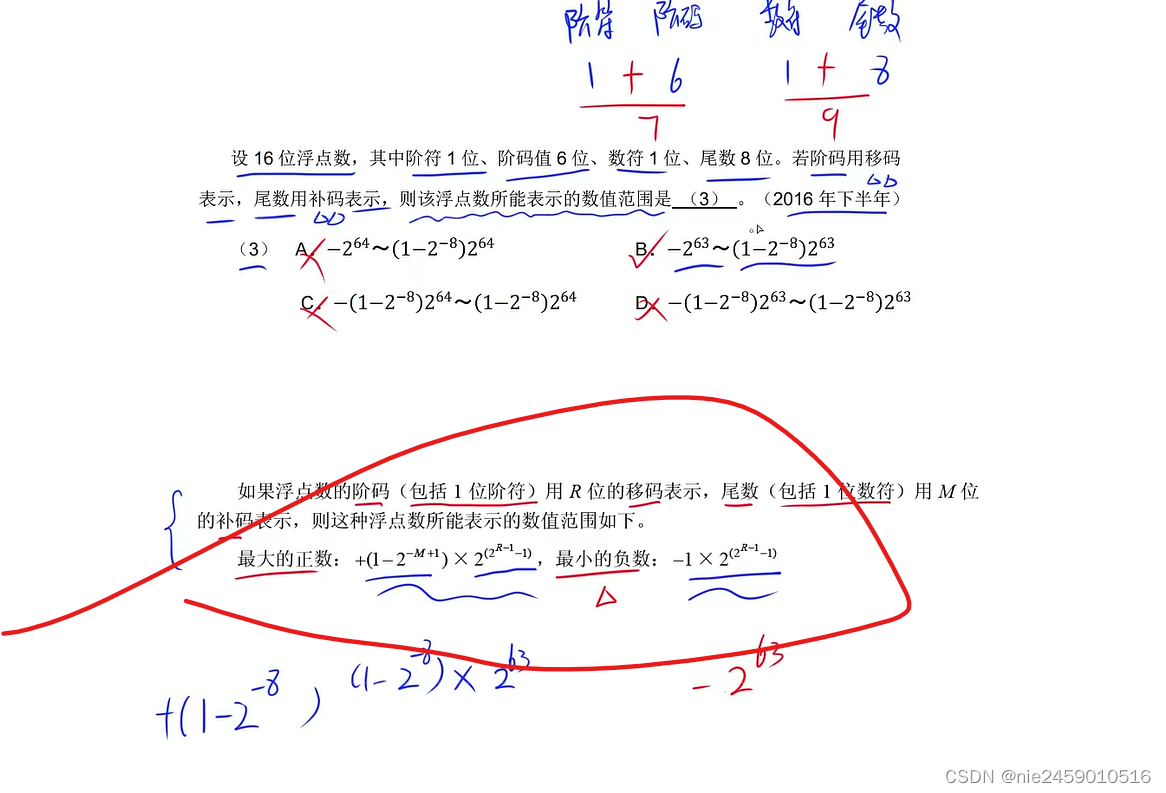

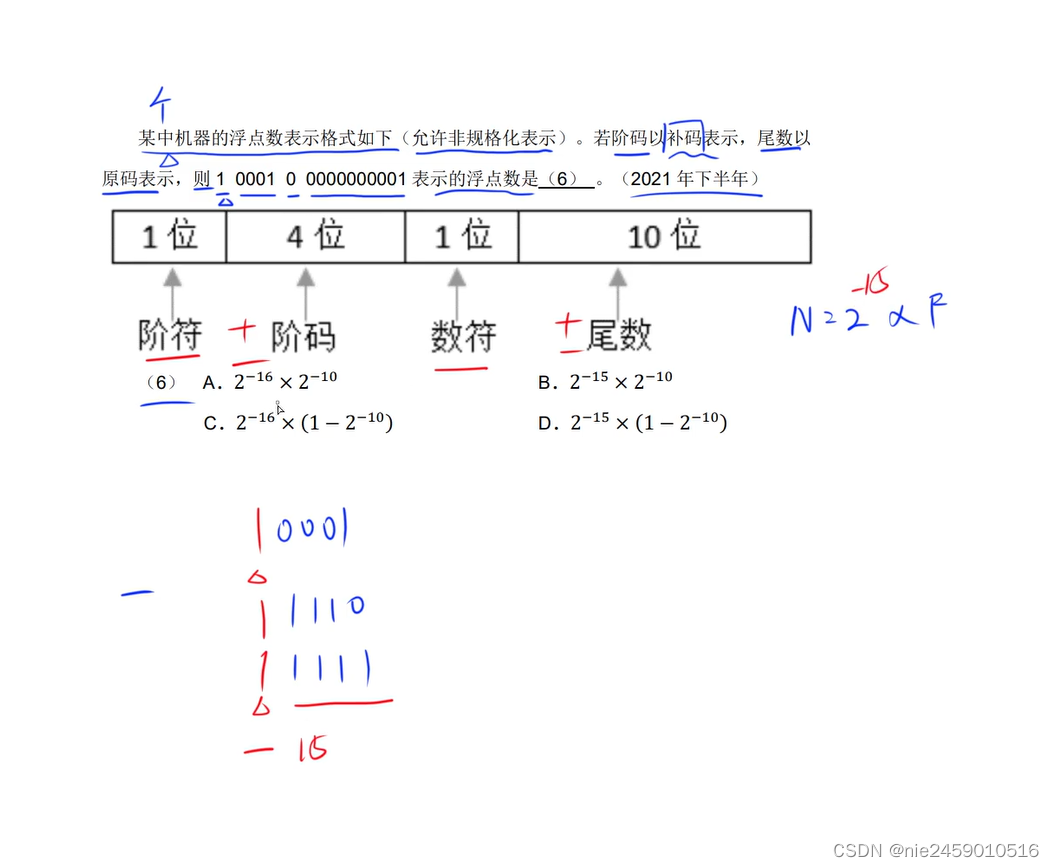

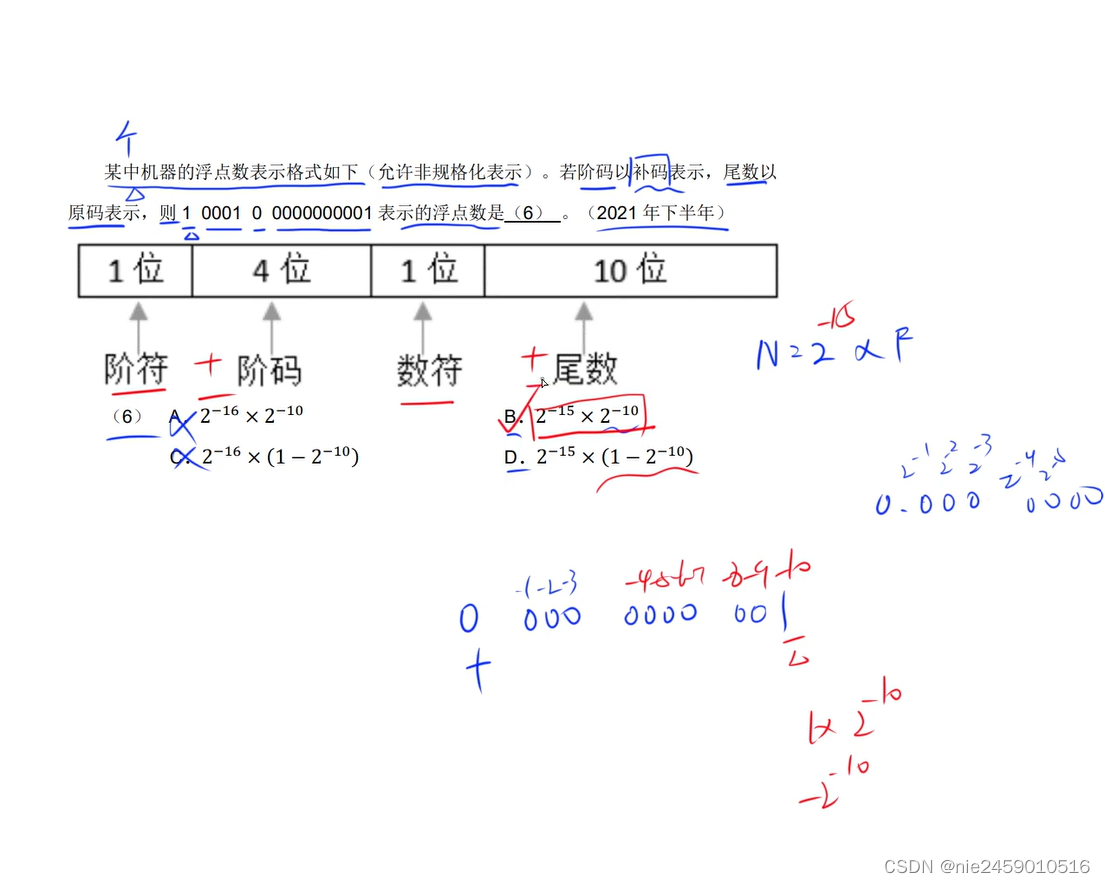

阶符和数符表示符号位

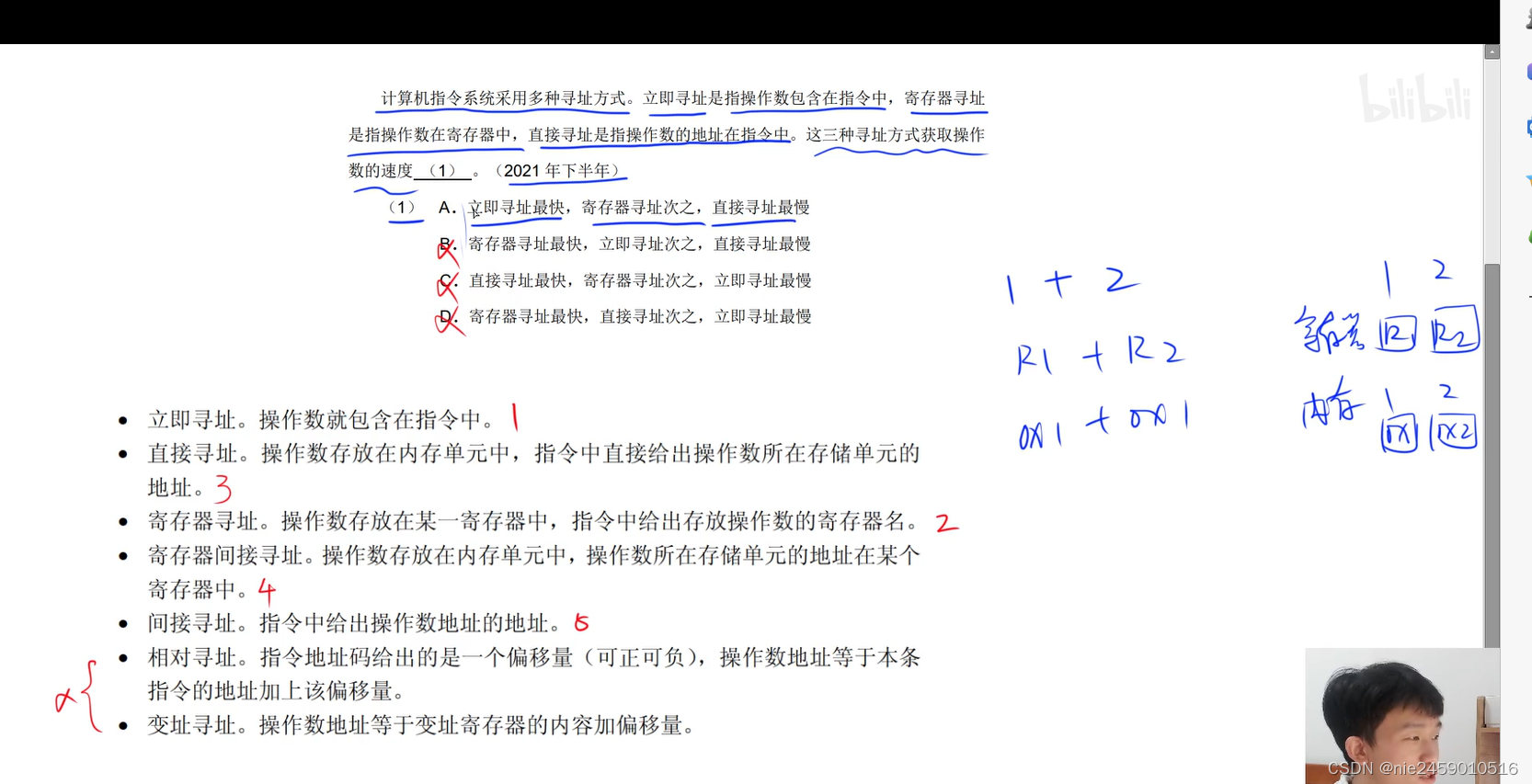

寻址背诵

奇校验 表示有奇数个出错可以检测出

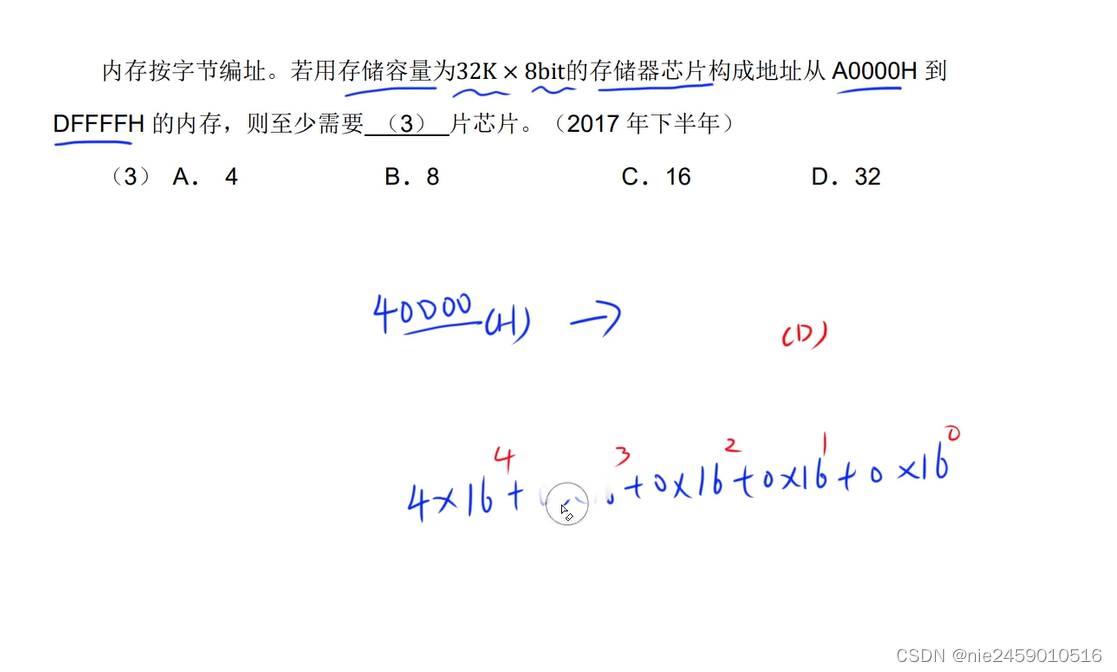

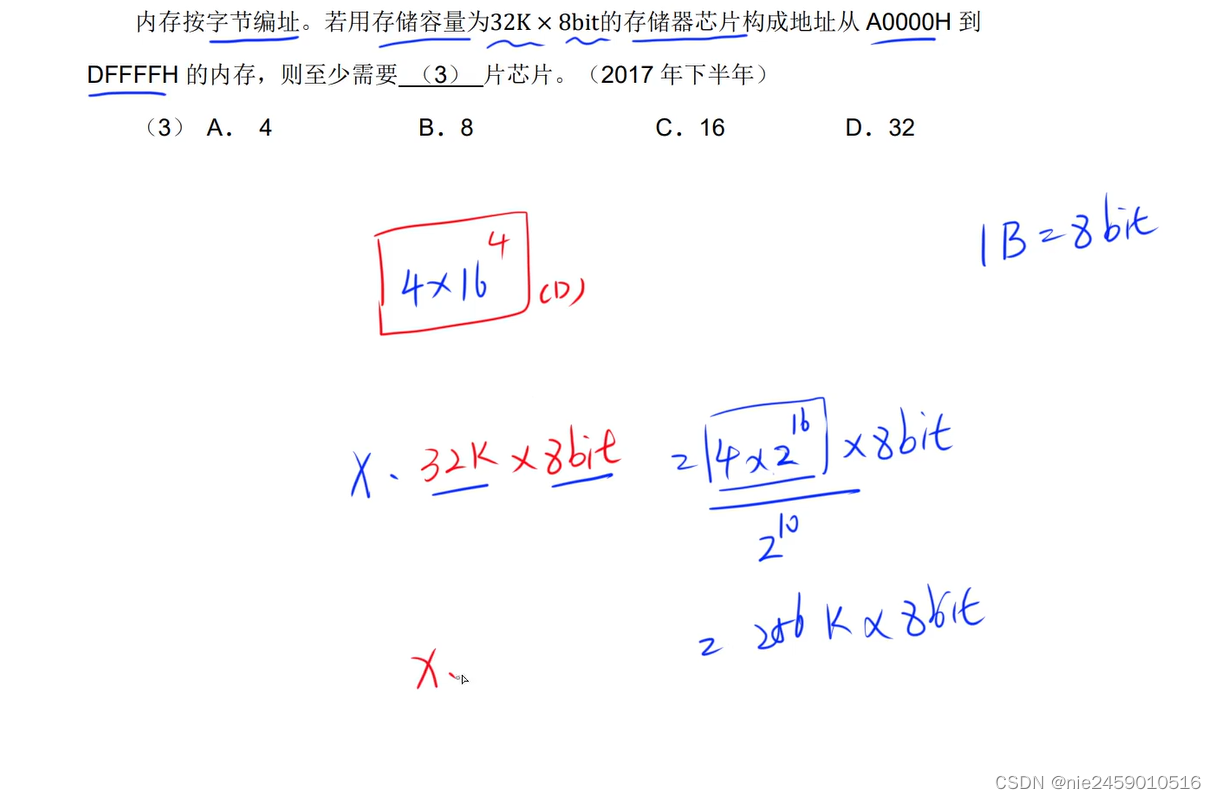

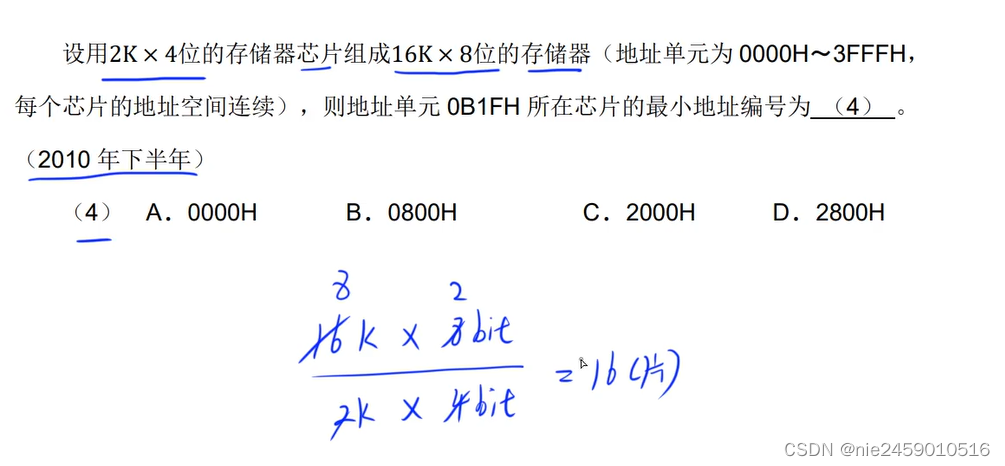

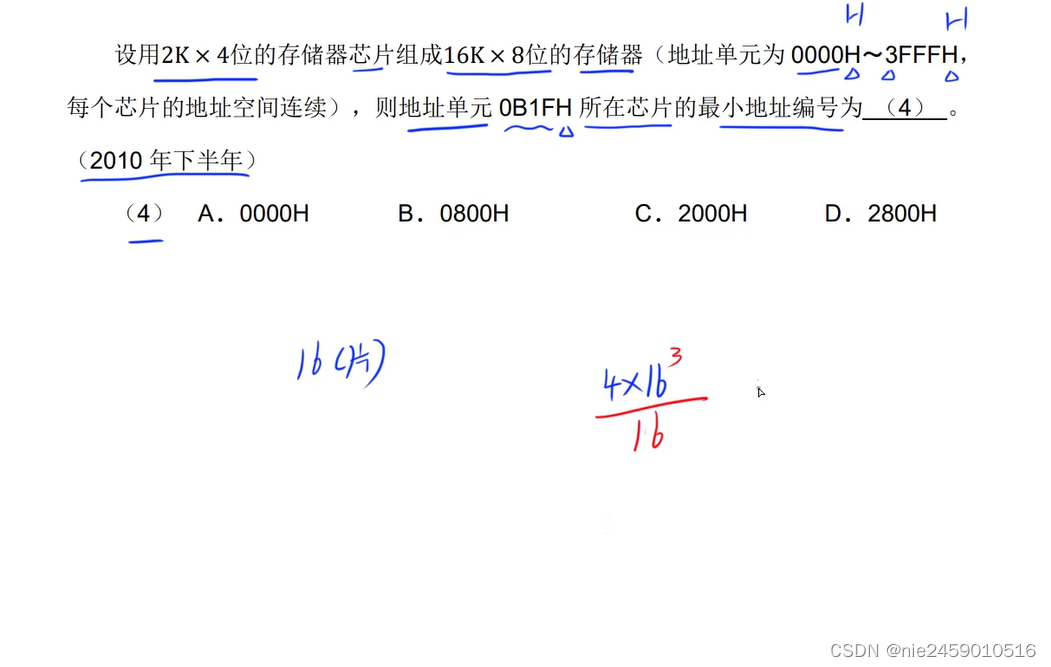

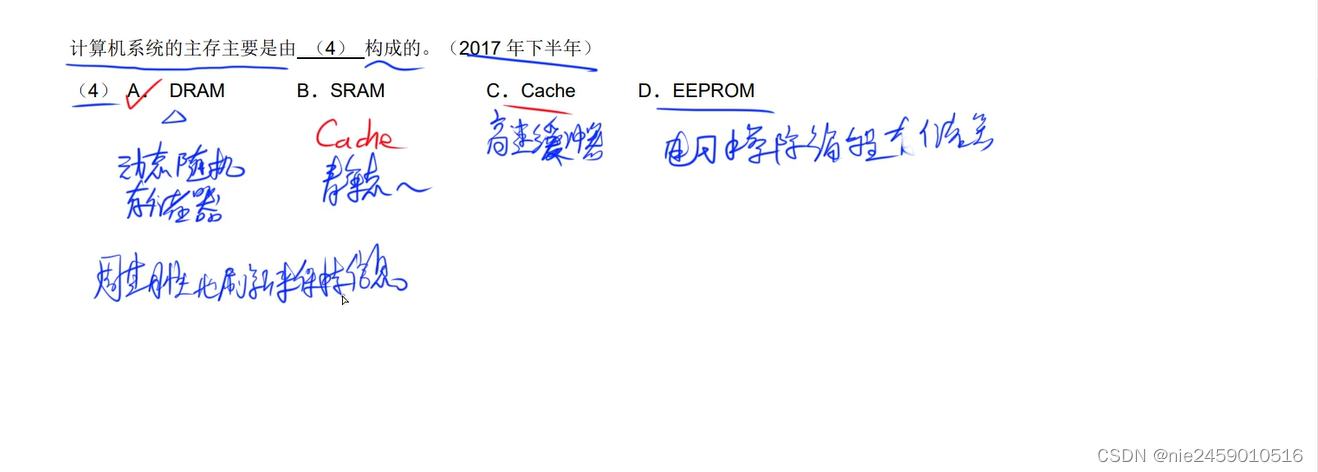

存储器背诵

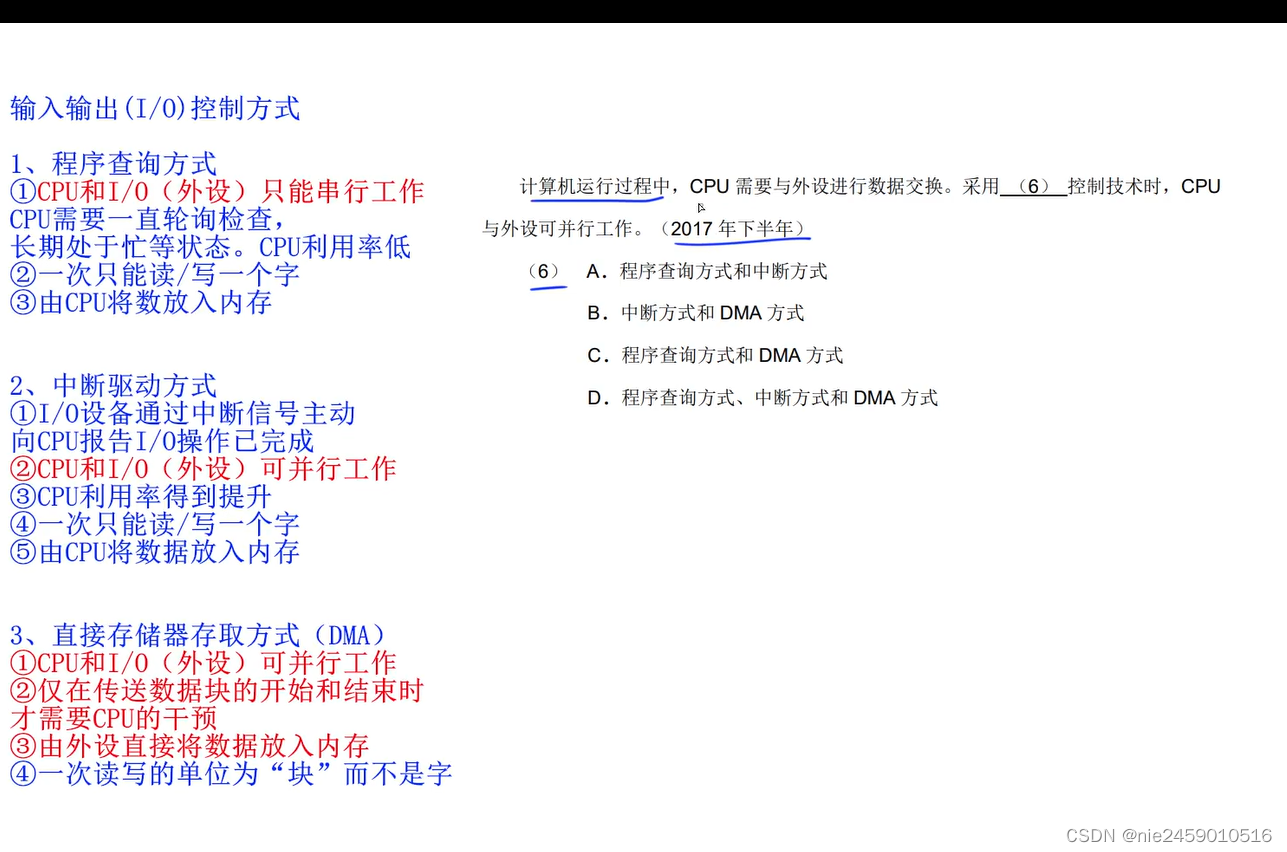

输入输出背诵

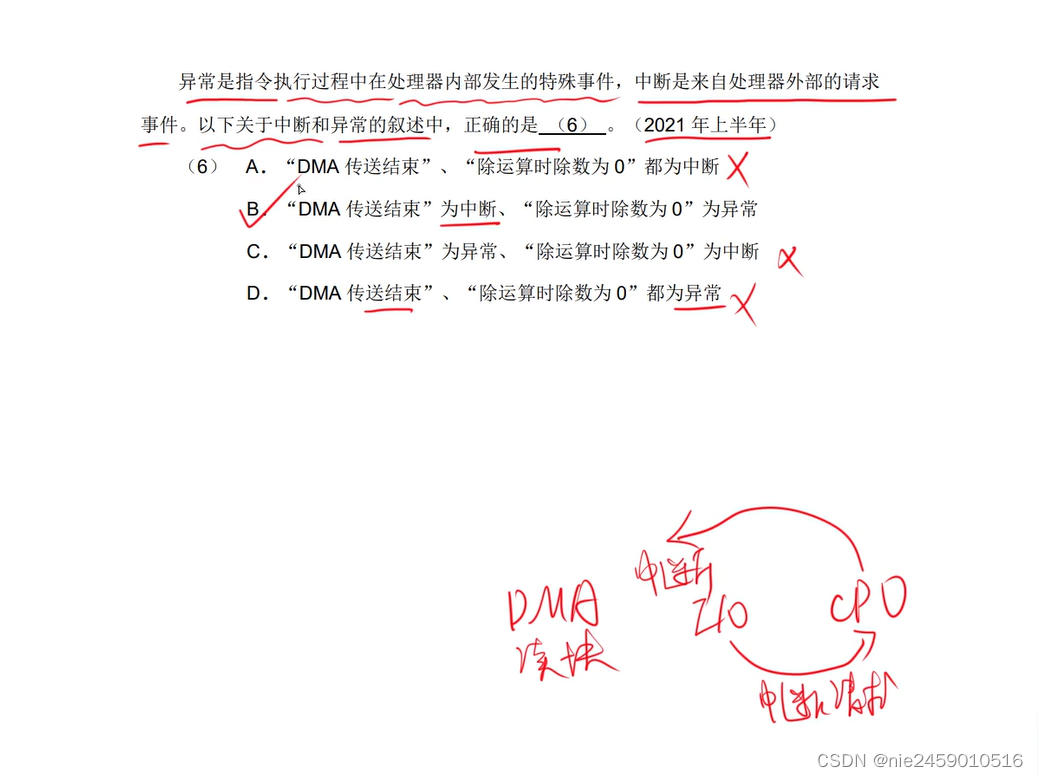

比如程序报错为异常10/0

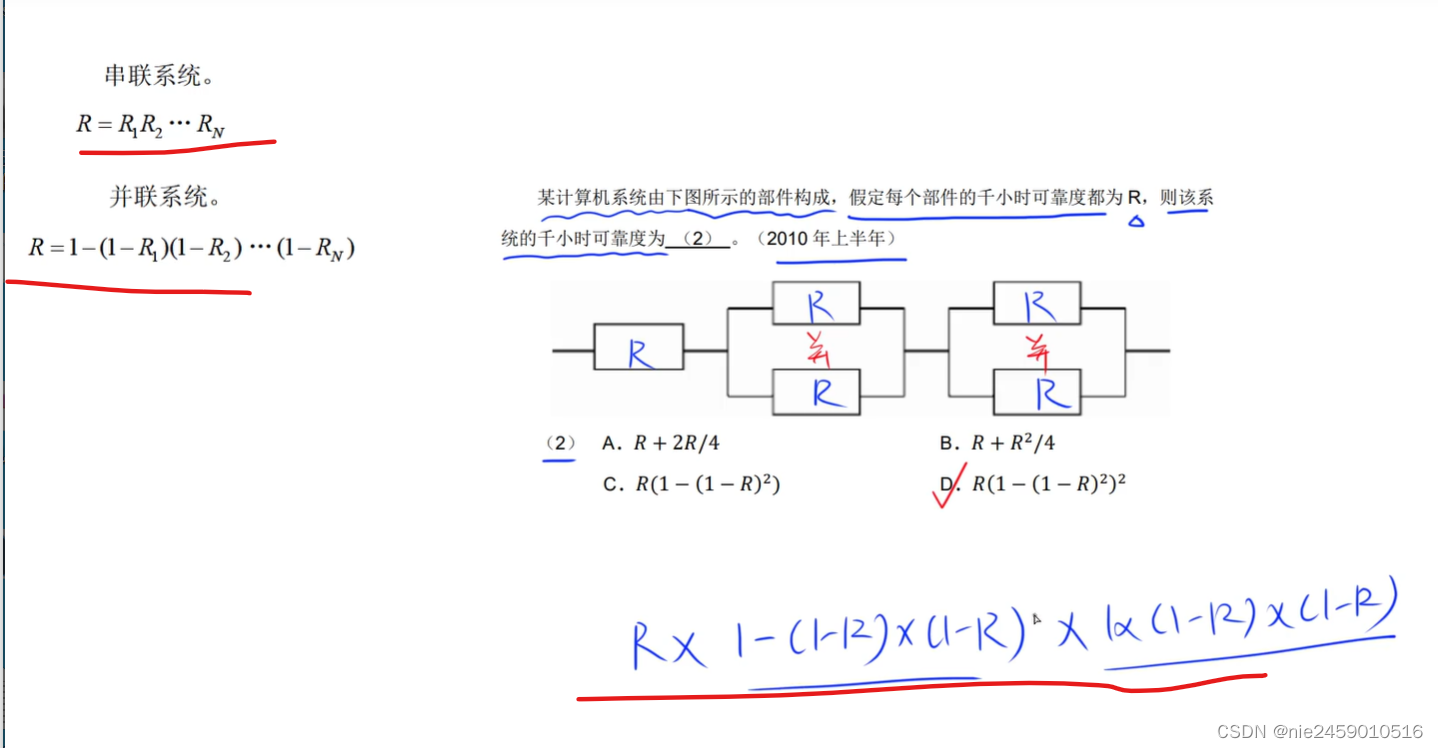

可靠性公式 背诵

这条公式是整体乘下来

大总结

**用户可见:通用寄存器组、程序状态字寄存器(PSW)、程序计数器(PC)、累加寄存器(AC) 用户不可见:指令寄存器(IR)、暂存寄存器(DR)、存储器地址寄存器(MAR)存储器数据寄存器(MDR)

数据寄存器是一个中转站

指令寄存器 ir 保存暂存指令(操作码加地址吗等于指令)

地址寄存器 保存当前cpu所访问的内存单元地址

程序计数器 保存的是下一条指令的地址

状态寄存器 标志运算的结果 类似 0()状态寄存器是运算器中的部件, 主要是标志运算的结果 进位/溢出等

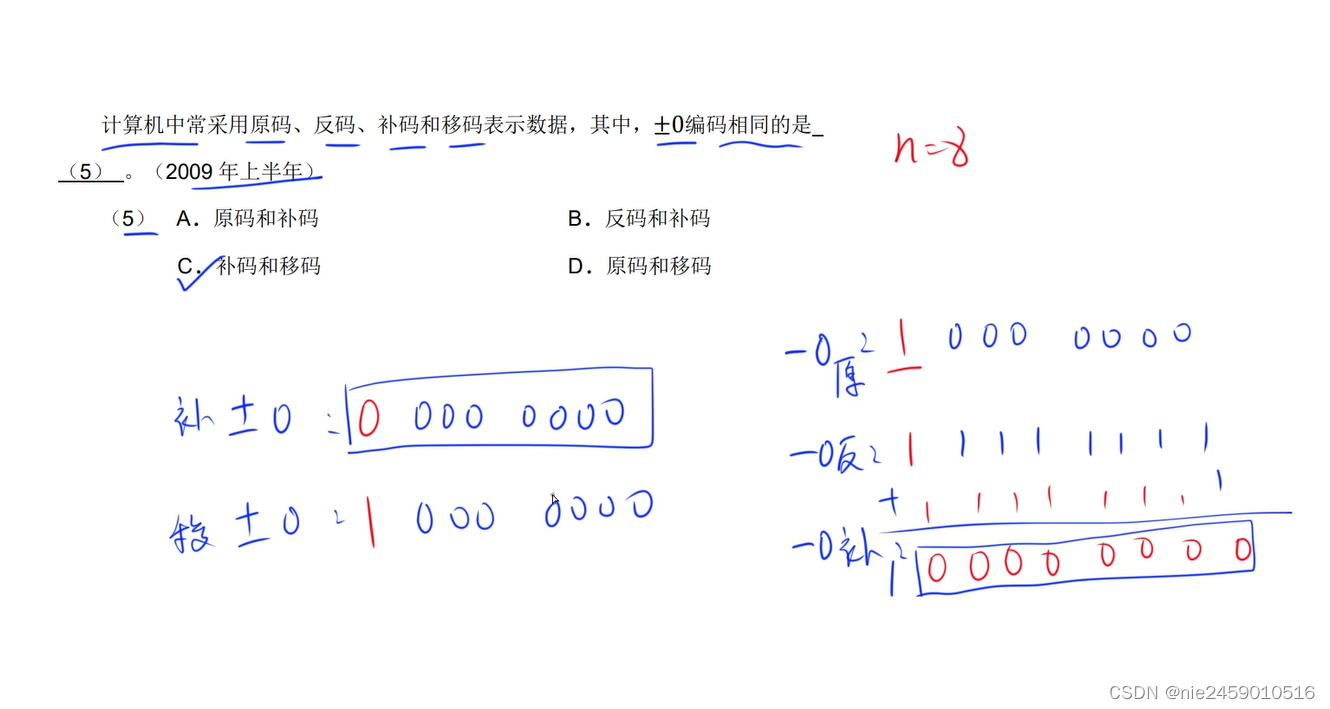

计算机中采用补码计算是因为他可以简化计算机运算部件的设计(把减法当成加法)

定点表示法小数点不需要占一个存储为

总位数相同的情况浮点数表示更大的书

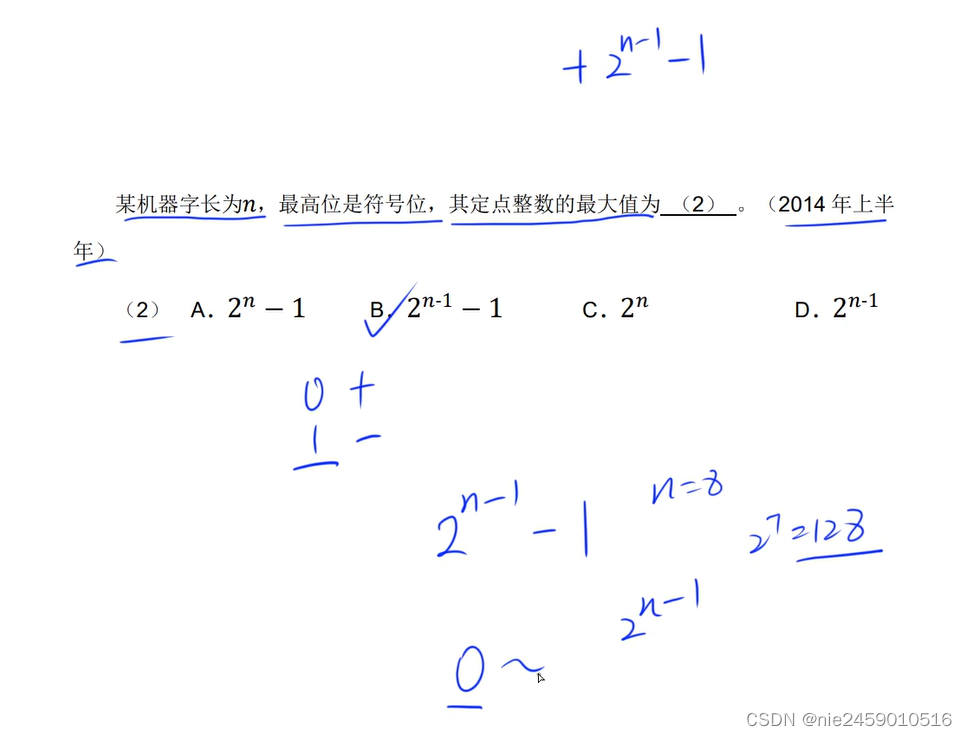

定点数的补码和姨妈克表示2n次方个树

采用不同寻址方式目的是扩大寻址空间提高编程灵活性

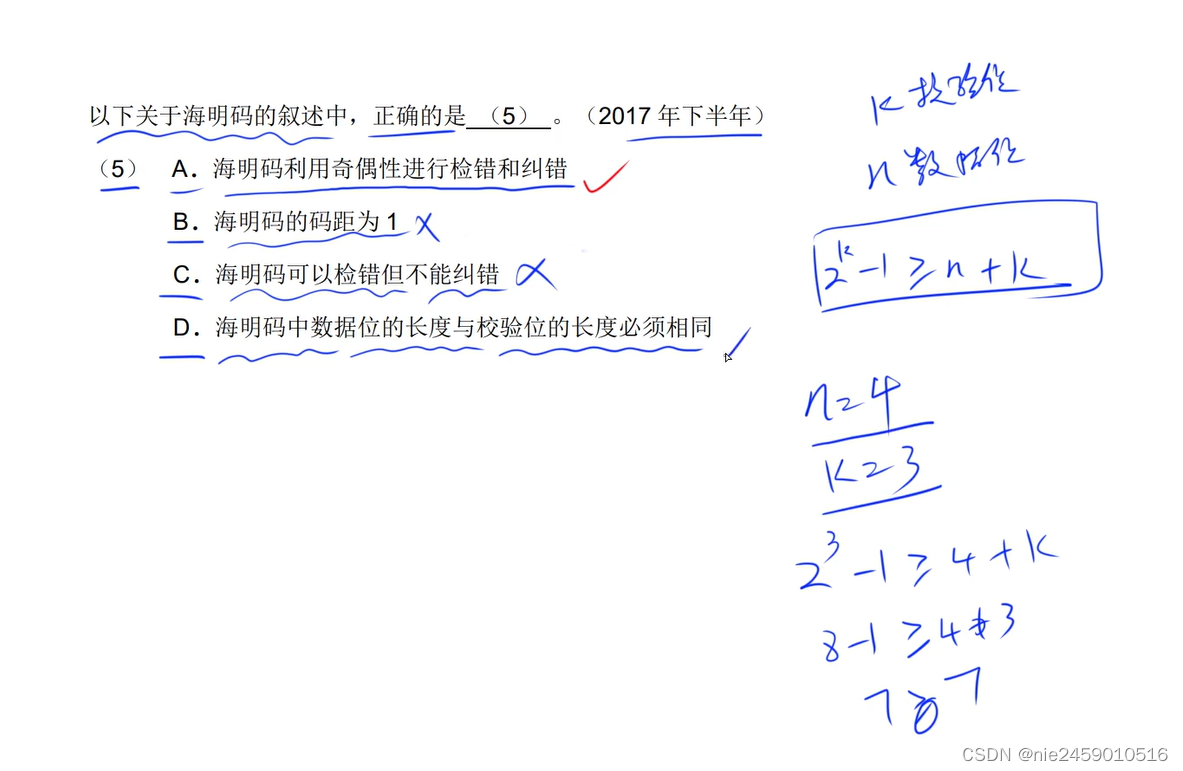

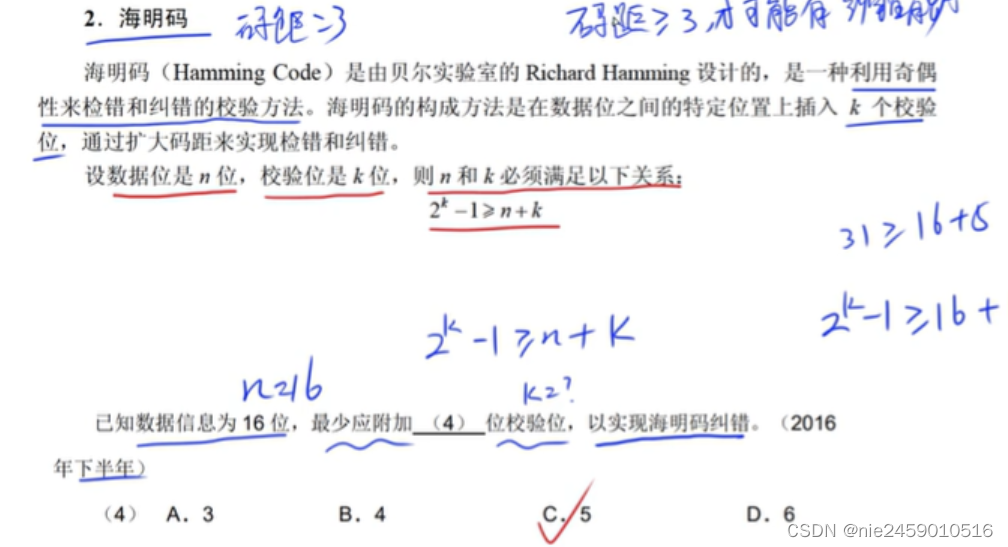

海明码lion给多组数位的奇偶性来检错和纠错 等于2检错 大于等于3纠错

循环冗余校验码不能纠错,海明码可以。可以检错d=2

2的k方-1=>n+k

奇校验 表示有奇数个出错可以检测出

循环冗余校验码k个数据位后跟r个校验位 采用模2运算

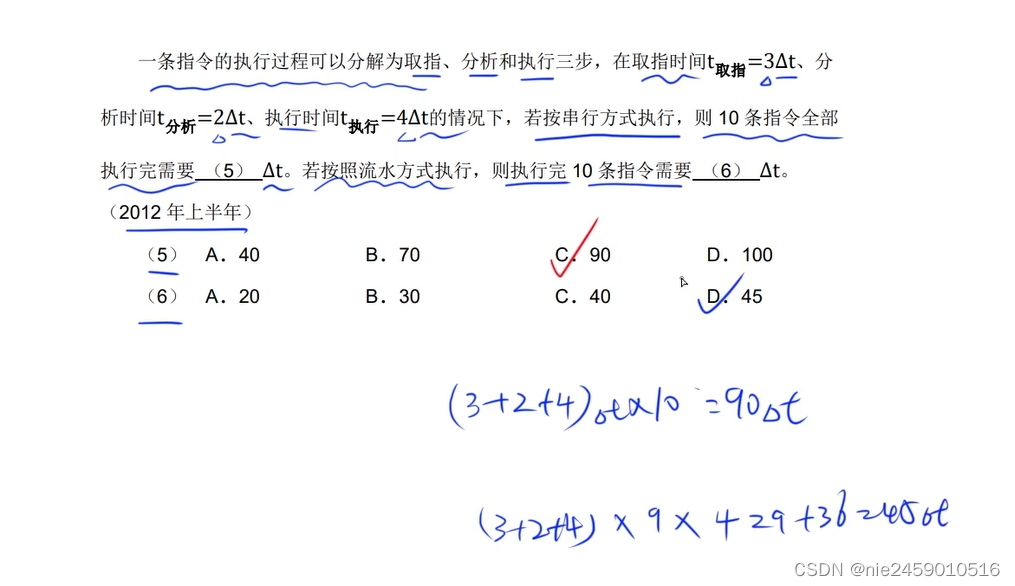

流水线公式(一条指令执行所需总时间)+(n次数-1)x(最长的一个时间段)

操作周期:取最长时间段

吞吐率:取最长时间段的倒数

执行n条指令的吞吐率:n除流水线公式

流水线提高设备利用率

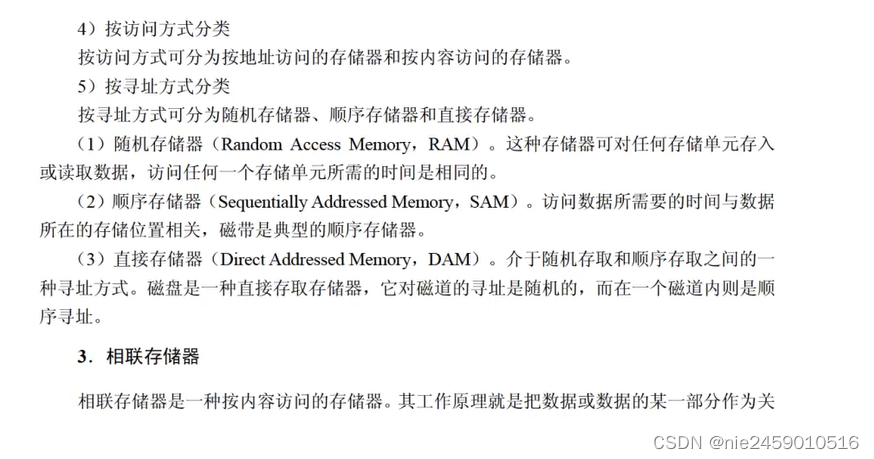

相联存储器是按内容访问

按寻址方式划分的存储器有随即顺序直接

主存和辅存是常用虚拟存储器

闪存相当于u盘以块为单位进行删除操作

空间局部性:访问当前存储单元后还可能访问相邻的

时间局部性:被访问的存储单元不久的将来又被访问成为时间局部性

cache设计思想是合理成本下提高命中率

直接映像冲突最多,组相联中等 全相联映像冲突最少

cache与主存地址的映射是由硬件自动完成的

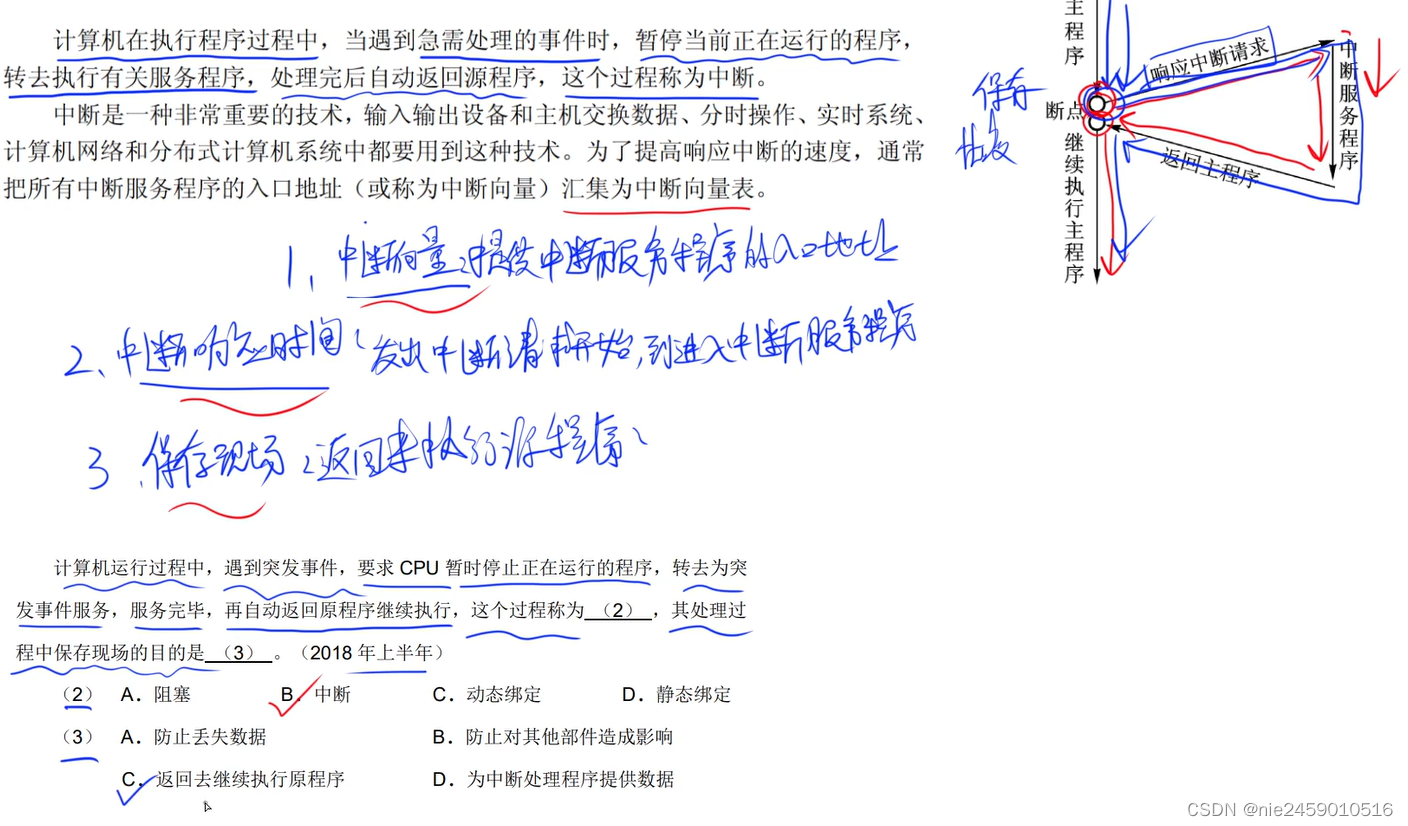

中断向量:相应中断请求就是根据中断向量相应的。它可以提供中断服务程序的入口地址

中断响应时间:发出中断请求开始,到进入中断服务程序

保存现场:返回来执行源程序

dma直接存储器存取方式无需cpu干预

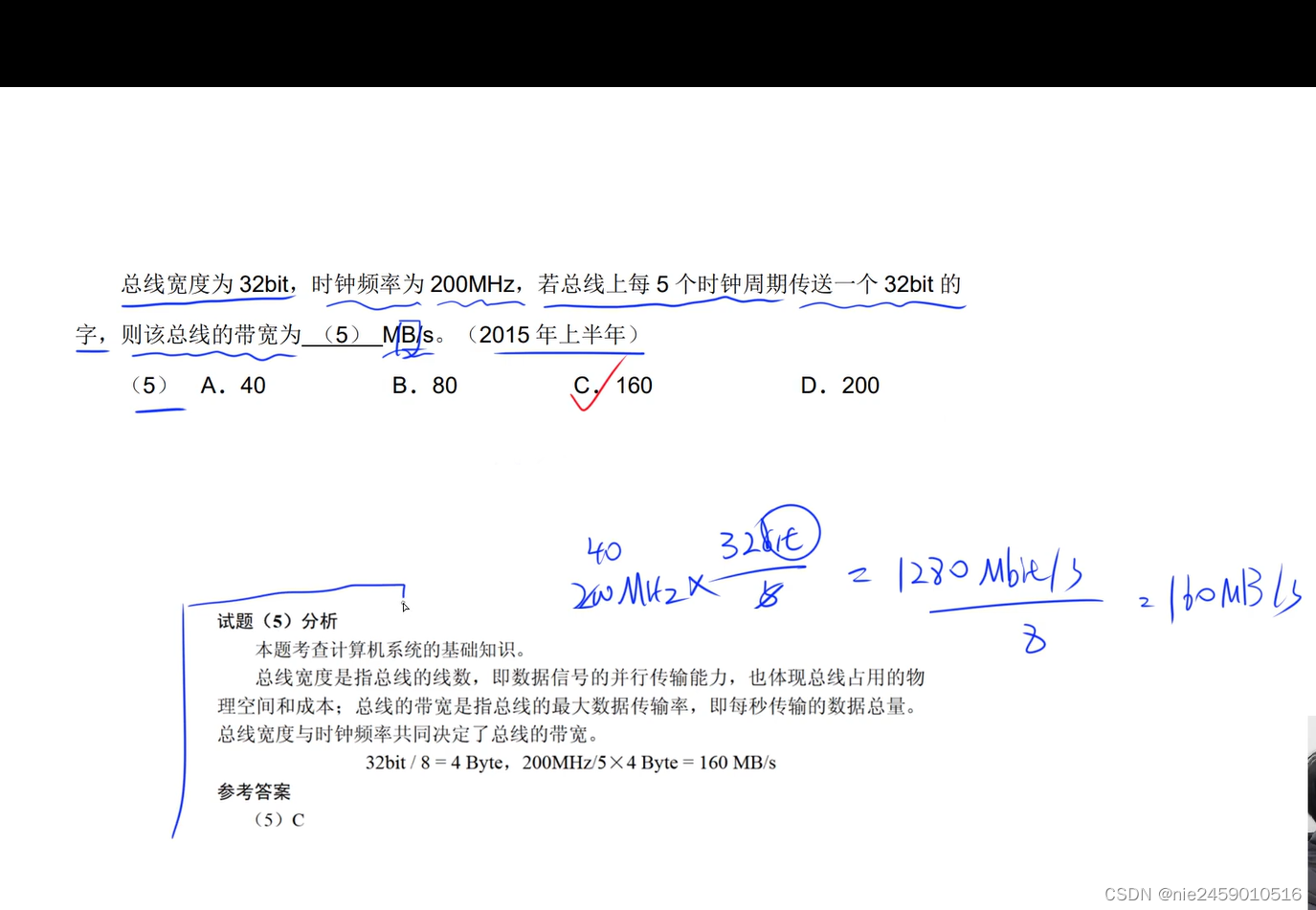

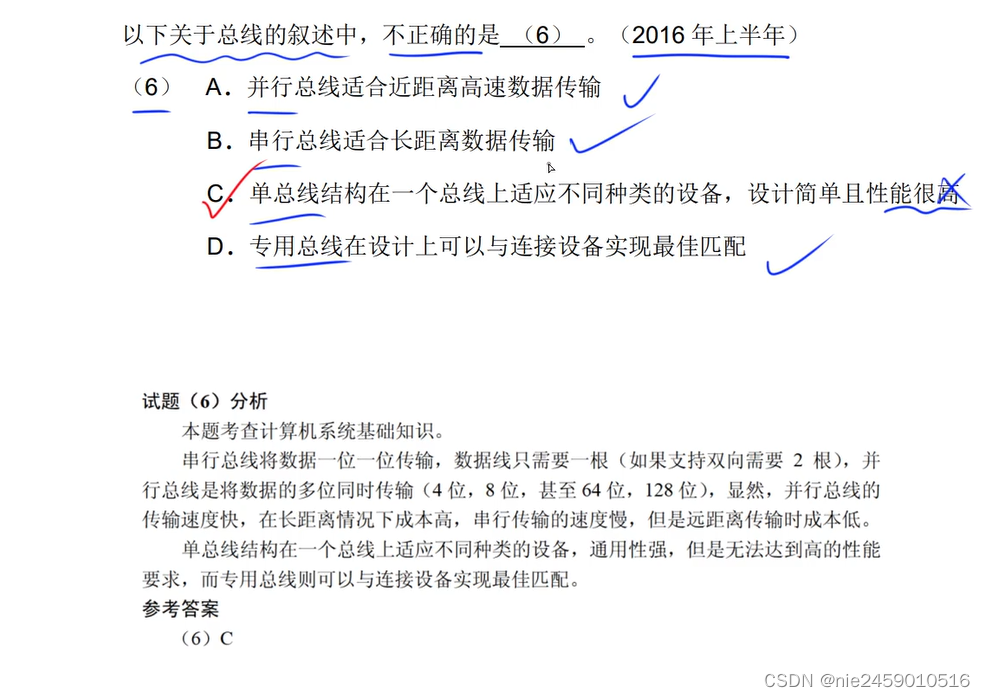

总线包括数地控

4gb等于2的32次方

采用总线结构可以减少信息传输线的数量

系统总线包括isa eisa pci

pci点对点 内总线并行

scsi并行外总线

私钥解密签名 公钥加密验证

私钥无论如何都不能给

保温摘要算法生成报文摘要的目的是防止发送的保温被篡改

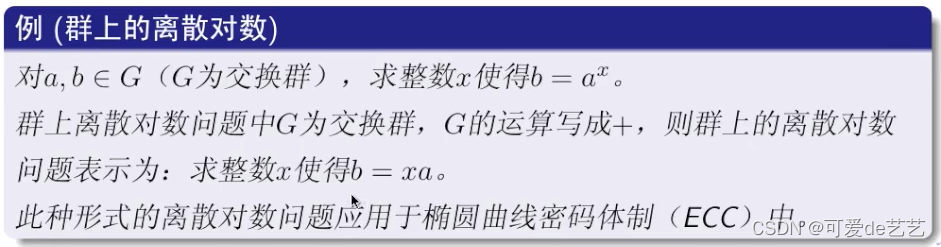

公开密钥加密算法RSA ECC DSA

只要记公钥算法是两个sa+一个cc就行了

大量明文——对称加密(加解密速度快)

MD5摘要算法输出128位散列值 sha-1安全散列算法

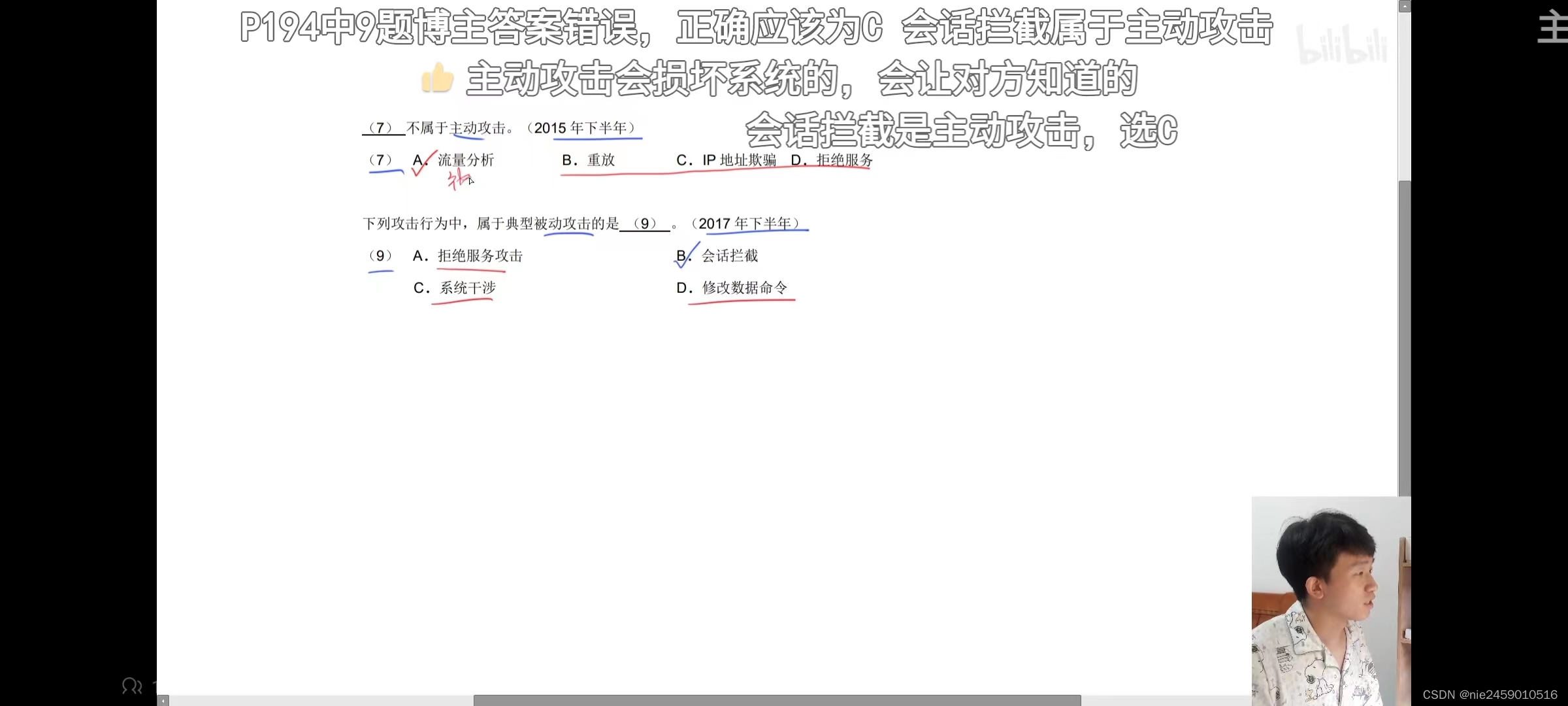

认证处理主动攻击 加密处理被动

串联是R=R1,R2

并联是R=(1-R)(1-R)…

指令寄存器就是保存指令用的啊,那么位数当然是由指令字长决定的

与就是乘法 或就是加法 逻辑与&有0就是0 逻辑或|有1就是1

逻辑同或 相同为1 不同为0 异或相反

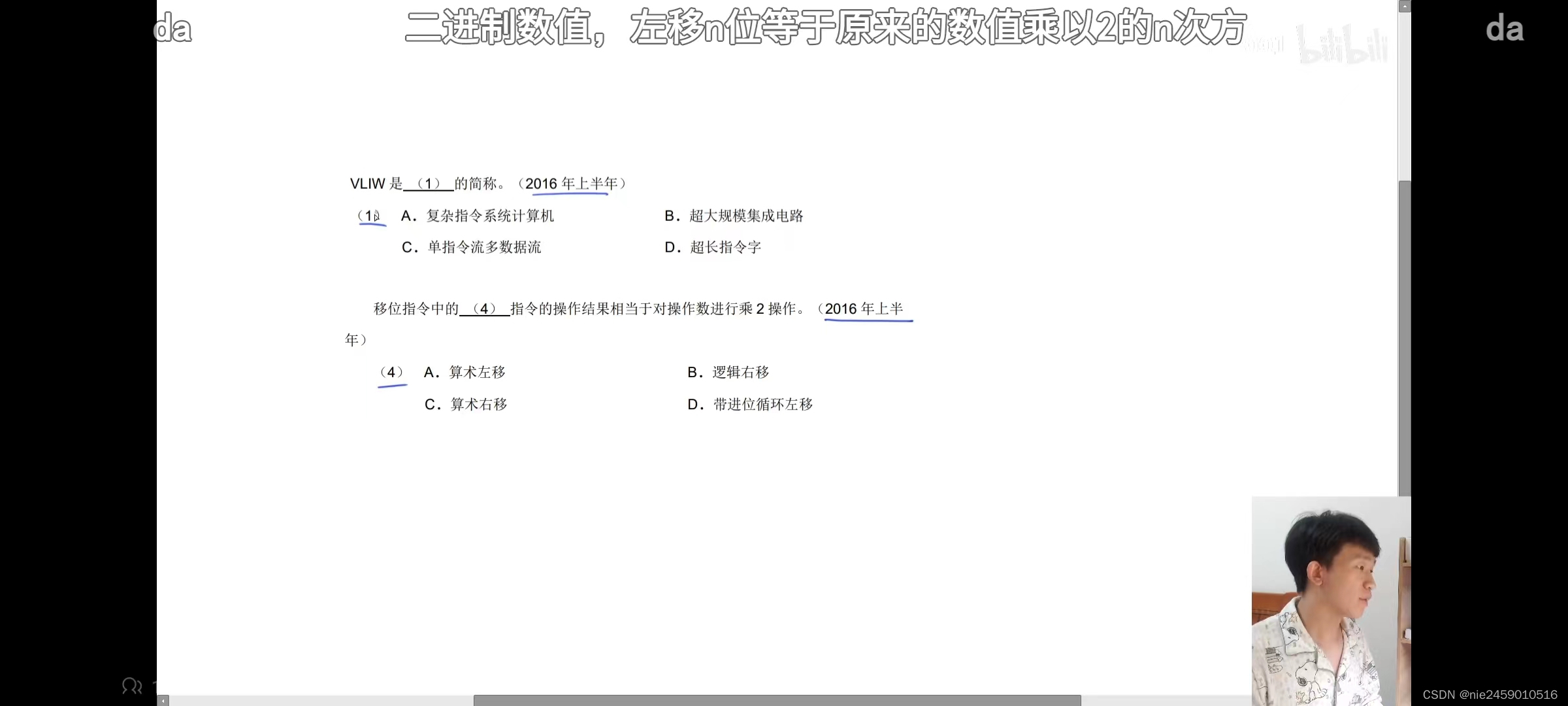

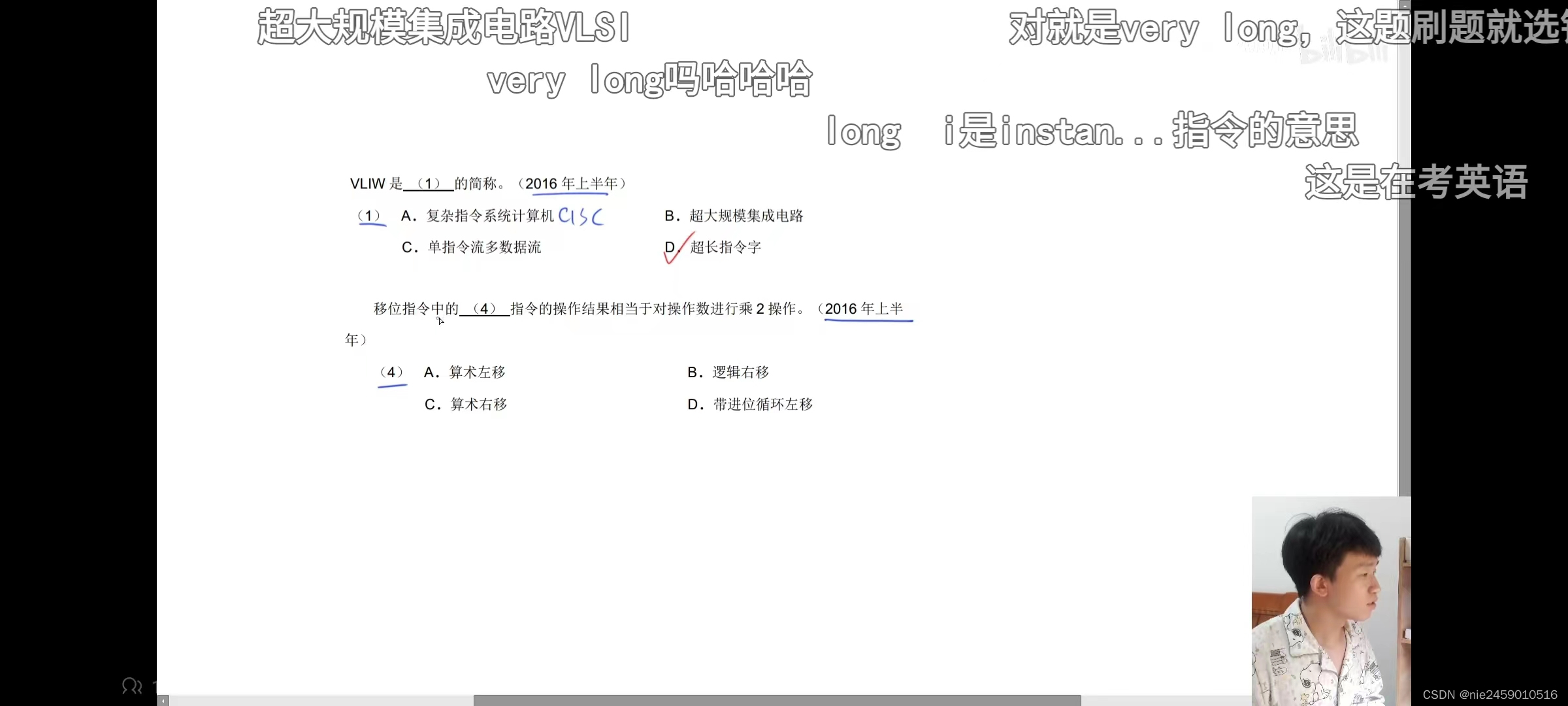

算术左移相当于二进制乘法的二次方 算术右移相当于除2

主动攻击会损坏系统的,会让对方知道的 **

![容器中的operator[]注意事项](https://img-blog.csdnimg.cn/1006e338c1e04e7ca158ae4d998d1f4c.png#pic_center)