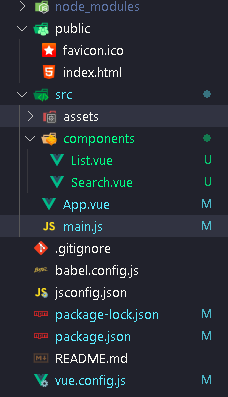

Altera_Shift Register(RAM-based)ip核

- 前言

- 1.创建mif文件,通过ROM ip核调用该mif文件

- 1.1创建mif文件

- 1.2顺序填充mif文件

- 1.3创建ROM ip核调用mif文件

- 2.计数器读取mif文件中的数据

- 2.1写一个0-15的循环计数器

- 2.2实例化ROM ip核、调用计数器模块

- 3.从mif中读取出来的数据传入shift_ram ip核

- 3.1创建shift_ram ip核

- 3.2实例化Shift_ram ip核

- 4.modelsim仿真查看shift_ram输出数据

- 4.1生成TestBench模板

- 4.2顶层文件添加激励、工程添加仿真文件

- 4.2.1顶层文件添加激励

- 4.2.2工程添加仿真文件

- 4.3modelsim仿真

前言

最近在做sobel、canny边缘检测需要使用shift_ram做3*3卷积模板,在这一块纠结过一阵子,最后还是想写篇博客沉淀一下。这篇博客就举例记录一下: mif文件输入shift_ram ip核,生成2条tap查看输出效果

1.创建mif文件,通过ROM ip核调用该mif文件

1.1创建mif文件

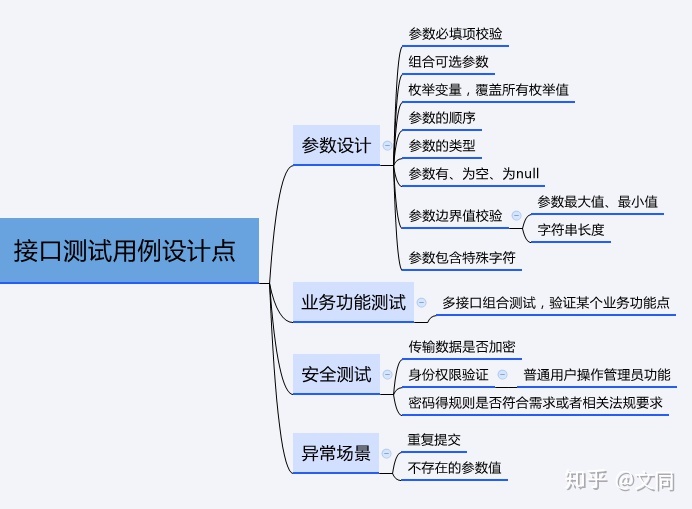

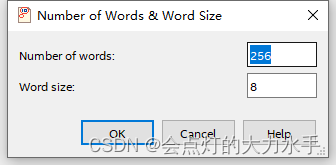

新建mif文件,保持默认的256字数和8位字长

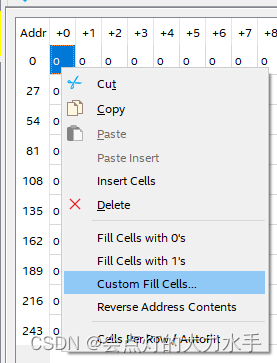

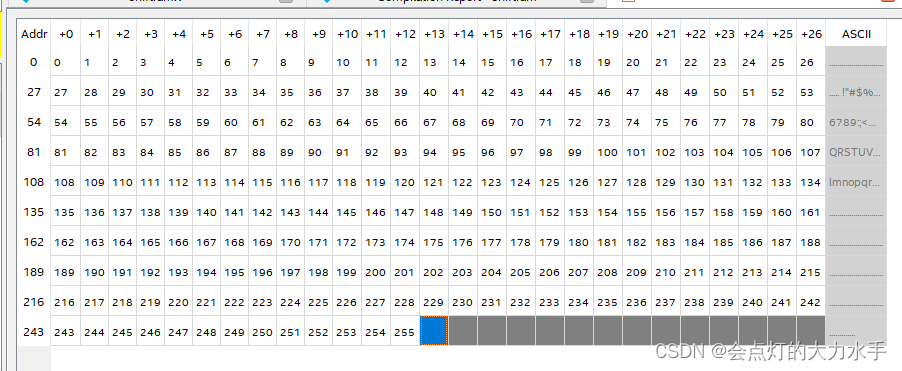

1.2顺序填充mif文件

可以使用mif生成软件,也可以按照下图所示

顺序填充mif,按照顺序填充的好处在于,modelsim仿真时,可以更方便查看结果

保存为mif文件,等待ROM ip核调用

保存为mif文件,等待ROM ip核调用

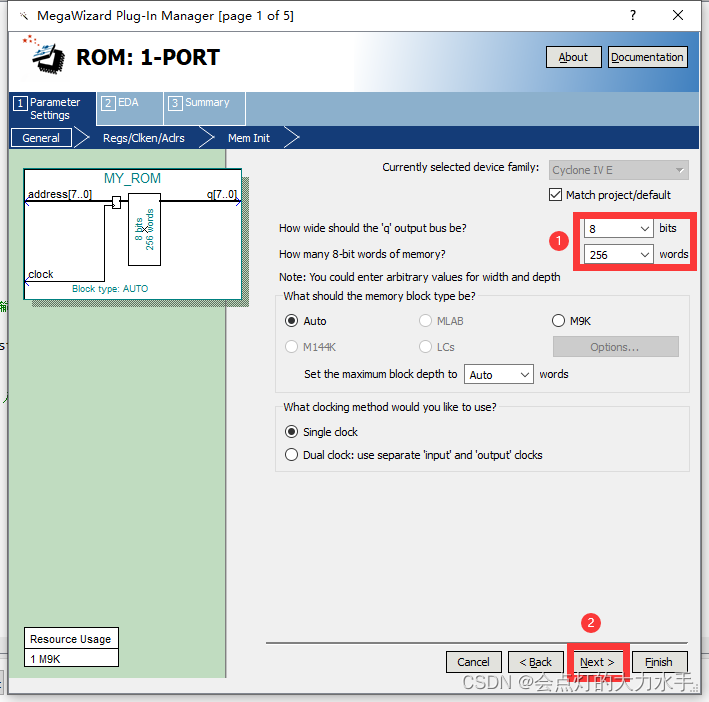

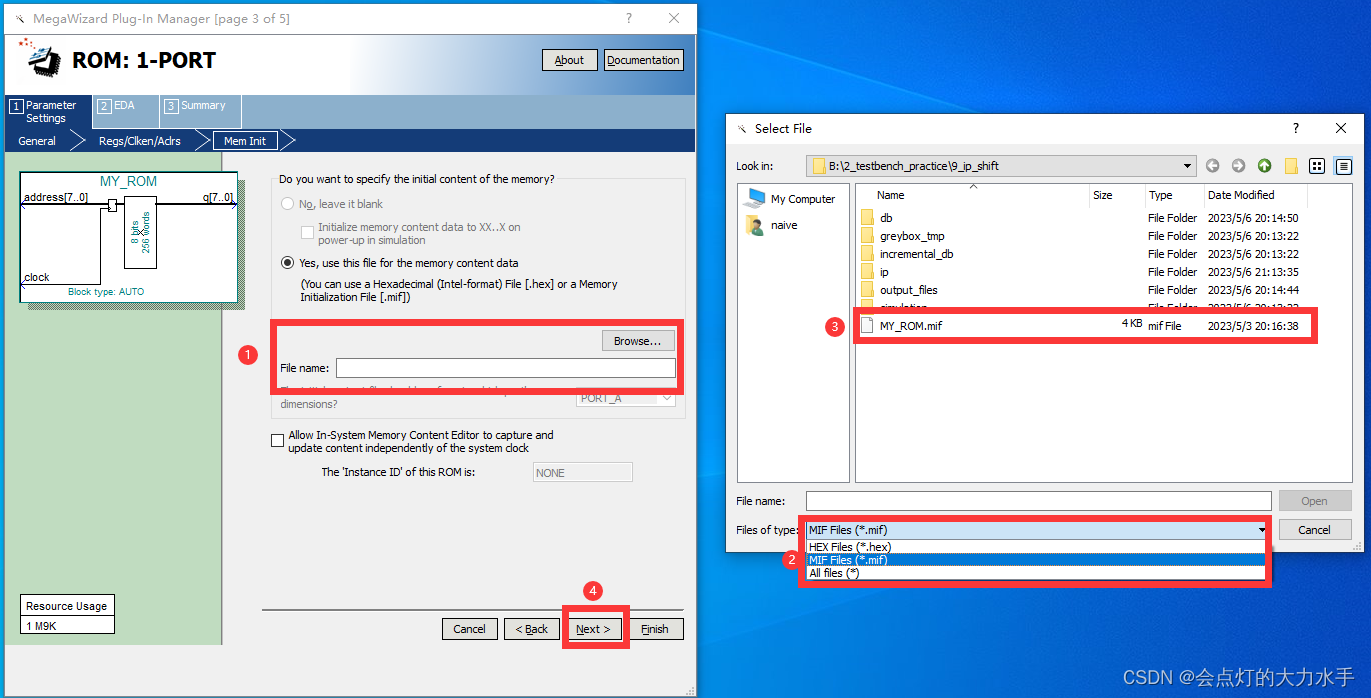

1.3创建ROM ip核调用mif文件

下图中按照mif文件的大小来配置ROM的大小

下图中按照mif文件的大小来配置ROM的大小

下图中的‘q’out port可选可不选,区别在于,勾选之后‘q’数据会被存入寄存器,由此带来一个时钟信号的延迟

2.计数器读取mif文件中的数据

2.1写一个0-15的循环计数器

这里以0-15的计数器为例,方便查看modelsim仿真数据,当然也可以配置成其他的

module counter(

input clk_in, //时钟信号

input rst_n, //复位信号

output reg [7:0] cnt, //计数值,在后续步骤中,这个cnt也可以作为ROM地址

output reg shift_en //进位信号,在后续步骤中,也可以做输出使能,

);

//0-16循环计数,计满时

always@(posedge clk_in or negedge rst_n)

begin

if(!rst_n)

begin

cnt <= 8'b0;

shift_en <= 1'b0;

end

else

begin //8'd16表示8位二进制数,大小为16

if(cnt >= 8'd16)

begin

cnt <= 8'b0; //等于16的瞬间被置为0,因此是0-15的计数器

shift_en <= 1'b1;

end

else

cnt <= cnt + 1'b1;

end

end

endmodule

2.2实例化ROM ip核、调用计数器模块

MY_ROM MY_ROM_inst (

.address ( cnt ),

.clock ( clk_in ),

.q ( in )

);

counter counter_inst(

.clk_in ( clk_in ),

.rst_n ( rst_n ),

.cnt ( cnt ), //ROM地址

.shift_en ( shift_en ) //输出使能

);

3.从mif中读取出来的数据传入shift_ram ip核

3.1创建shift_ram ip核

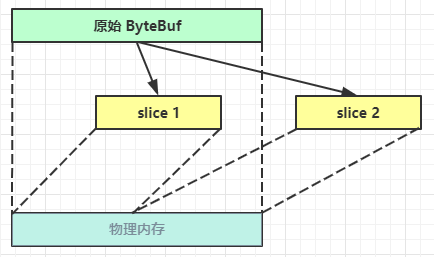

Shift_ram配置说明

ROM输出的数据是8位的,所以要输入Shift_ram的话,shift_in需要配置为8位

这里选择2条taps输出,另一条是shiftout,所以一共是3条输出

distance根据需求配置,例如,输入一张像素是100*120的图片,那么distance可以配置成100

3.2实例化Shift_ram ip核

shift_register shift_register_inst(

.clk_in ( clk_in ),

.rst_n ( rst_n ),

.shift_en ( shift_en ),

.in ( in ), //从ROM输入的数据

.shiftout0 ( shiftout0 ),

.shiftout1 ( shiftout1 ),

.shiftout2 ( shiftout2 )

);

4.modelsim仿真查看shift_ram输出数据

4.1生成TestBench模板

4.2顶层文件添加激励、工程添加仿真文件

4.2.1顶层文件添加激励

`timescale 1 ns/ 1 ns

module shiftram_vlg_tst();

// test vector input registers

reg clk_in;

reg rst_n;

// wires

wire [7:0] cnt;

wire [7:0] in;

wire shift_en;

wire [7:0] shiftout0;

wire [7:0] shiftout1;

wire [7:0] shiftout2;

// assign statements (if any)

shiftram i1 (

.clk_in(clk_in),

.cnt(cnt),

.in(in),

.rst_n(rst_n),

.shift_en(shift_en),

.shiftout0(shiftout0),

.shiftout1(shiftout1),

.shiftout2(shiftout2)

);

initial

begin

clk_in = 0;

rst_n = 0;

#100 rst_n = 1;

end

always #10 clk_in = ~clk_in;

endmodule

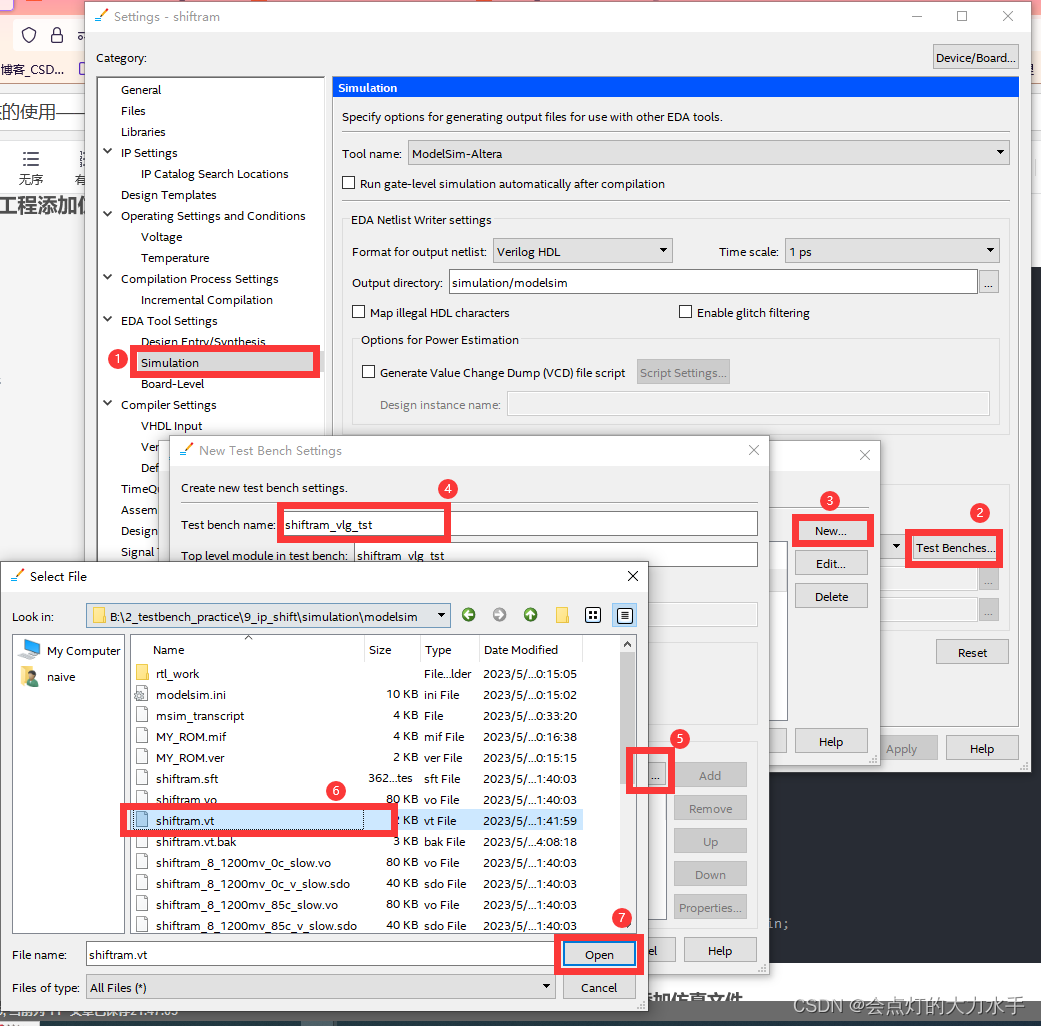

4.2.2工程添加仿真文件

shiftram_vlg_tst这个提前复制出来,后面要用

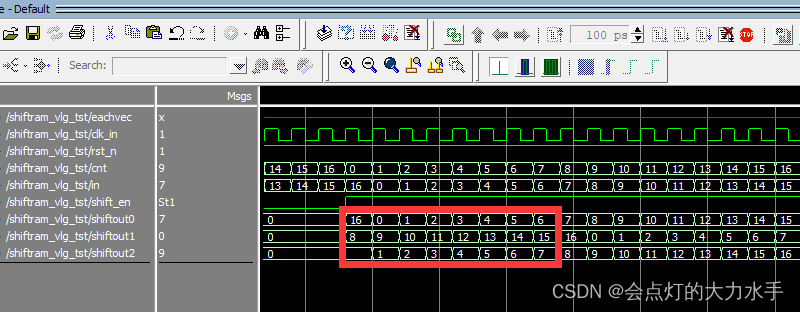

4.3modelsim仿真

工程链接点我点我点我!

![K8S管理系统项目实战[API开发]-2](https://img-blog.csdnimg.cn/27e2b8811f3645d5b5e29dcbc1715515.png)