目录

一、RAM

1.RAM特点

2.静态RAM

2.1静态RAM保存原理

2.2静态RAM基本单元电路的构成

2.3静态RAM读写操作

3.动态RAM

3.1动态RAM保存原理

3.2动态RAM基本单元电路的构成

3.3动态RAM对单元电路的读写操作

3.4动态RAM的刷新

4.静态RAM与动态RAM的比较

二、ROM

1.ROM发展

三、存储器容量扩展

1.位扩展(增加存储字长)

2.字扩展

3.字与位同时扩展

一、RAM

1.RAM特点

2.静态RAM

2.1静态RAM保存原理

静态RAM使用的是触发器进行存储数据,触发器由四根晶体管构成,属于双稳态触发器,具有源端和非端用于存储数据,一方为0另一方为1,一方为1,另一方为0。

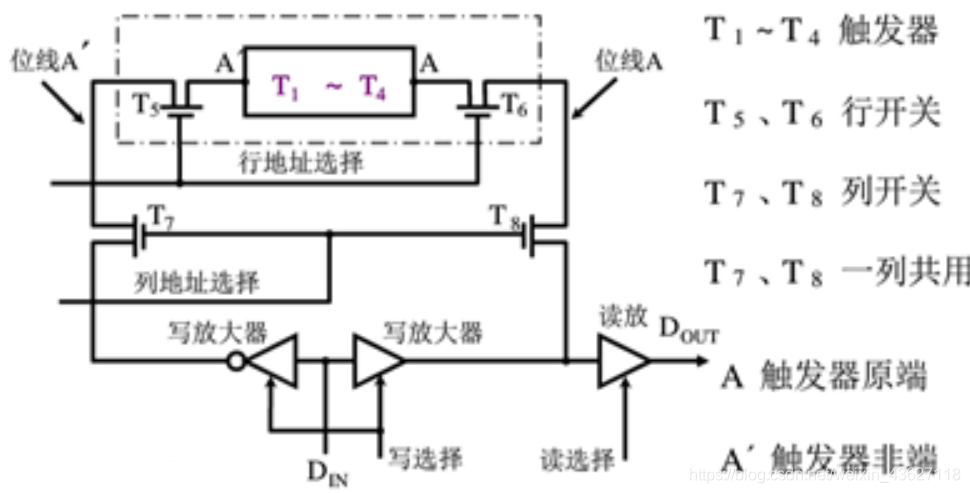

2.2静态RAM基本单元电路的构成

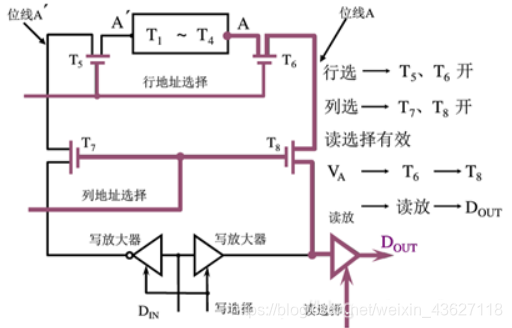

2.3静态RAM读写操作

(1)读操作

读数据时,虽然T5开,T7开,但是非端数据到写放大器就终止了。

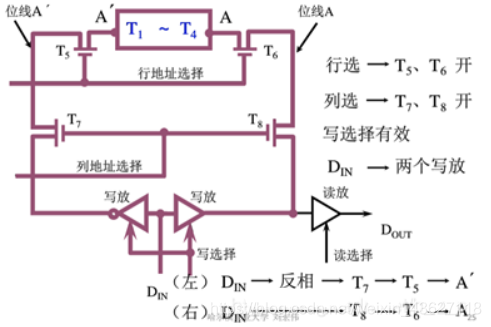

(2)写操作

写数据时,左边的写放大器把右边的写放大器的值取非后进行输出,保证A和非A端的值相反。

3.动态RAM

3.1动态RAM保存原理

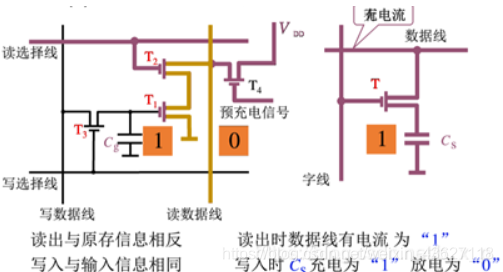

动态RAM使用电容,电容中保存了电荷为1,电容没有被充电为0。

3.2动态RAM基本单元电路的构成

3.3动态RAM对单元电路的读写操作

(1)左侧电路读写操作

读操作: T4为预充电信号,如果预充电信号有效,T4会被打开,Vdd通过T4对读数据线进行充电,使得读数据线成为高电平,如果是进行读操作,则读选择信号有效,T2打开,如果此时CG中保存的数据是0,也就是CG没有充电,则T1不会导通,则读数据线就会保持高电平,所以,如果保存的数据是0,则在读数据时候,读出的数据是1。如果CG电容中保存的数据是1,T1导通,此时读数据线上的电平通过T2,T1线路进行放电,读数据线低电平,读出的数据为0。所以电容读出的信息和原存的信号是相反的。

写操作: 写入和输入信息相同。如果是写操作,写选择线有效,T3导通 写数据线会通过T3向CG充电,或者CG通过T3进行放电,如果写入的数据是1高电平,写数据线会通过T3向CG充电,CG写入1.如果写入是0,则CG通过T3进行放电,CG放电为0。

(2)右侧电路读写操作

读操作: 如果相应的行被选中,字线连接的T被打开,电容就会通过T进行充电或者放电,如果CG中有电位1,此时放电,则数据线有电流,如果CS中没有充电,则数据线无电流,通过数据数据线有无电流判断CS中保存的是1还是0。

写操作: 写入时,写入1,数据线有电流,进行充电为1。写入0,数据线无电流,放电为0。

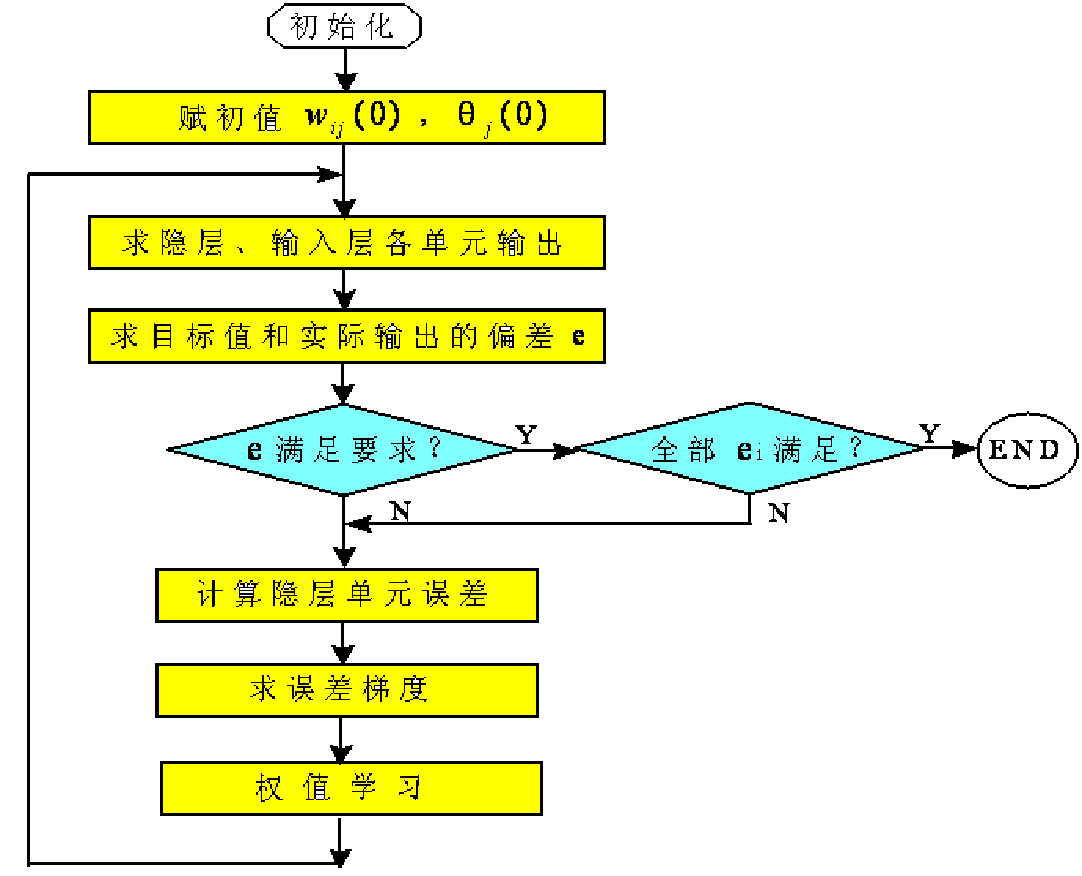

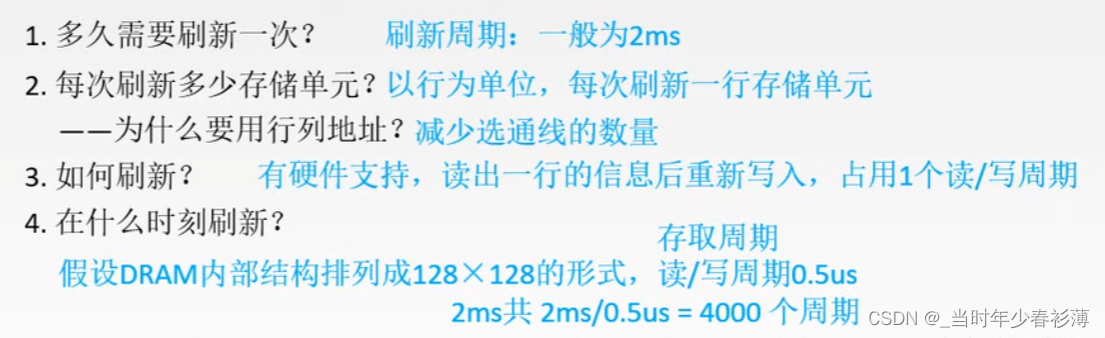

3.4动态RAM的刷新

(1)为什么要刷新

由于动态RAM使用电容存储信息,电容容易漏电,经过一段时间,电容漏电,会导致数据有1变为0,。动态RAM刷新只和行地址有关,和列地址无关,每次刷新的是一行中的所有基本电容电路。给出行地址,某一行被全部选中,这个行上所有电容中的信息都会被送到读电路,如果在读数据线和写数据线之间增加一个刷新放大器(每一列都加),就会完成对一行数据的刷新。

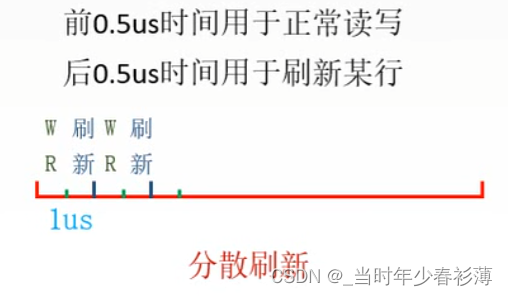

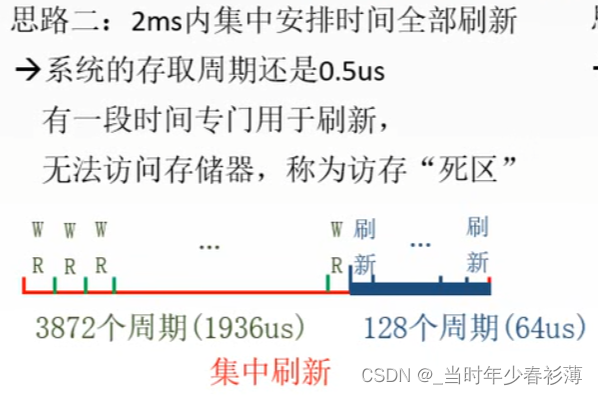

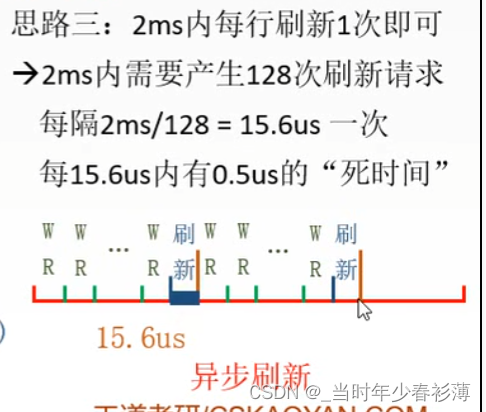

(2)刷新方法

分散刷新虽然没有死区,但是刷新过于频繁,并且延长了CPU的读写周期。

集中刷新每隔2ms对128进行全部刷新,存取周期为0.5us,所以刷新每行也需要0.5us,2ms内,刷新需要64us。在这段死区内,CPU无法对动态RAM进行读写操作。

异步刷新若将刷新安排在指令译码阶段,就不会出现死区

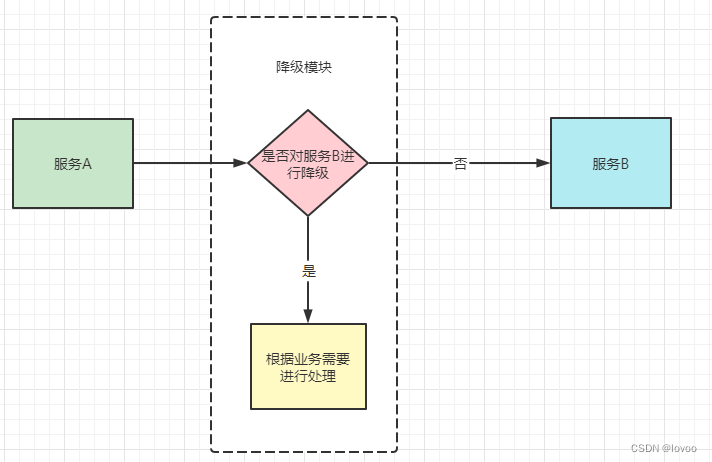

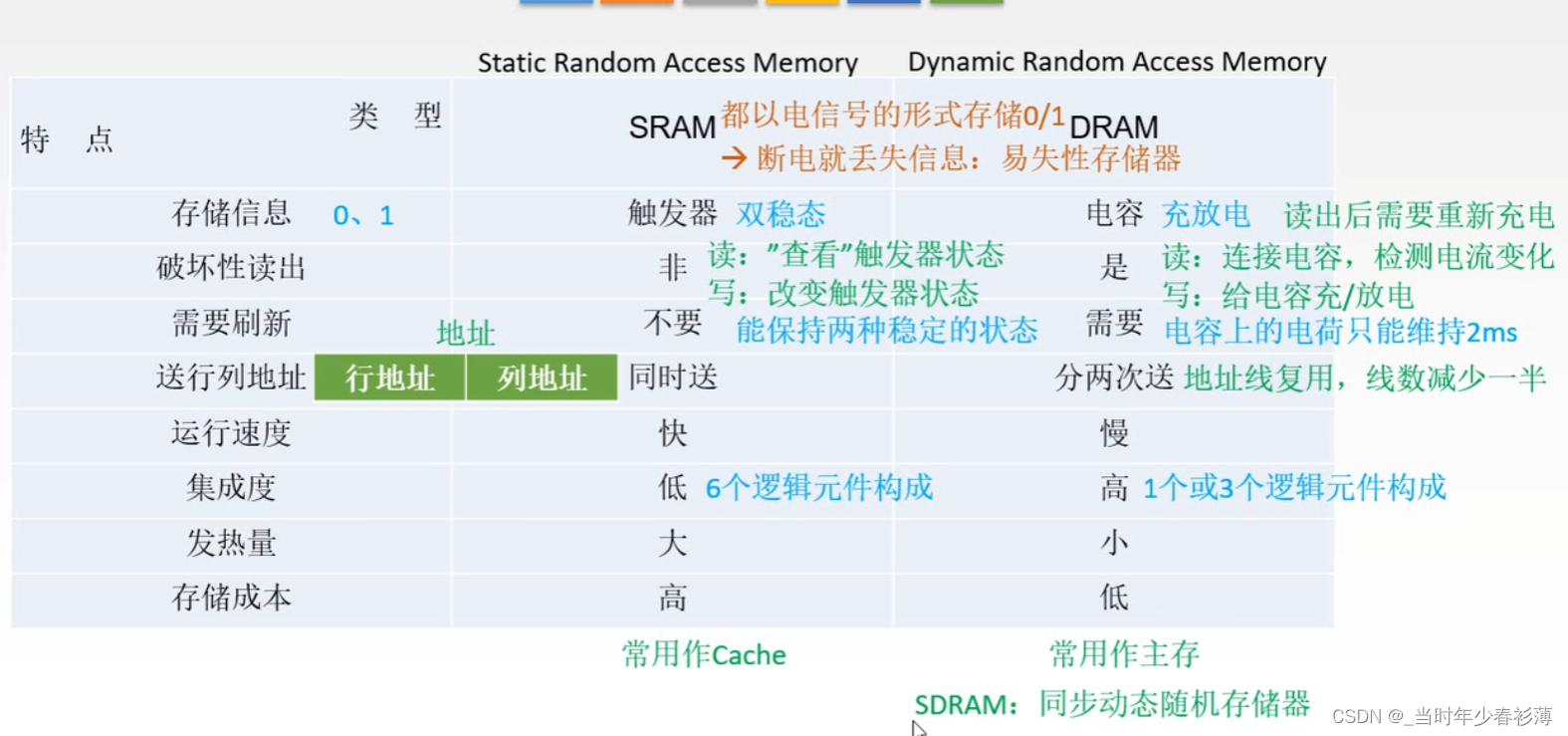

4.静态RAM与动态RAM的比较

DRAM用于做主存,SRAM用于主存和CPU之间的缓存。这样就可以降低成本同时加快访问速度。

二、ROM

1.ROM发展

三、存储器容量扩展

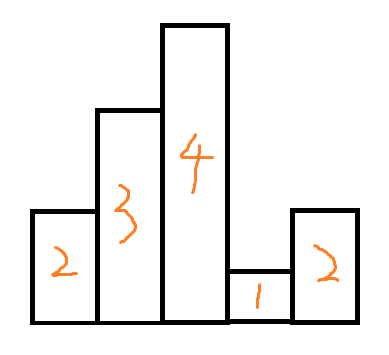

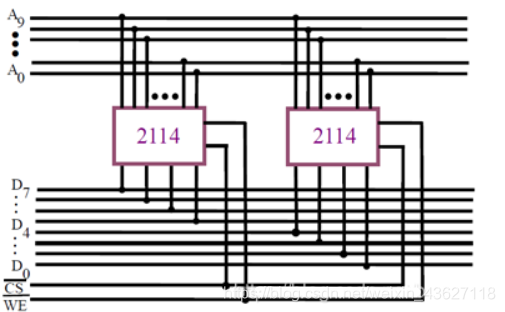

1.位扩展(增加存储字长)

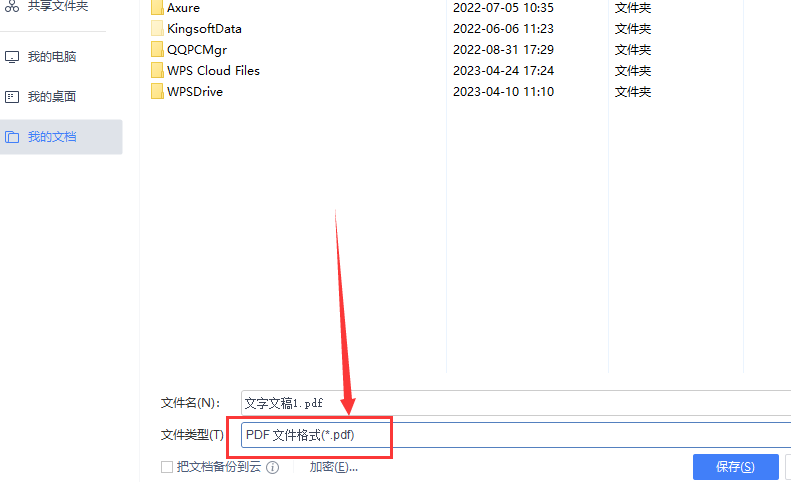

上图为用两个 1k * 4 位存储芯片组成一个1K * 8位的存储芯片。在读取数据的时候,通过cs片选线同时选中两个芯片,将每个芯片中的四位组成8位传送到数据线上。

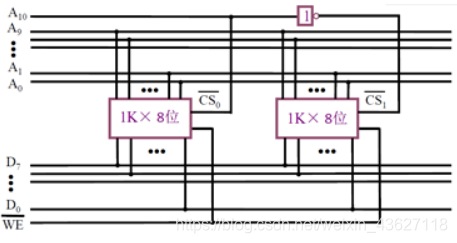

2.字扩展

图中是将连个1k * 8的存储芯片组成一个2k * 8的存储芯片。共需要11根地址线 ,8根数据线,其中10根地址线选中具体的一个地址,第十根地址线用作片选线,当第十根为0时候,使用芯片1,当第十根为1时候,使用芯片2。

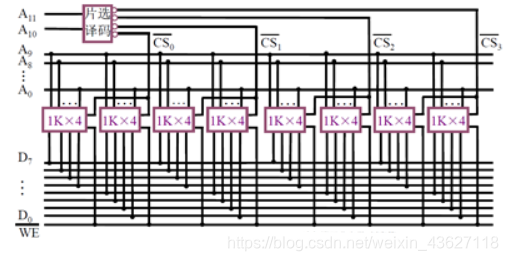

3.字与位同时扩展

用8片 1K * 4位的芯片组成4K * 8位的芯片。其中有12根地址线,8根数据线,其中两根地址线作为片选线,一个片选地址选中两片芯片。