1.1 GS232 开源版本简介

GS232 开源版本不包含 DSP、浮点部件等。

TLB 大小为 32 项。

指令和数据 Cache 为 4 路组相连,每路大小为 4KB,Cache 行大小为 32 bytes。

对外接口为 32 位 AXI 接口。

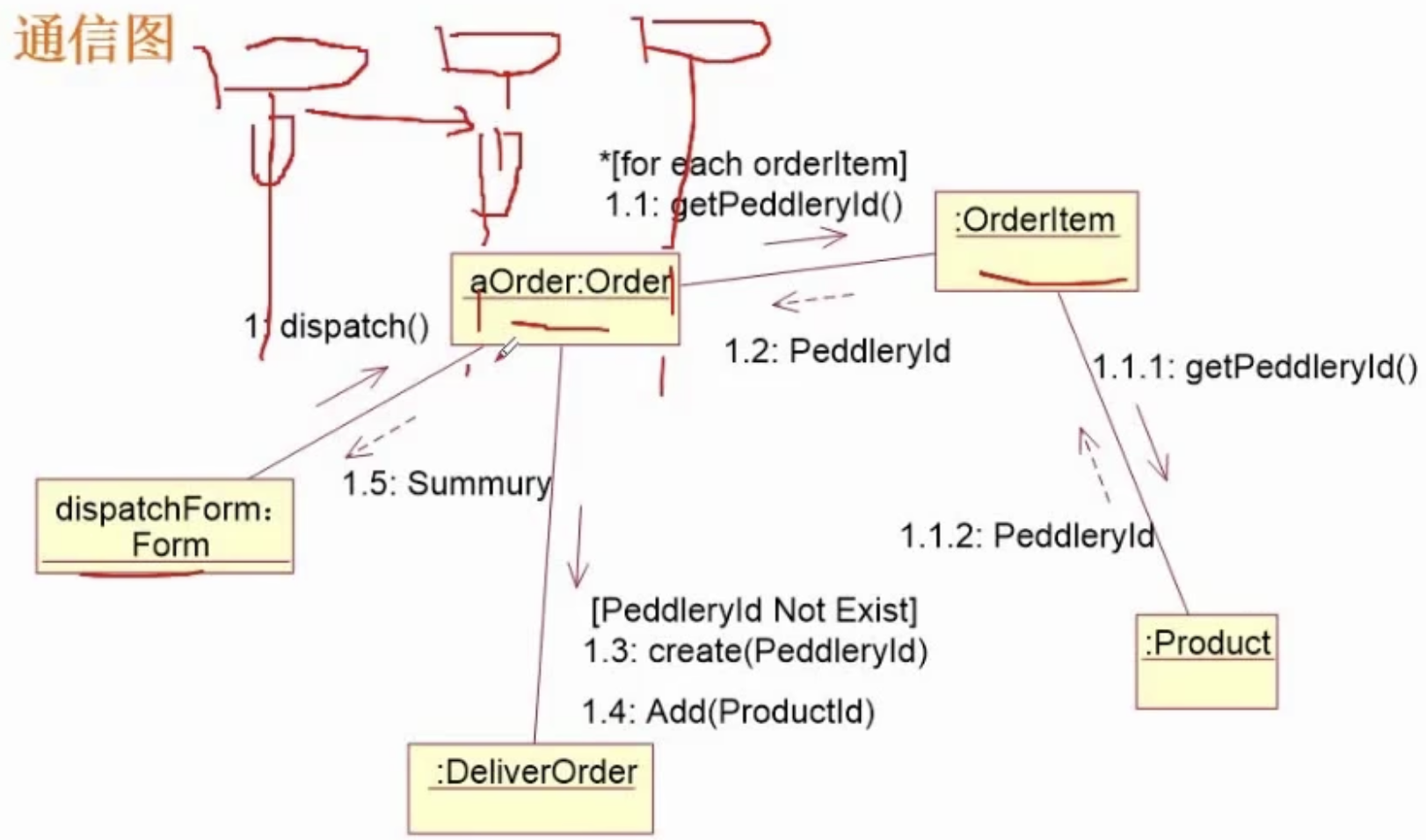

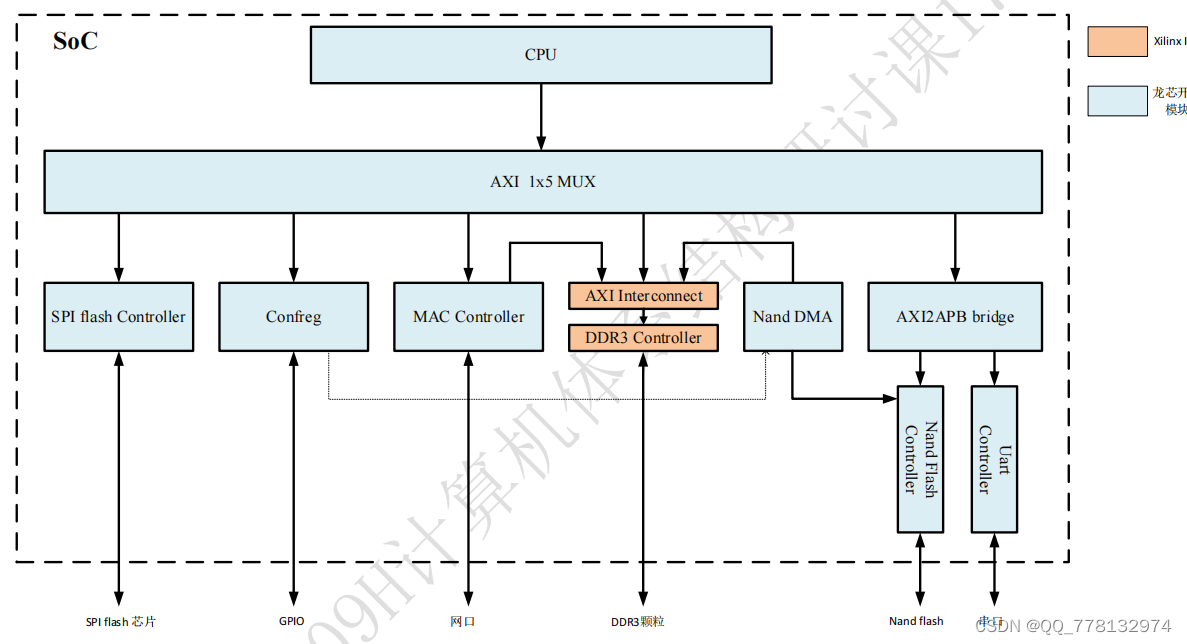

1.2 1,soc_up结构

SoC_up 如上图所示。开源 GS232 对外有一个 AXI 接口,连接到 AXI 互联网络上与外设相连。SoC_up 对外连接的设备共有 6 个:SPI flash、GPIO(数码管、LED 灯、开关灯)、网口、DDR3 颗粒、Nand flash和串口。这些外设在教学实验板上均已集成。

2,各模块的控制器说明

NAND DMA 控制器

其一端通过 64 位 AXI 接口接到 DDR3 内存上,一端通过 APB 接口接到 APB 设备上(可认为接到 NAND 控制器 上)。 该 DMA 只用于 nand flash 与内存交换数据。 该 DMA 的配置寄存器 ORDER_ADDR_IN 位于 CONFREG 模块。

NAND FLASH 控制器

通过 APB 接口接在 APB 桥上。

该 NAND FLASH 控制器不支持上电从 flash 启动和校验纠错。

FPGA 板上 NAND FLASH 颗粒 K9F1G08U0C-PCB0 的 main 区容量为:1K blocks * 64 pages/block * 2K Bytes/page =128M bytes。也就是共有 64k 页,一页为 2k bytes。每页的 spare 区为 64bytes。

CONFREG 模块

包含 8 个 32 位内存映射读写寄存器和一个 d