文章目录

- 相关概念介绍

- IO引脚的三态输出之高阻态---将逻辑门与系统其他部分隔离,电平外部控制

- IO引脚输出模型 推挽电路 与 开漏电路---单独开漏无高电平驱动能力

- 原理介绍

- 什么是上下拉电阻?---把IO口用电阻拉到正压VCC(上拉) 或 接地GND(下拉)

- 使用场景一:将不确定信号钳位高电平(上拉) 或 低电平(下拉)

- 使用场景二:开漏输出加上拉电阻实现 线与逻辑,如I2C总线用法

- 使用场景三:开漏输出加上拉电阻 提高电压准位

- 使用场景四:加大引脚驱动能力,上拉加强拉电流能力,下拉加强吸电流能力

- 参考

在嵌入式领域 上下拉电阻应用非常广泛。近期项目有用到,这里总结一下相关使用。

相关概念介绍

IO引脚的三态输出之高阻态—将逻辑门与系统其他部分隔离,电平外部控制

三态门/三态输出电路 三种状态为:高电平,低电平,高阻态;

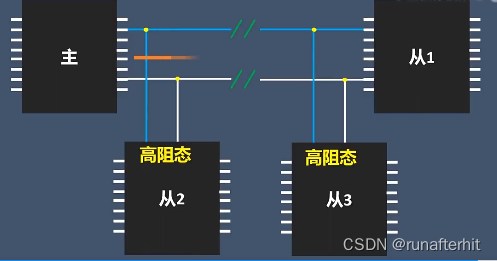

计算机中的记忆元件由触发器组成,而触发器只有01两个状态。如果要在一条信号线上连接多个触发器,而每个触发器可以根据需要与信号线连通或断开,当连通时可以传送0或1,断开时对信号线上的信息不产生影响,此状态为高阻态。

高阻态从端口看进去,对GND或者VCC的电阻都很大,什么也不输出了,引脚上的电平可由其它电路来控制,外面任何弱驱动都能改变该点的电位。

使用场景举例:当一个总线上 一个主设备和一个从设备通信的时候,其他设备都处于高阻态,不影响正在通信设备。

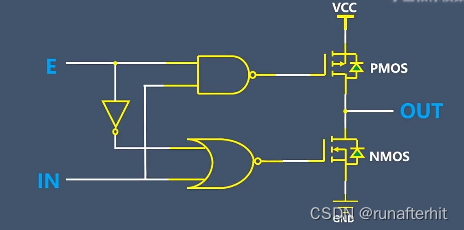

三态原理举例:已下图三态输出缓冲器:IN为输入,OUT为输出,E是使能。当E=H,IN=H,下面Nmos关闭,上面Pmos导通,Out=H。当输入E=H,IN=L,下面Nmos打开,上面Pmos关闭,Out=L。当E=L,两个mos都关闭,输出为高阻Out=Z。

IO引脚输出模型 推挽电路 与 开漏电路—单独开漏无高电平驱动能力

首先讲IO输出的电流描述,输入端有电流流进称为吸电流(被动);输出端有电流流出称为拉电流(主动);输出端有电流流入称为灌电流(被动)。灌电流能力与拉电流能力也称为芯片引脚的驱动能力,对于任何给定的芯片,引脚的驱动能力都是有限的。下面介绍两种输出模型:

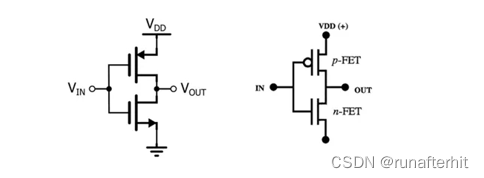

1)推挽输出(Push-Pull Output):由两个MOS或者三极管受到互补控制信号的控制,两个管子始终处在一个导通另一个截止的状态。推挽输出既可以输出低电平(只下方Mos导通),也可以输出高电平(只上方Mos导通)。推挽输出可以吸电流也可以灌电流,相对于开漏输出电平取决于IC电源是固定的,一条总线上输出期间只能有一个推挽。

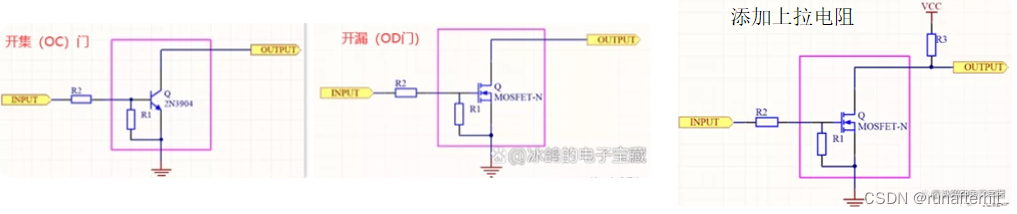

2)开漏输出(open drain):开漏OD门是针对MOS管来说,针对三极管来说叫开集OC门。单独的开漏输出只能输出低电平(导通Mos),不导通时为高阻态。高电平需要上拉电阻才能输出,通过控制连接VCC大小设置电平,因此在需要进行指定高电平时适合使用开漏输出(推挽固定IC电源)。开漏还能实现”线与“逻辑(I2C等接口总线应用中),利用外电路提高驱动能力,利用上拉电阻提供高电平,没有上拉电阻只能输出低电平。

原理介绍

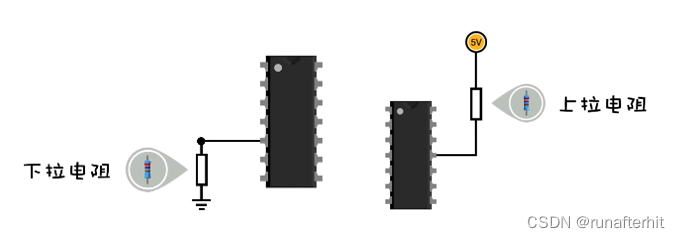

什么是上下拉电阻?—把IO口用电阻拉到正压VCC(上拉) 或 接地GND(下拉)

上拉/下拉电阻设计时一般不能影响正常的信号电平,常见上拉/下拉电阻阻值是1k、4k7或10k。典型上拉电阻如10K左右,太大了抗干扰能力弱,太小了,会导致电流过大。

使用场景一:将不确定信号钳位高电平(上拉) 或 低电平(下拉)

单片机刚上电的时候电平是不定的,初始状态基本默认都为输入,切换到输出引脚有一个过程。输入端如果是高阻状态,或高阻抗输入端处于悬空状态,此时需要加上拉或下拉电阻,以免受到随机电平的影响(作为输入读取到的状态一直在变化)进而影响电路工作。同时悬空就比较容易接收外界的电磁干扰,为了防止静电造成损坏,不用的引脚不能悬空,一般接上拉电阻降低输入阻抗,提供泄荷通路。

使用场景二:开漏输出加上拉电阻实现 线与逻辑,如I2C总线用法

I2C总线协议在两条通信线上使用了上拉电阻。当设备处于非激活状态,它们“释放”掉通信线并使它们的输出端呈现高阻态,这样使它们的高低电平不影响其他电路。当总线上所有的设备都“释放”掉通信线时,对输出目标电路的唯一影响就是上拉电阻将输出端的电平拉高。当一个设备需要通信时,这个输出端脱离高阻态,并使得通信线的输出端电平降低。

使用场景三:开漏输出加上拉电阻 提高电压准位

当TTL电路驱动CMOS电路时,如果TTL电路输出的高电平低于CMOS电路的最低高电平,这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值;

使用场景四:加大引脚驱动能力,上拉加强拉电流能力,下拉加强吸电流能力

单片机输出高电平驱动力有限,由于后续电路的影响是达不到VCC,可通过上拉电阻可以提高拉电流驱动能力。下拉电阻情况类似,让单片机引脚输出低电平,结果由于后续电路影响输出的低电平达不到GND,所以接个下拉电阻。

参考

什么是数字芯片的高阻态:https://www.bilibili.com/video/BV1UG41187YV/

上拉电阻的通俗解释,你真正知道吗?:https://www.bilibili.com/video/BV1W34y1579U/

下拉电阻的通俗解释,你真正知道吗?:https://www.bilibili.com/video/BV1ZU4y1Q7eo/