目录

概述:

组合逻辑电路:——电路无记忆功能

组合逻辑电路的设计方法:

传统的设计方法:采用标准组件进行设计

组合逻辑电路的设计方法:

两种设计方法的比较:

概述:

数字电路按其完成逻辑功能的不同特点,划分为组合逻辑电路和时序逻辑电路两大类。

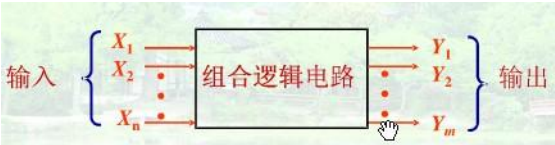

组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关

而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

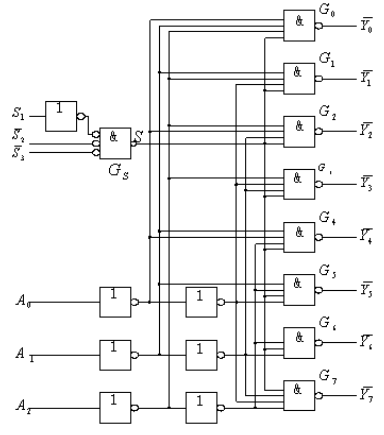

如下图的3-8译码器,Y1到Y8的输出值只与A1、A2、A3和片选信号S1、S2、S3的当前输入值有关,而与A1、A2、A3、S1、S2和S3以前任一时刻的任意输入状态无关,因此是一个典型的组合逻辑电路,而并非时序逻辑电路

组合逻辑电路:——电路无记忆功能

从逻辑上讲,组合电路在仸一时刻的输出状态仅由该时刻的信号决定,而与电路原来的状态无关。

从结构上讲,组合电路都是单纯由逻辑门组成,且输出不存在反馈路径。(不含存储单元)

常用的组合逻辑电路:简单门电路、选择器、译码器、三态门等

组合逻辑电路的设计方法:

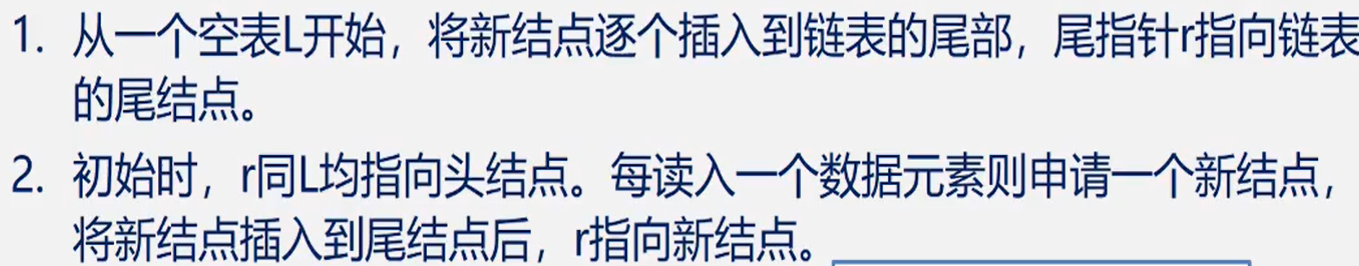

传统的设计方法:采用标准组件进行设计

(1)逻辑问题的描述。将设计问题转化为一个逻辑问题

(2)逻辑函数简化。将第一步的函数化简,求得描述设计 问题的最简表达式

(3)逻辑函数转换。根据使用的门电路类型,将表达式变 换为所需形式

(4)画逻辑图,并考虑实际工程问题。

组合逻辑电路的设计方法:

使用可编程逻辑器件,用硬件语言描述的EDA设计方法

(1)逻辑问题的描述。将设计问题转化为一个逻辑问题

(2)根据逻辑问题,用硬件描述语言进行描述

(3)对描述进行综合,仿真测试

(4)生成最终网表,下载到芯片

两种设计方法的比较:

![[Android]图片加载库Glide](https://img-blog.csdnimg.cn/dacffe54bd204edc8f5a27bb905a3300.png)