本人做过FPGA设计的项目,后面想转 IC 设计方向。现在从 DC 工具的使用开始学起,DC 是新思科技的EDA软件,具体的安装见下面的文章:

Synopsys EDA Tools 安装问题记录![]() https://blog.csdn.net/qq_43045275/article/details/127630241学习的过程就是啃书+看视频+看帖子。随我的学习进度同步更新~~~~

https://blog.csdn.net/qq_43045275/article/details/127630241学习的过程就是啃书+看视频+看帖子。随我的学习进度同步更新~~~~

本篇文章就记录一下,DC的使用和配置。

目录

知识储备

实际操作

DC setup

1、.synopsys_dc.setup 配置

2、当前用户的目录

3、工程路径下添加 .synopsys_dc.setup

启动 DC

1、输入命令

2、读取设计文件

3、link

其他

list_libs

report_lib <库名称>

-help

man

打印环境变量

list_designs

current_design

参考说明

知识储备

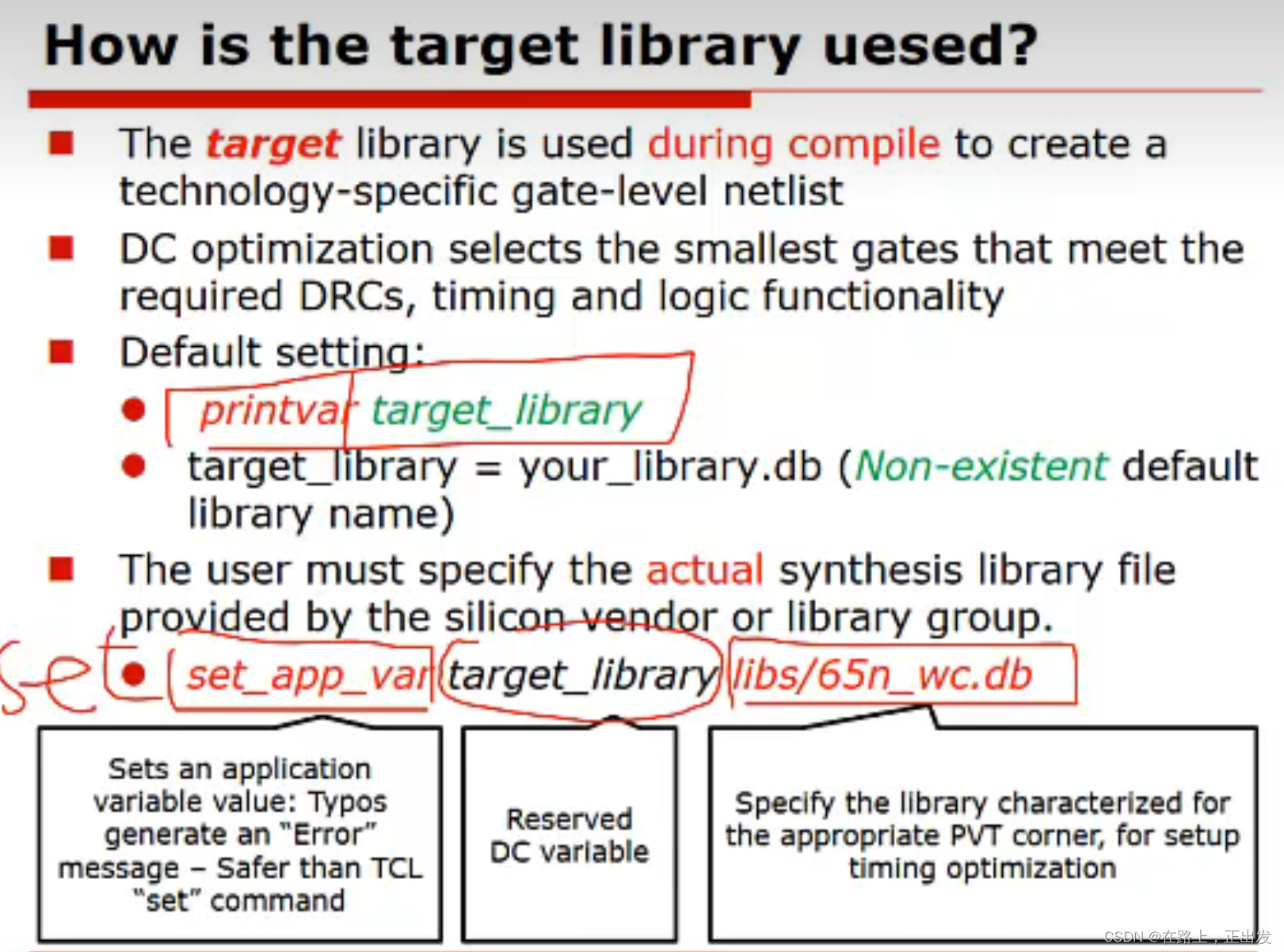

target library 是最基本的一些门、触发器等基本器件的工艺信息。

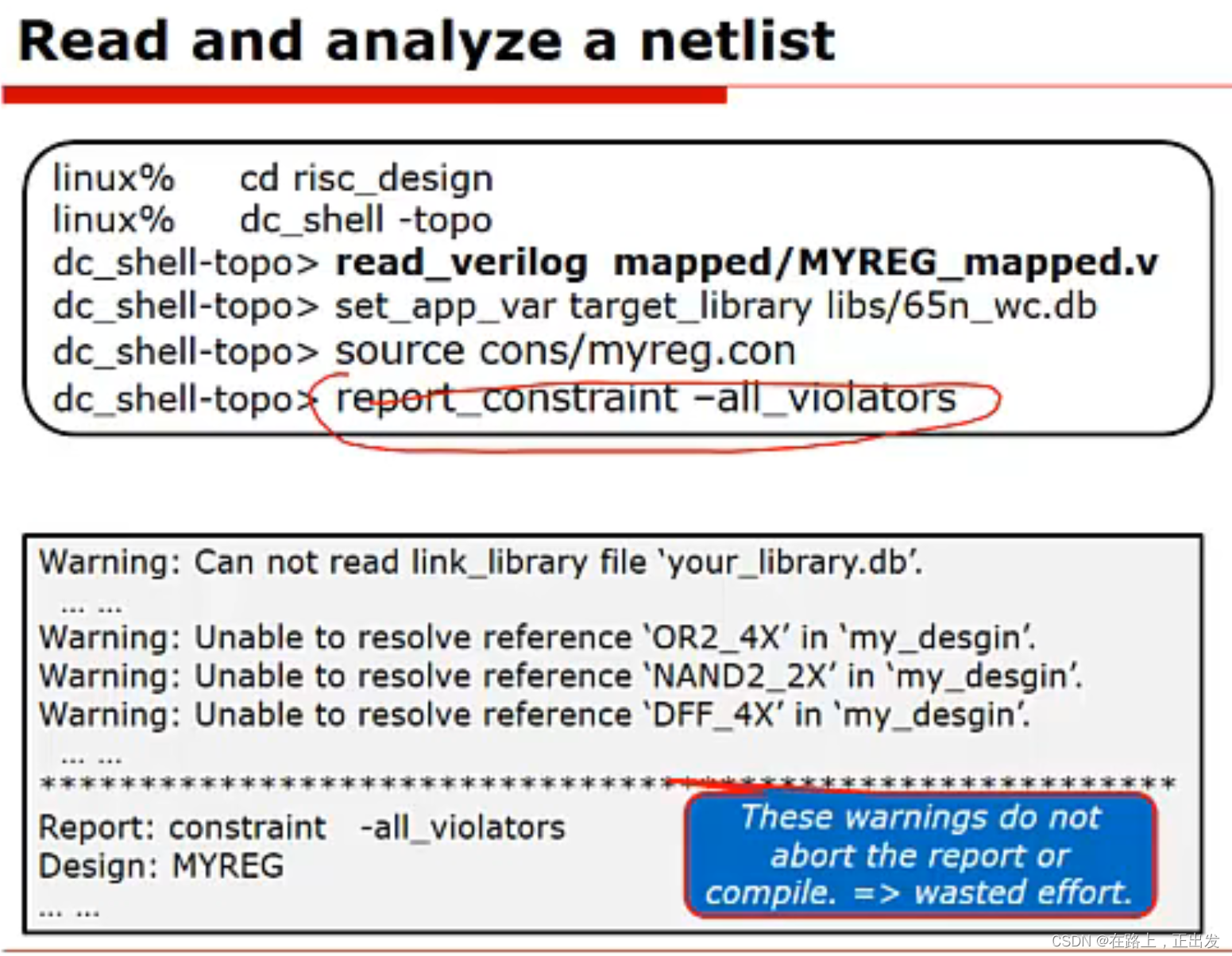

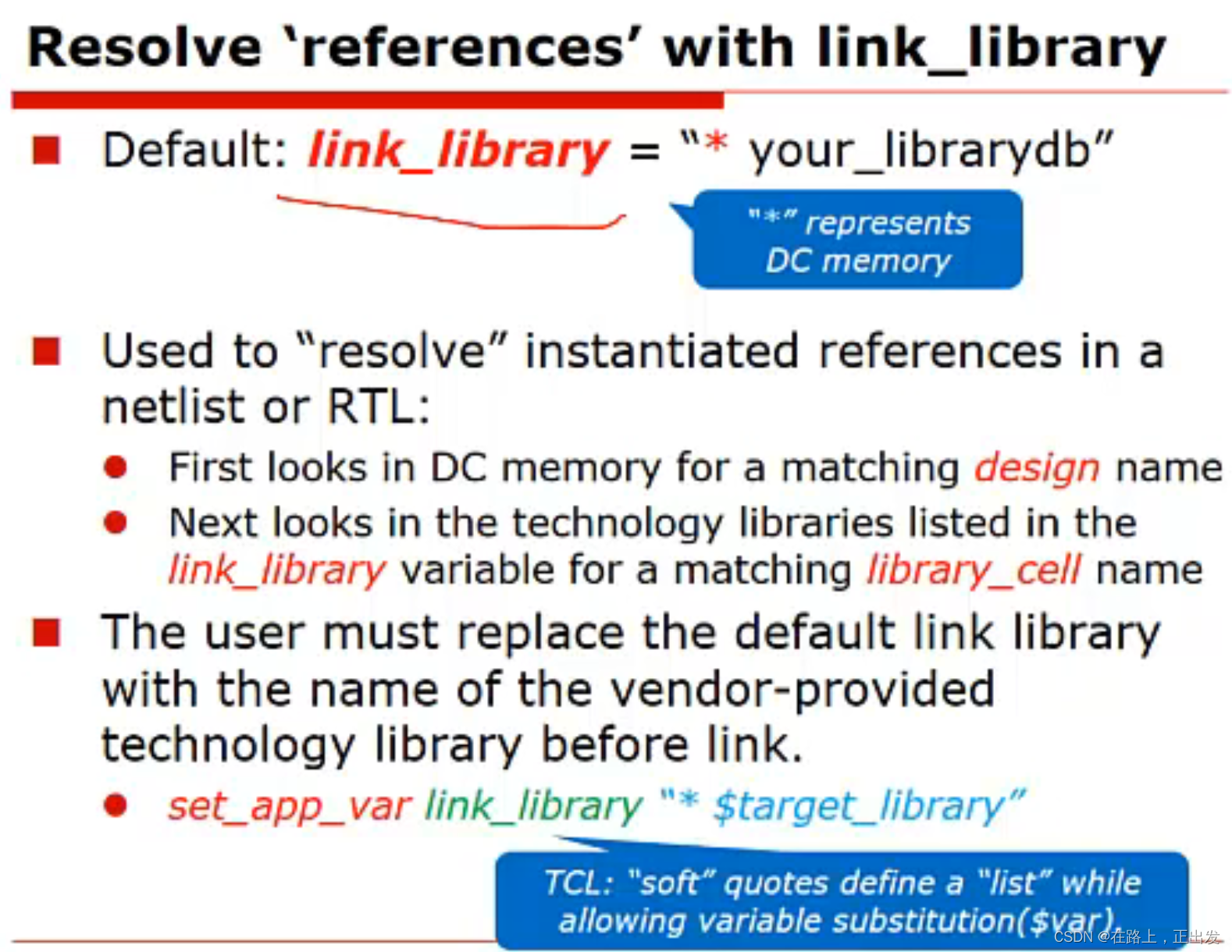

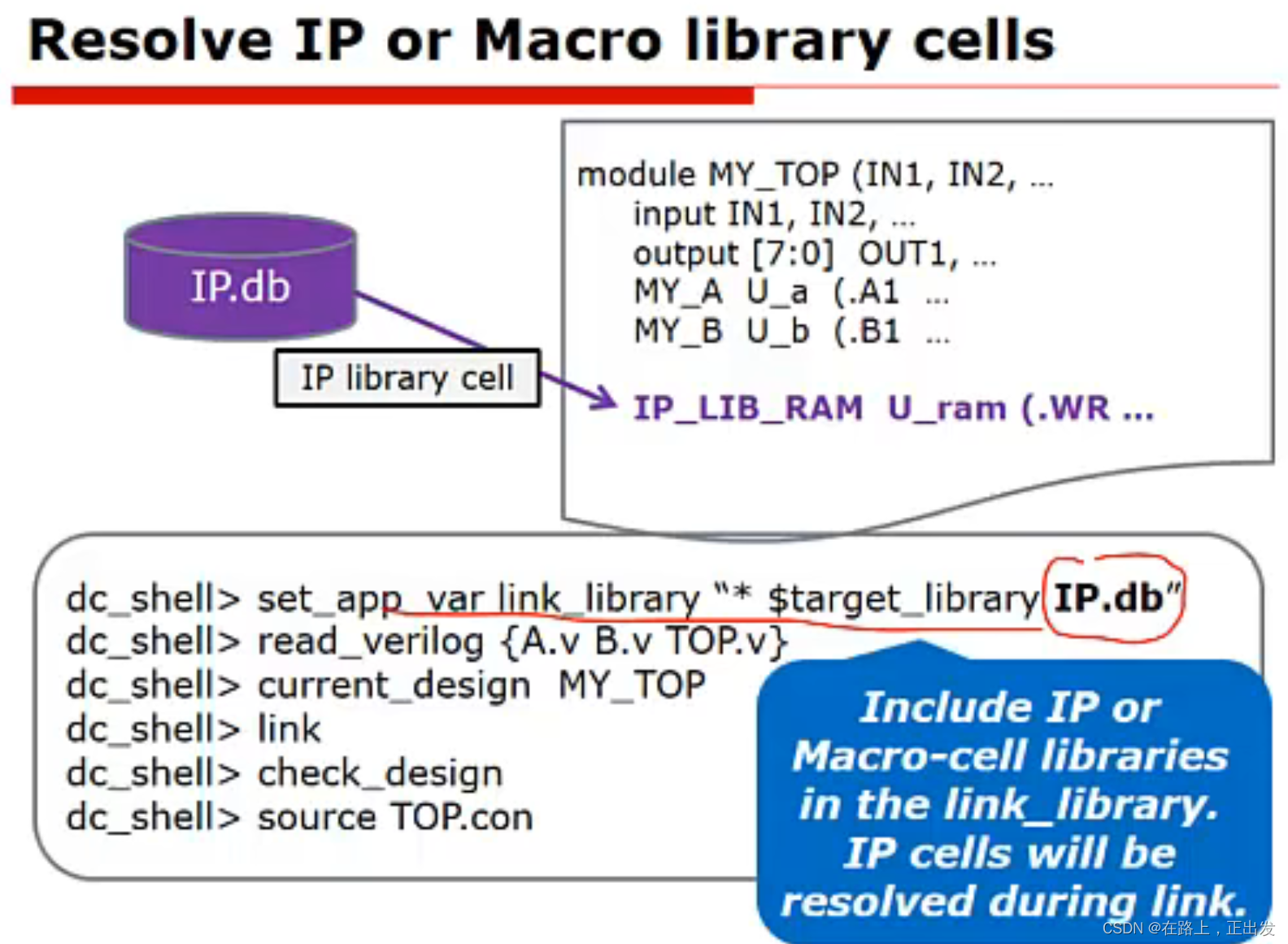

link library 包括一些 第三方 IP对应的db格式文件。

文件权限 3 > 2 >1

实际操作

DC setup

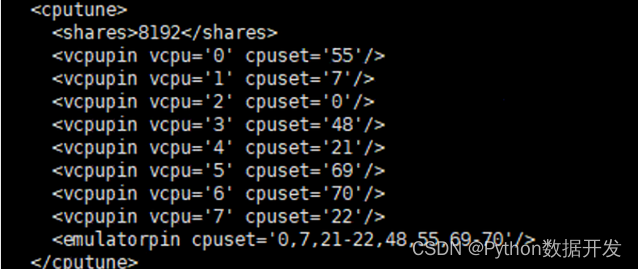

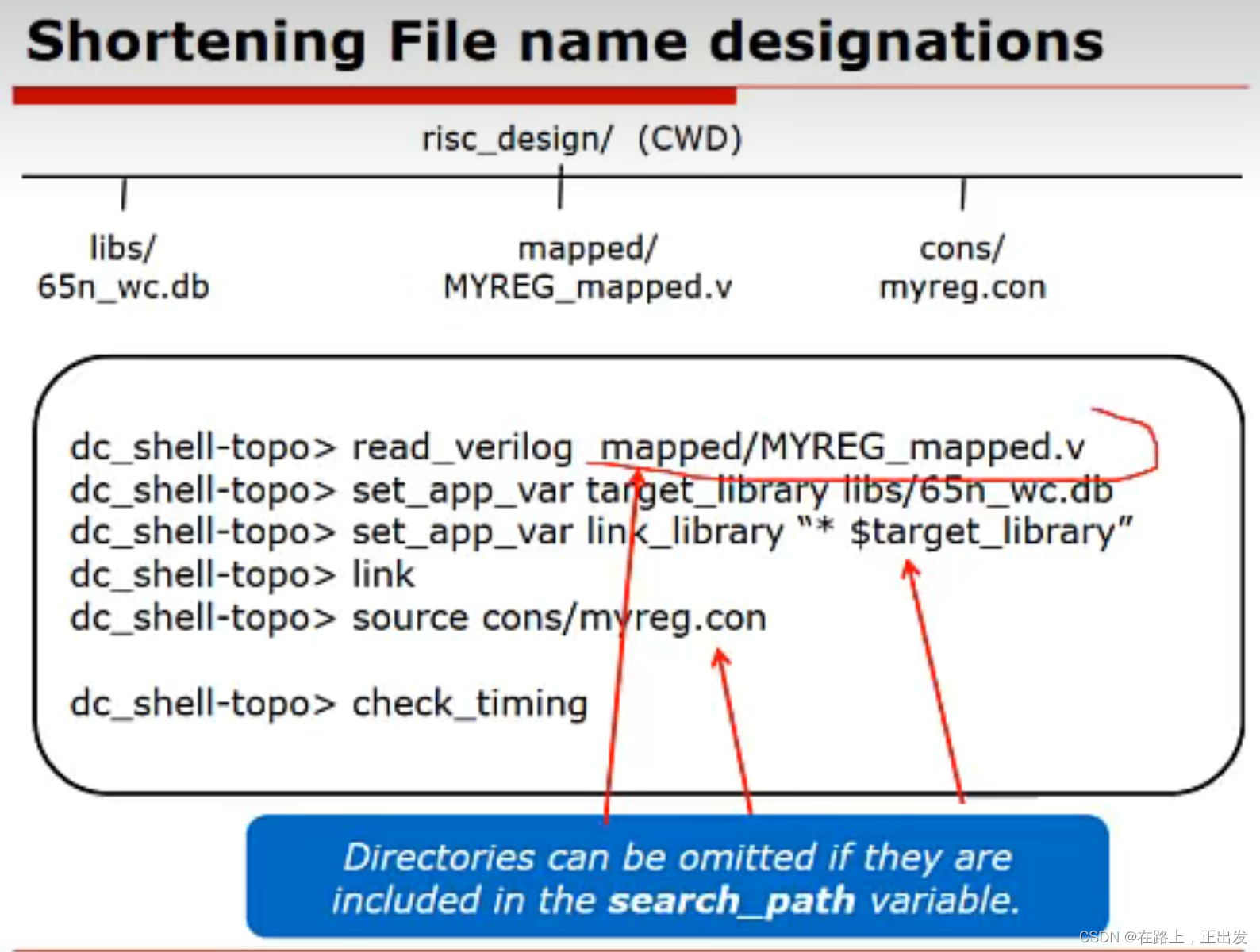

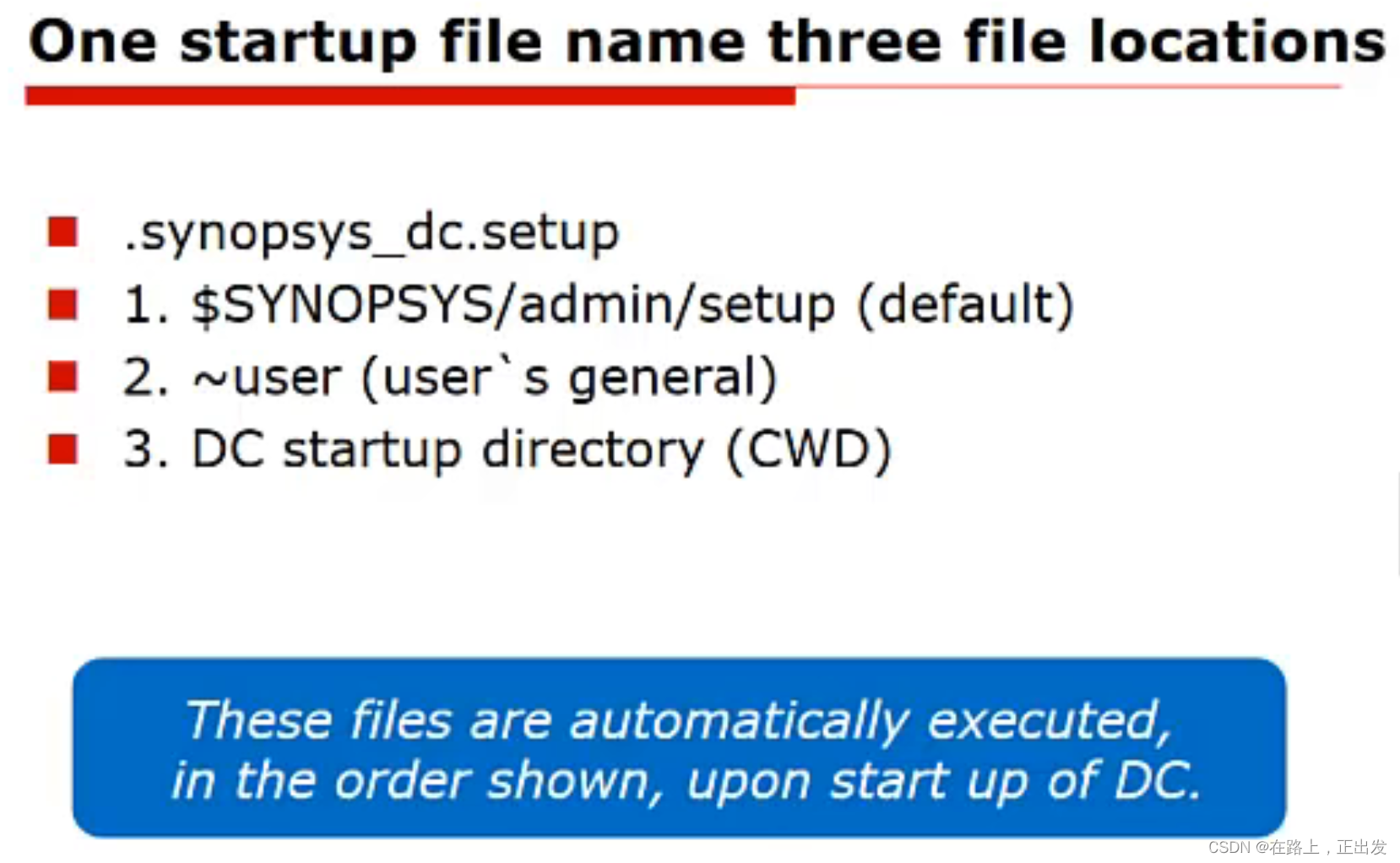

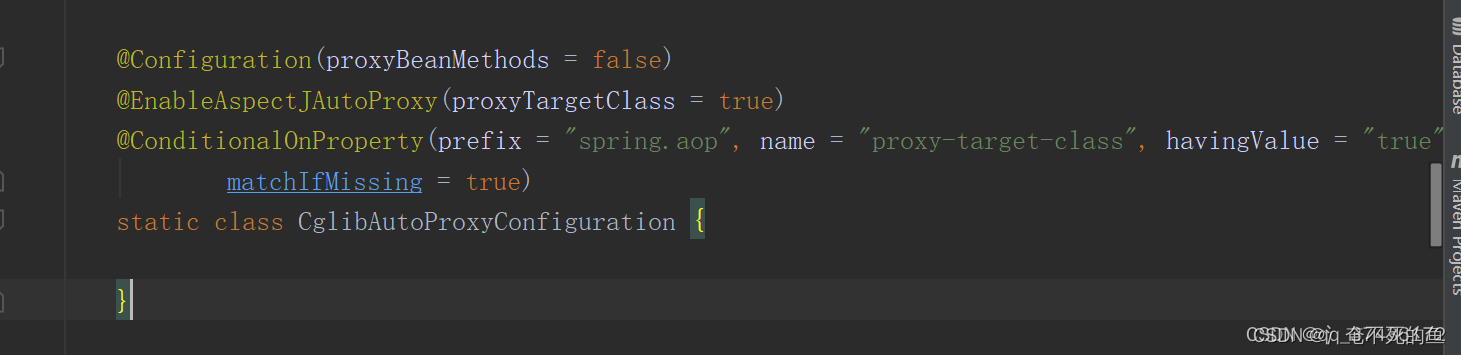

DC在启动前会加载配置文件,下面分别说明。分布在3个地方:DC的安装目录、

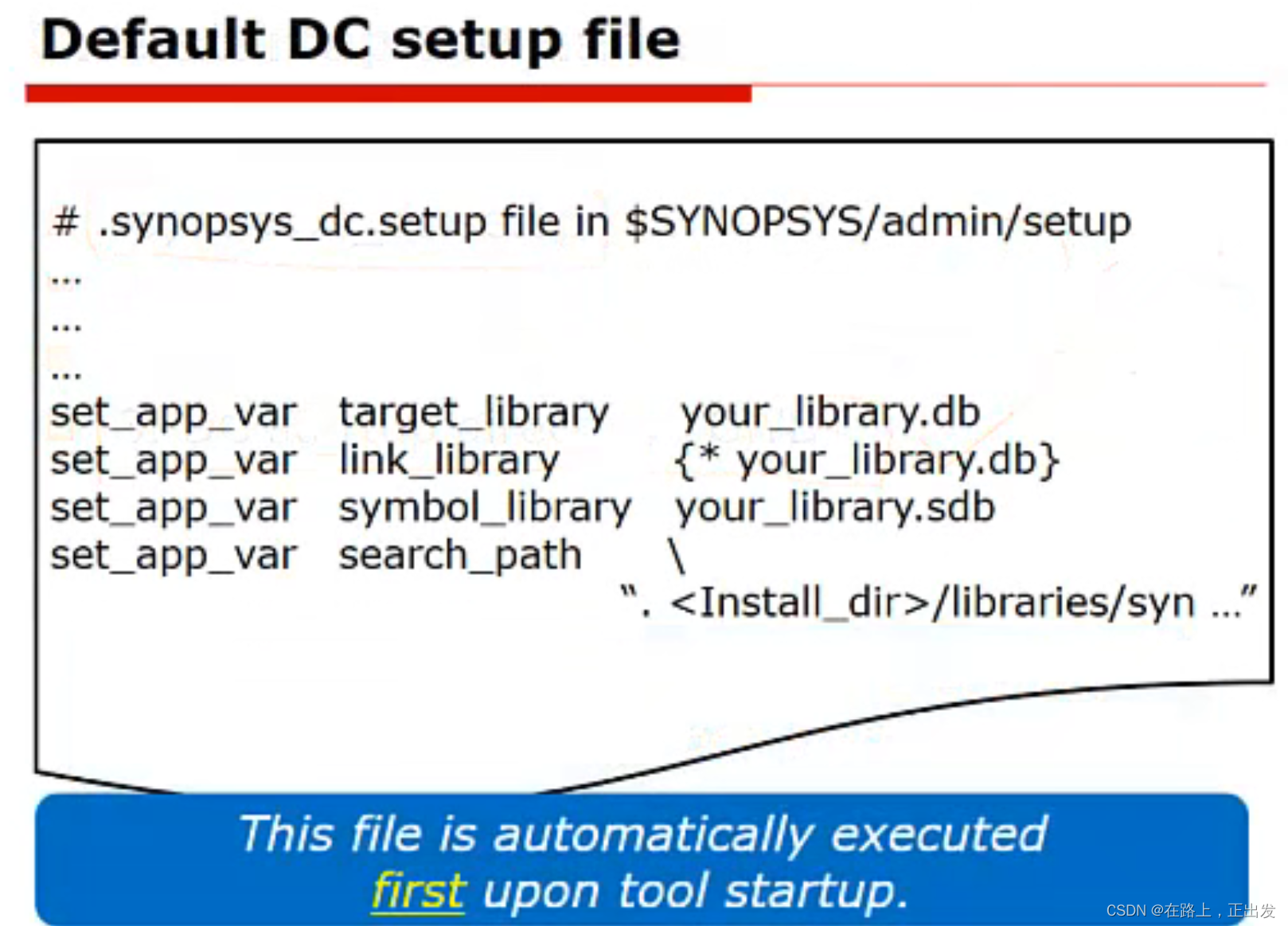

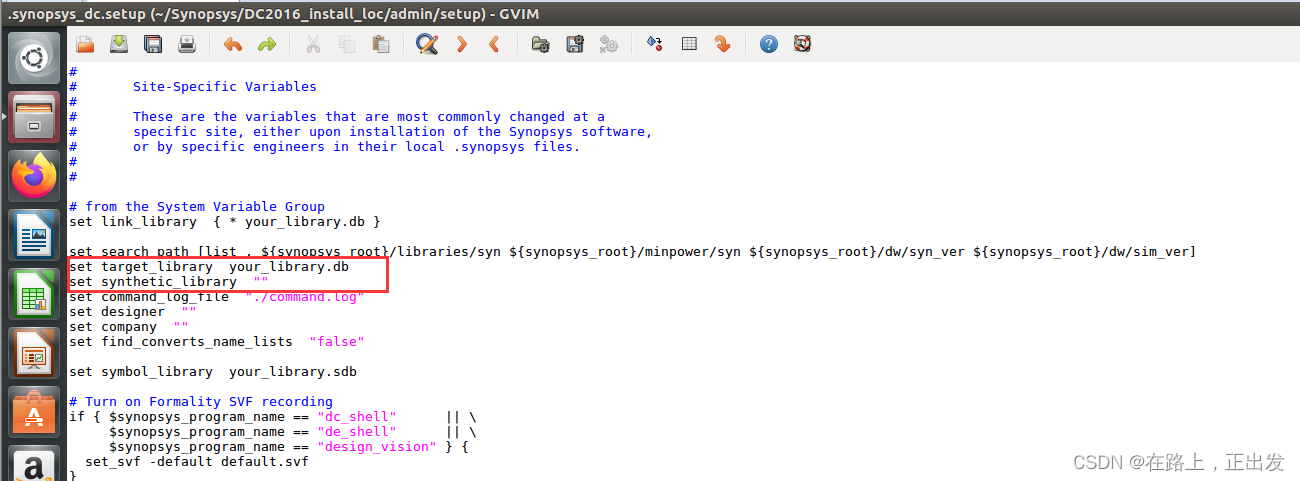

1、.synopsys_dc.setup 配置

1、软件安装目录

1、在DC安装的如下路径下面打开终端:

/Synopsys/DC2016_install_loc/admin/setup

2、在终端输入:

ls -al3、执行如下命令:

gvim .synopsys_dc.setup或者使用 :

gedit .synopsys_dc.setup如果没有安装 vim,可以通过以下的命令来完成:

sudo apt install vim-gtk

打开后可以看到:

2、当前用户的目录

1、终端输入如下命令,切换到当前用户目录

cd ~2、通过下面命令可以看到配置文件

ls -al

我的用户目录没有找到 .synopsys_dc.setup 文件,但是并不影响使用 DC。

3、工程路径下添加 .synopsys_dc.setup

下面是我的启动文件。

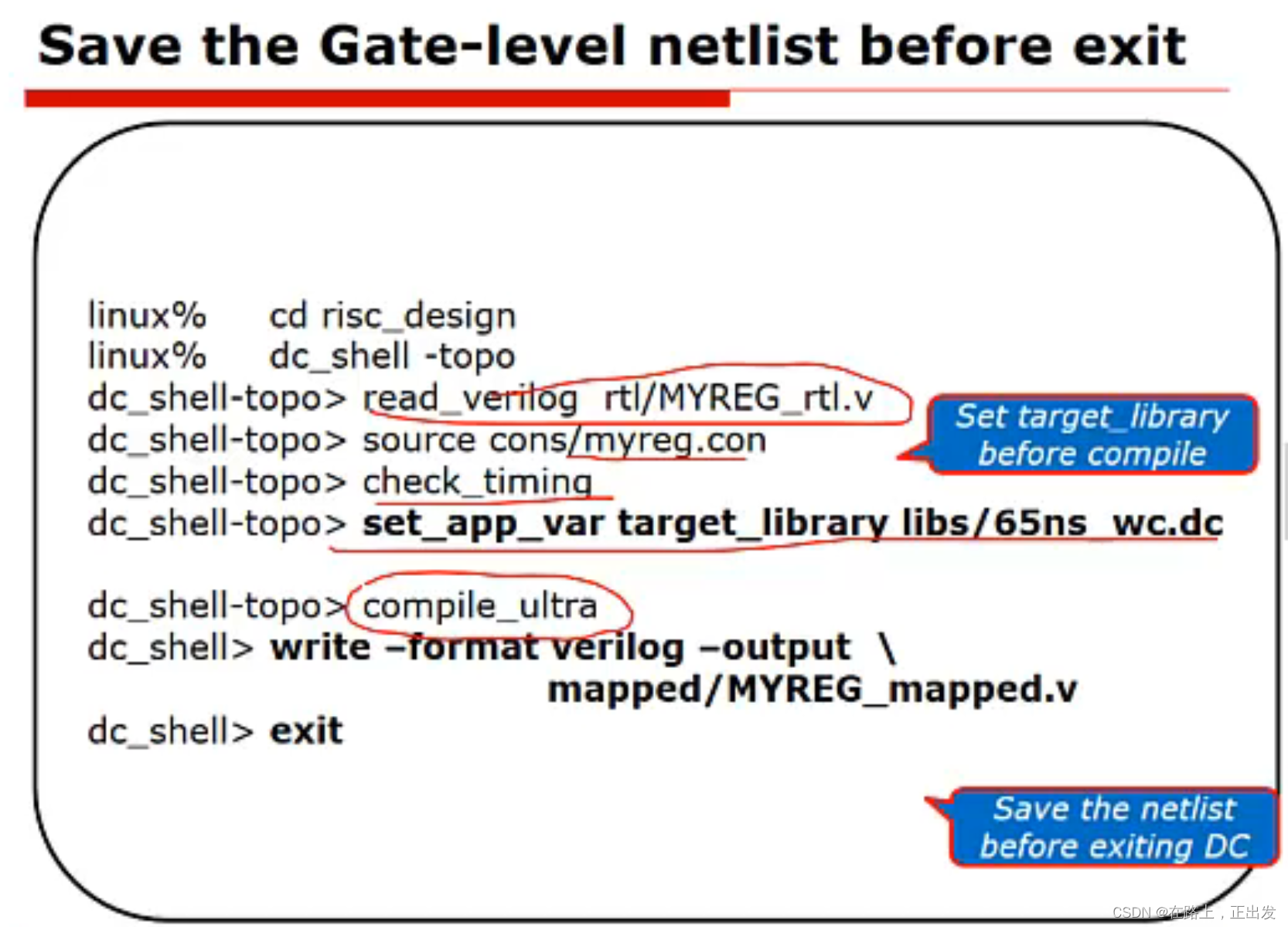

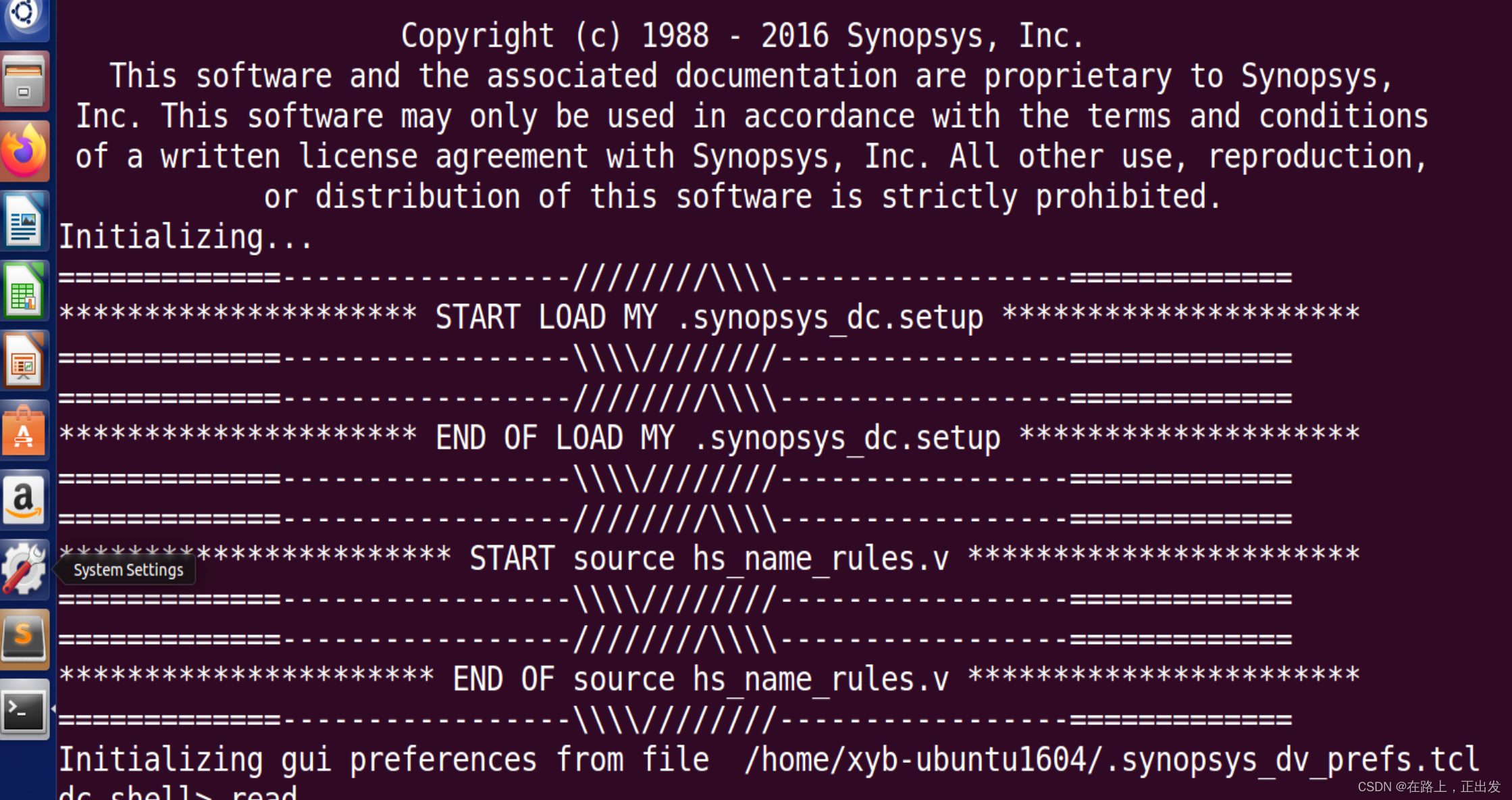

echo "=============-----------------\\\\\\\\-----------------=============" echo "********************* START LOAD MY .synopsys_dc.setup *********************" echo "=============-----------------\\\\\\\\-----------------=============" set SYN_ROOT_PATH /home/xyb-ubuntu1604/XYB/MY_DC/Example_1 set RTL_PATH $SYN_ROOT_PATH/rtl set CONFIG_PATH $SYN_ROOT_PATH/config set SCRIPT_PATH $SYN_ROOT_PATH/script set MAPPED_PATH $SYN_ROOT_PATH/mapped set UNMAPPED_PATH $SYN_ROOT_PATH/unmapped # define work directory set WORK_PATH $SYN_ROOT_PATH/work set DC_PATH /home/xyb-ubuntu1604/XYB/Synopsys_Tool/DC2016 define_design_lib work -path $WORK_PATH set SYMBOL_PATH /home/xyb-ubuntu1604/XYB/MY_STUDY_LIB/smic180/std_cell/fb_2005q4v1/aci/sc-x/symbols/synopsys set LIB_PATH /home/xyb-ubuntu1604/XYB/MY_STUDY_LIB/smic180/std_cell/fb_2005q4v1/aci/sc-x/synopsys set_app_var search_path [list . $search_path $LIB_PATH \ $SYMBOL_PATH $RTL_PATH \ $SCRIPT_PATH \ ${DC_PATH}/libraries/syn] # This virables are automatically set if you perform ultra command. # Specify for use during optimization # You do not need to be anything to access the standard library. # DC is setup to use this lirary by default set_app_var synthetic_library [list dw_foundation.sldb standard.sldb] set_app_var target_library [list typical.db] set_app_var link_library [list * ${target_library} dw_foundation.sldb] set_app_var symbol_library [list smic18.sdb] echo "=============-----------------\\\\\\\\-----------------=============" echo "********************* END OF LOAD MY .synopsys_dc.setup ********************" echo "=============-----------------\\\\\\\\-----------------=============" echo "=============-----------------\\\\\\\\-----------------=============" echo "*********************** START source hs_name_rules.v ***********************" echo "=============-----------------\\\\\\\\-----------------=============" # source -v -e ./hs_name_rules.tcl echo "=============-----------------\\\\\\\\-----------------=============" echo "********************** END OF source hs_name_rules.v ***********************" echo "=============-----------------\\\\\\\\-----------------============="关于hs_name_rules.tcl 文件我没有在网上找到可用的文件,后面的命令暂且注释。

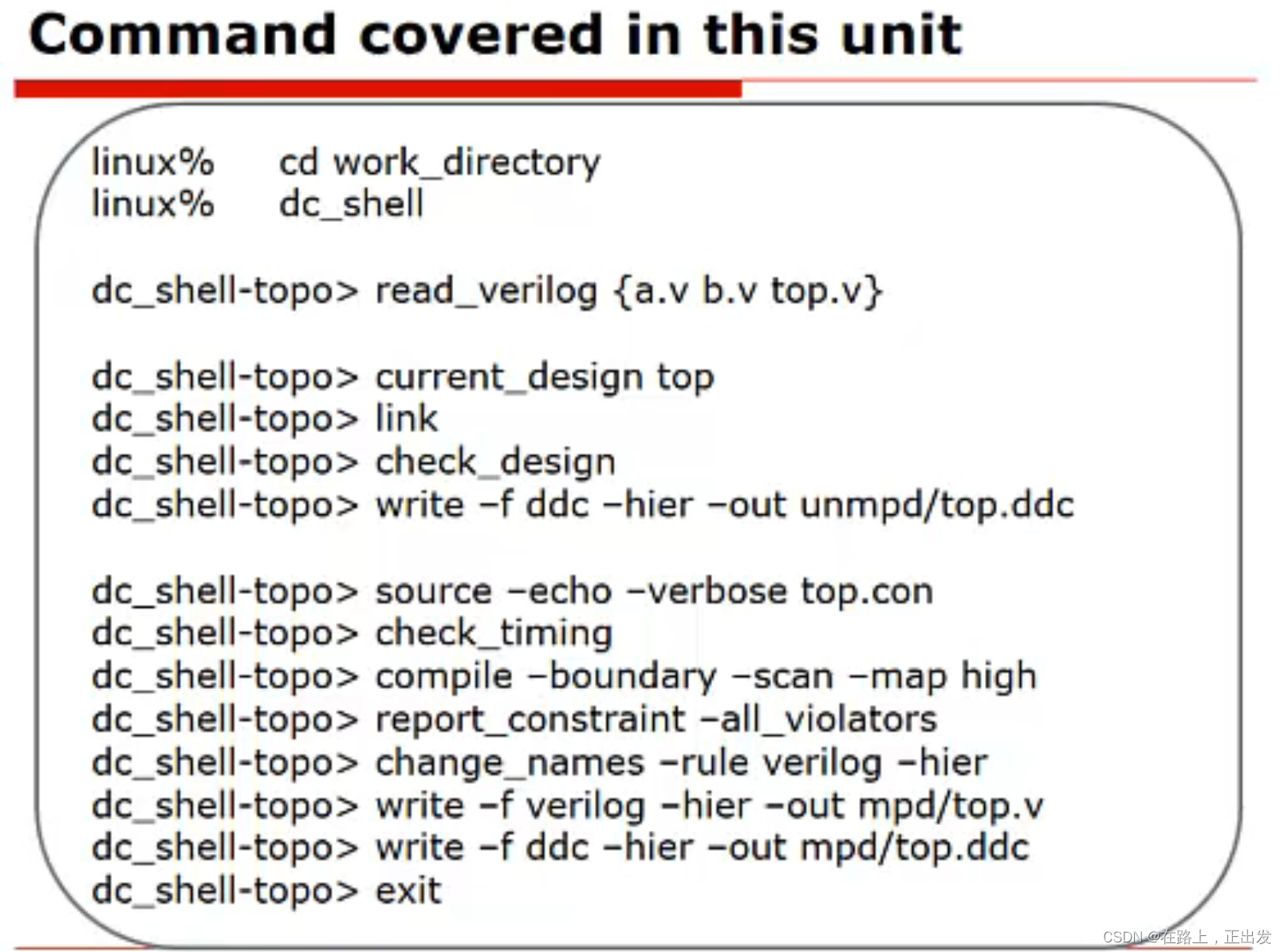

启动 DC

1、输入命令

dc_shell |tee dc_start.log启动 DC 的同时,记录启动的log信息。

启动完成:

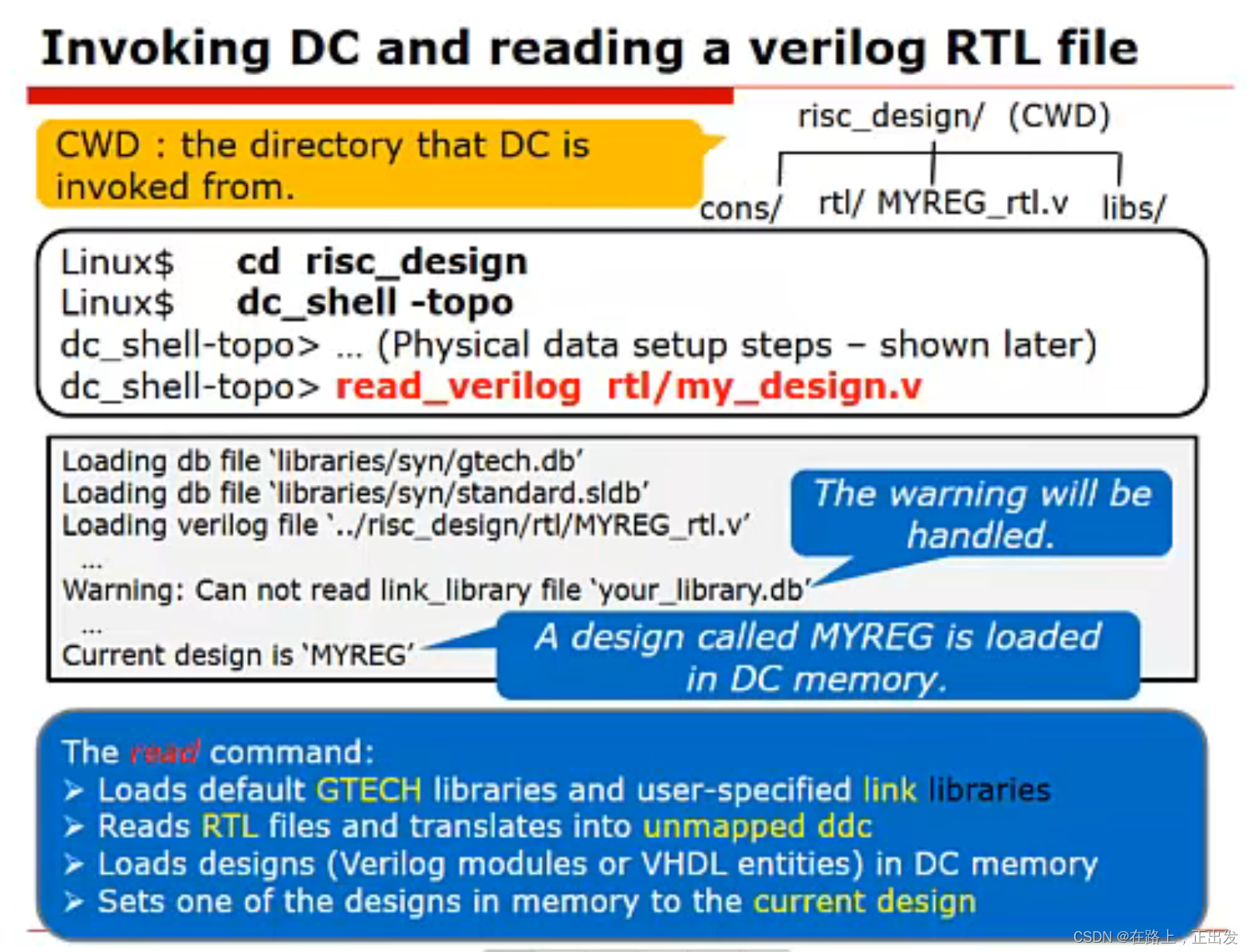

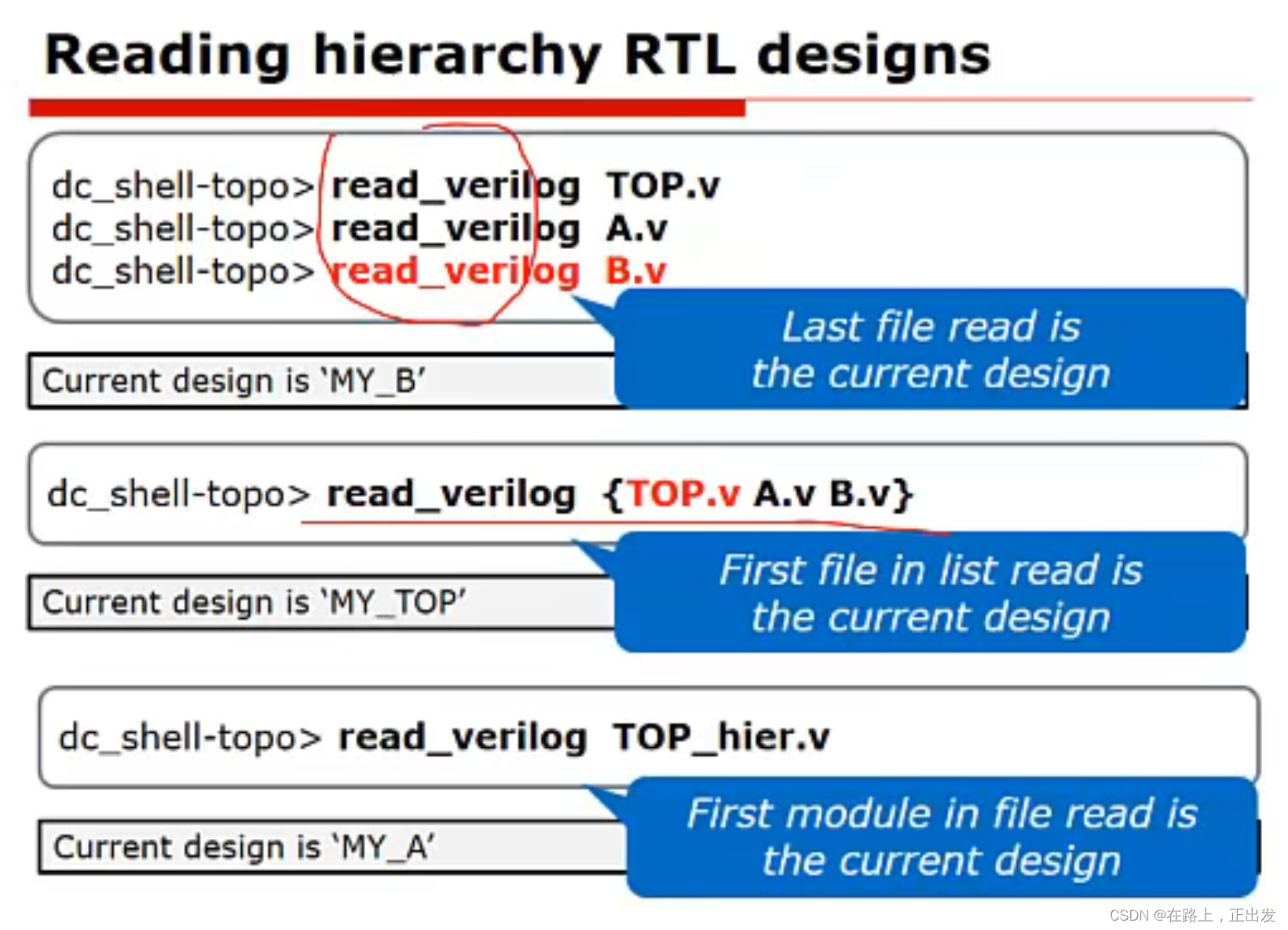

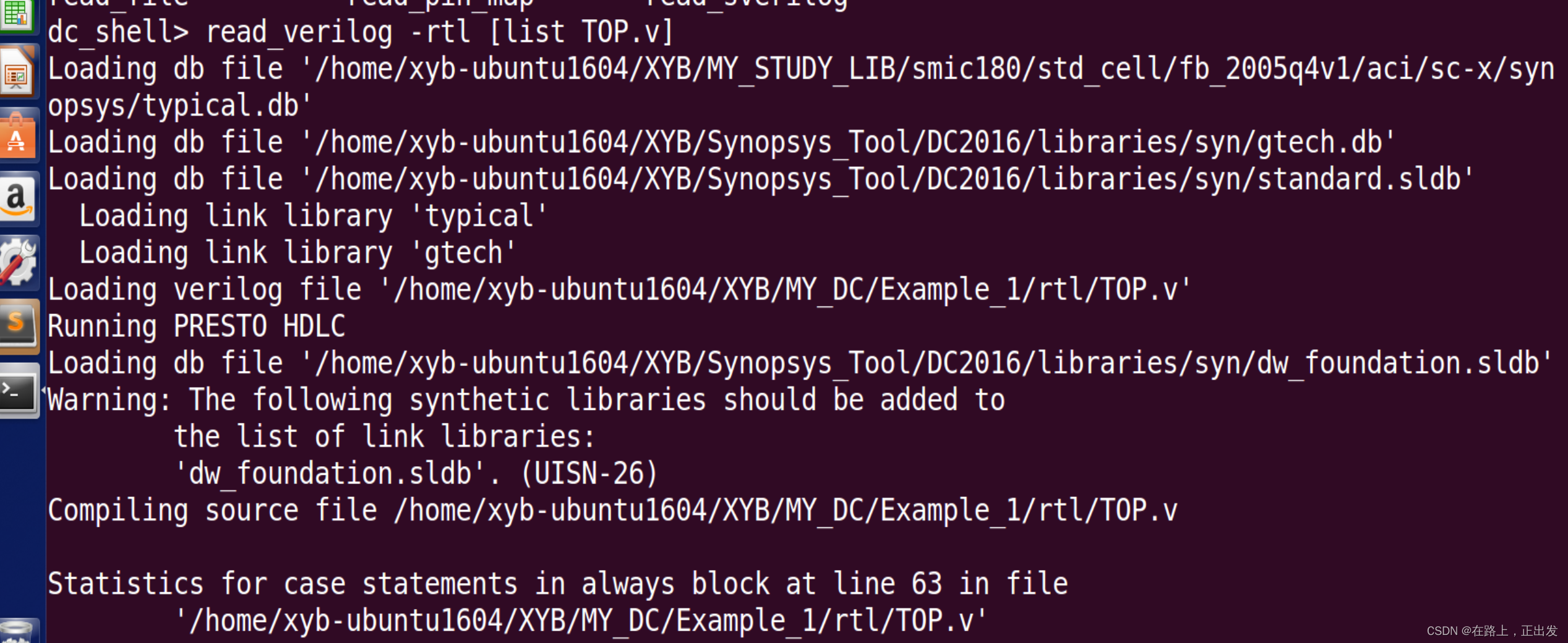

2、读取设计文件

read_verilog -rtl [list TOP.v]

设计文件源代码:

`define RESET_STATE 3'b000 `define FETCH_INSTR 3'b001 `define READ_OPS 3'b010 `define EXECUTE 3'b011 `define WRITEBACK 3'b100 module TOP(Clk, Reset, Crnt_Instrn, Zro_Flag, Carry_Flag, Neg_Flag, Return_Addr, Current_State, PC); input Clk; input Reset; input [31:0] Crnt_Instrn; // Current Executing Inst input Zro_Flag, Carry_Flag, Neg_Flag; // Flags from ALU or Stack input [7:0] Return_Addr; output [2:0] Current_State; // CurrentState from Control FSM output [7:0] PC; // Program Count wire Incrmnt_PC, Ld_Brnch_Addr, Ld_Rtn_Addr; wire [2:0] CurrentState; FSM I_FSM ( .Clk(Clk), .Reset(Reset), .CurrentState(CurrentState) ); DECODE I_DECODE ( .Zro_Flag(Zro_Flag), .Carry_Flag(Carry_Flag), .Neg_Flag(Neg_Flag), .CurrentState(CurrentState), .Crnt_Instrn(Crnt_Instrn), .Incrmnt_PC(Incrmnt_PC), .Ld_Brnch_Addr(Ld_Brnch_Addr), .Ld_Rtn_Addr(Ld_Rtn_Addr) ); COUNT I_COUNT ( .Reset(Reset), .Clk(Clk), .Incrmnt_PC(Incrmnt_PC), .Ld_Brnch_Addr(Ld_Brnch_Addr), .Ld_Rtn_Addr(Ld_Rtn_Addr), .Imm_Addr(Crnt_Instrn[7:0]), .Return_Addr(Return_Addr), .PC(PC) ); assign Current_State = CurrentState; endmodule module FSM(Clk, Reset, CurrentState); input Clk, Reset; // CPU Clock // CPU Reset output [2:0] CurrentState; // Current State of FSM reg [2:0] Current_State, Next_State; always @(Reset or Current_State) begin case (Current_State) `RESET_STATE: begin Next_State <= `FETCH_INSTR; end `FETCH_INSTR: begin Next_State <= `READ_OPS; end `READ_OPS: begin Next_State <= `EXECUTE; end `EXECUTE: begin Next_State <= `WRITEBACK; end `WRITEBACK: begin Next_State <= `FETCH_INSTR; end default : begin Next_State <= `RESET_STATE; end endcase end always @( posedge Clk) begin if (Reset == 1'b1) begin Current_State <= `RESET_STATE; end else begin Current_State <= Next_State; end end assign CurrentState = Current_State; endmodule module DECODE(Zro_Flag, Carry_Flag, Neg_Flag, CurrentState, Crnt_Instrn, Incrmnt_PC, Ld_Brnch_Addr, Ld_Rtn_Addr); input Zro_Flag, Carry_Flag, Neg_Flag; // "Zero" Flag from DATA_PATH // "Carry" Flag from DATA_PATH // "Negative" Flag from DATA_PATH input [2:0] CurrentState; // CurrentState from FSM input [31:0] Crnt_Instrn; // Current instruction under execution // from Instruction Latch output Incrmnt_PC, Ld_Brnch_Addr, Ld_Rtn_Addr; // Increments PC (in WRITEBACK cycle) reg Incrmnt_PC; // appended automatically by vhdl2verilog. // Load Immediate add from Instrn Latch // into PC (in WRITEBACK cycle) // Load Return addr from Stack into PC (in WRITEBACK cycle) reg Brnch_Addr, Rtn_Addr, Take_Branch; reg Neg, Carry, Zro, Jmp; always @(Take_Branch or CurrentState or Crnt_Instrn or Zro_Flag or Carry_Flag or Neg_Flag or Brnch_Addr or Rtn_Addr) begin Brnch_Addr <= 1'b0; Rtn_Addr <= 1'b0; // Determine if Jmp on False or Jmp on True if ((Crnt_Instrn[25]) == 1'b1) begin Neg = ~Neg_Flag; Carry = ~Carry_Flag; Zro = ~Zro_Flag; Jmp = 1'b0; end else begin Neg = Neg_Flag; Carry = Carry_Flag; Zro = Zro_Flag; Jmp = 1'b1; end // Determines which of the CONDITIONs needs to be checked and whether to jmp if (Crnt_Instrn[23:16] == 8'b00000000) begin Take_Branch <= Neg; end else if (Crnt_Instrn[23:16] == 8'b00000001) begin Take_Branch <= Zro; end else if (Crnt_Instrn[23:16] == 8'b00000010) begin Take_Branch <= Carry; end else if (Crnt_Instrn[23:16] == 8'b00111111) begin Take_Branch <= Jmp; end else begin Take_Branch <= 1'b0; end case (CurrentState) `WRITEBACK: begin if (Crnt_Instrn[31:30] == 2'b00) begin // For Jmp/Call with condition check if ((Crnt_Instrn[29] == 1'b1 || Crnt_Instrn[28] == 1'b1) && Take_Branch == 1'b1) begin Brnch_Addr <= 1'b1; end // For Return if (Crnt_Instrn[27] == 1'b1) begin Rtn_Addr <= 1'b1; end end // If not Jmping or Rtrning the increment PC if (Rtn_Addr == 1'b1 || Brnch_Addr == 1'b1) begin Incrmnt_PC <= 1'b0; end else begin Incrmnt_PC <= 1'b1; end end default: begin Incrmnt_PC <= 1'b0; end endcase end assign Ld_Brnch_Addr = Brnch_Addr; assign Ld_Rtn_Addr = Rtn_Addr; endmodule module COUNT(Reset, Clk, Incrmnt_PC, Ld_Brnch_Addr, Ld_Rtn_Addr, Imm_Addr, Return_Addr, PC); input Reset, Clk, Incrmnt_PC, Ld_Brnch_Addr, Ld_Rtn_Addr; // Reset for the PC // CPU Clock // Increment PC // Load Jmp/Call Addr from instruction // Load Return Addr input [7:0] Imm_Addr, Return_Addr; // Immediate Addr for Jmp/Call // Return addr from Stack output [7:0] PC; // Addr of instruction to be fetched in // the next Fetch Cycle reg [7:0] PCint; always @(posedge Clk) begin if (Reset == 1'b1) begin PCint <= 8'b00000000; end else if (Incrmnt_PC == 1'b1) begin // Occurs in WRITEBACK cycle PCint <= PCint + 3'b001; end else if (Ld_Rtn_Addr == 1'b1) begin // Occurs in WRITEBACK cycle PCint <= Return_Addr; end else if (Ld_Brnch_Addr == 1'b1) begin // Occurs in WRITEBACK cycle PCint <= Imm_Addr; end end assign PC = PCint; endmodule

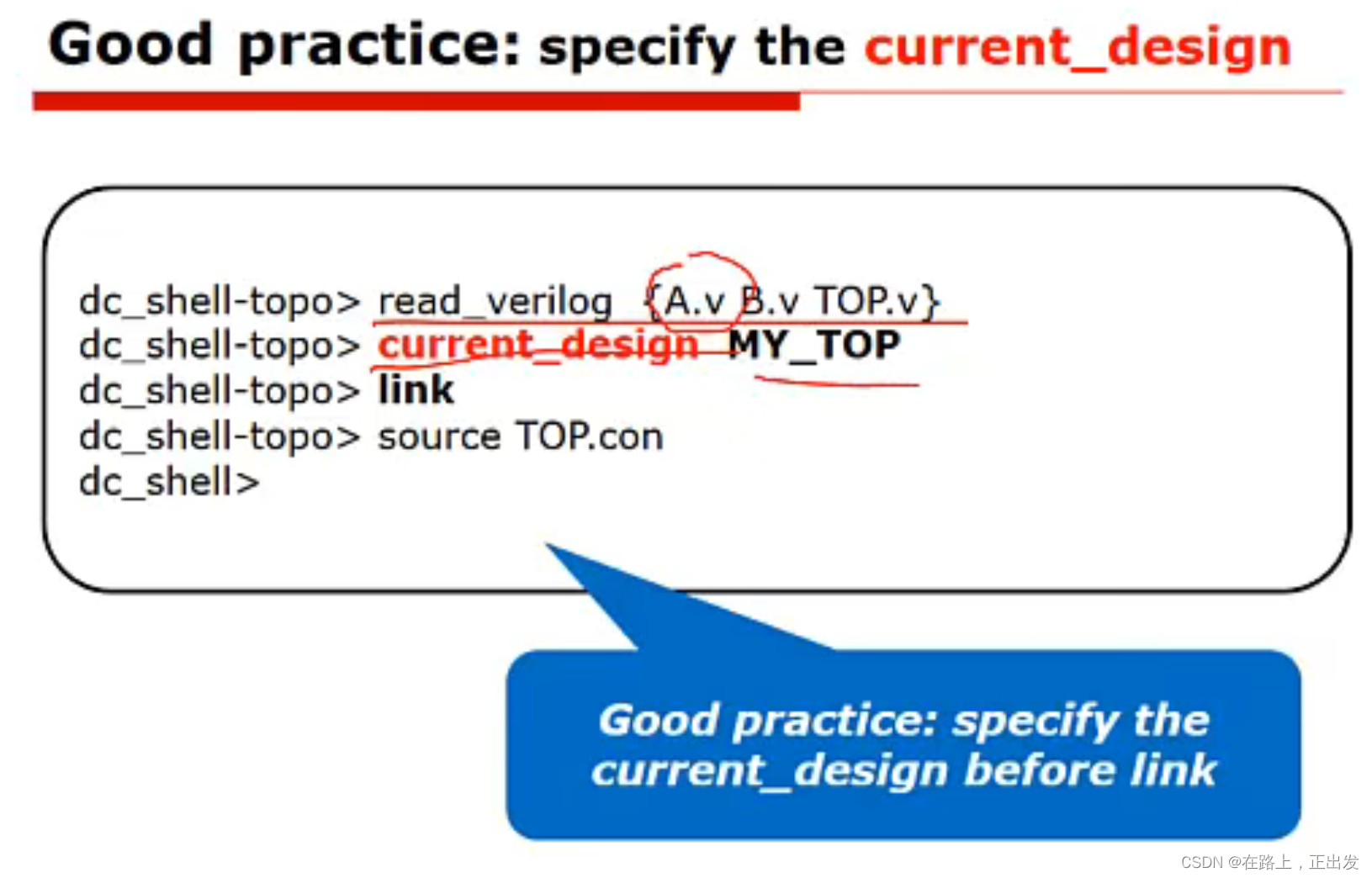

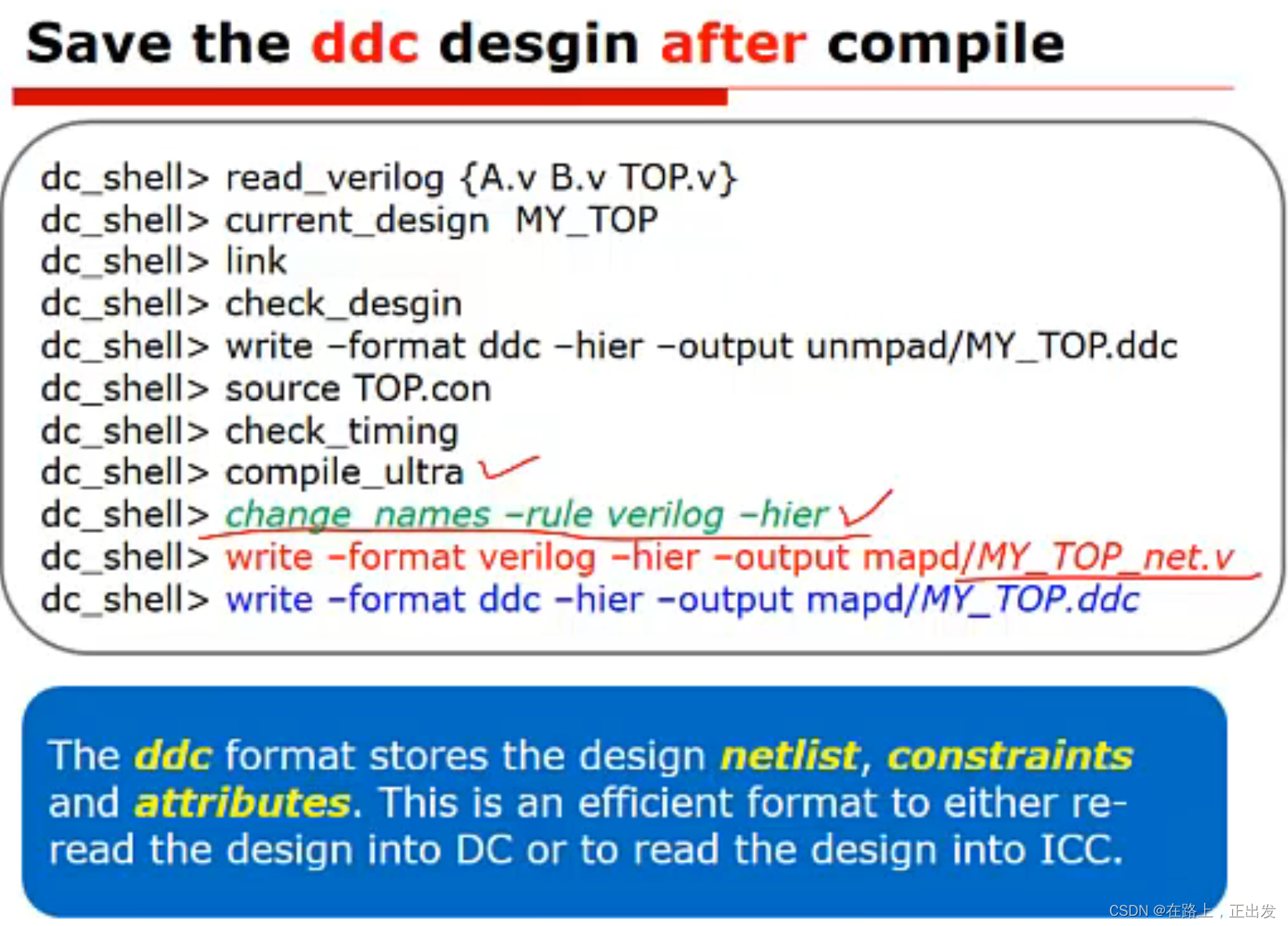

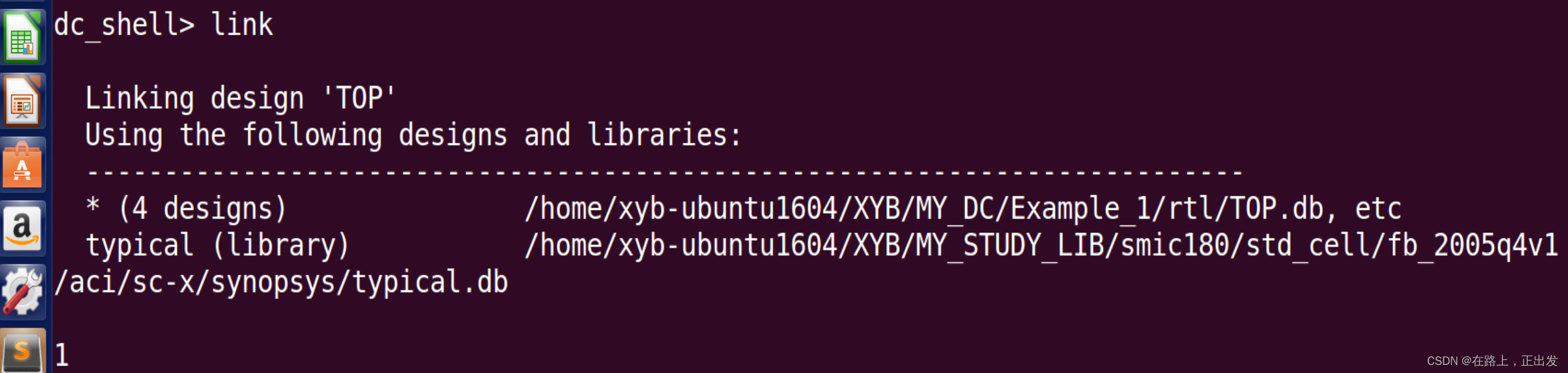

3、link

其他

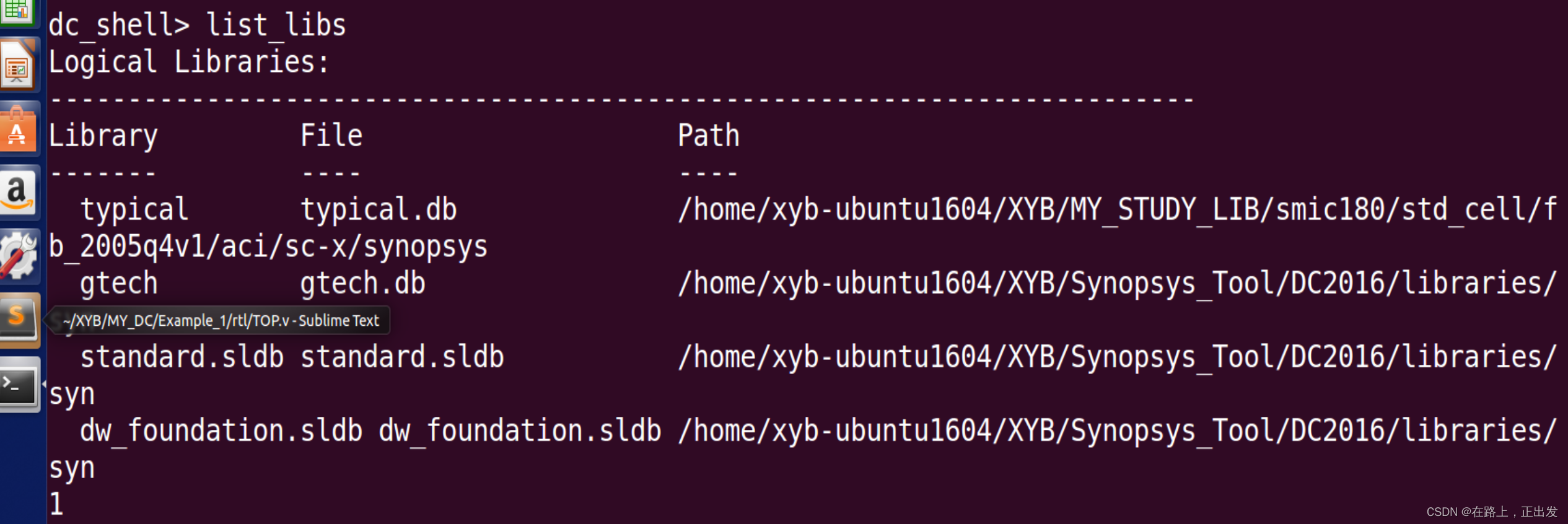

list_libs

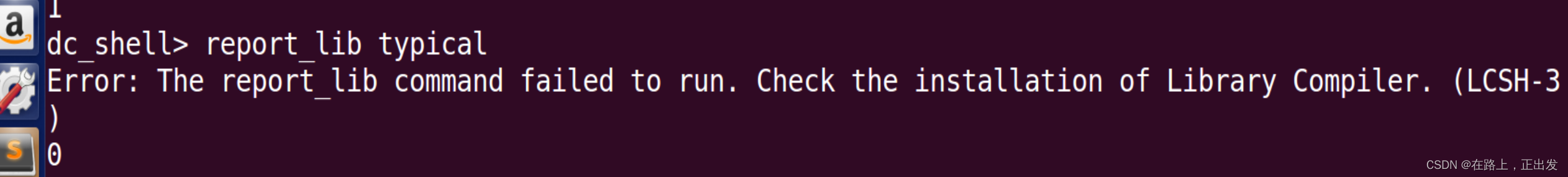

report_lib <库名称>

此命令可以查看某一工艺库的信息。我这里报错主要因为没安装 library compiler

-help

示例:

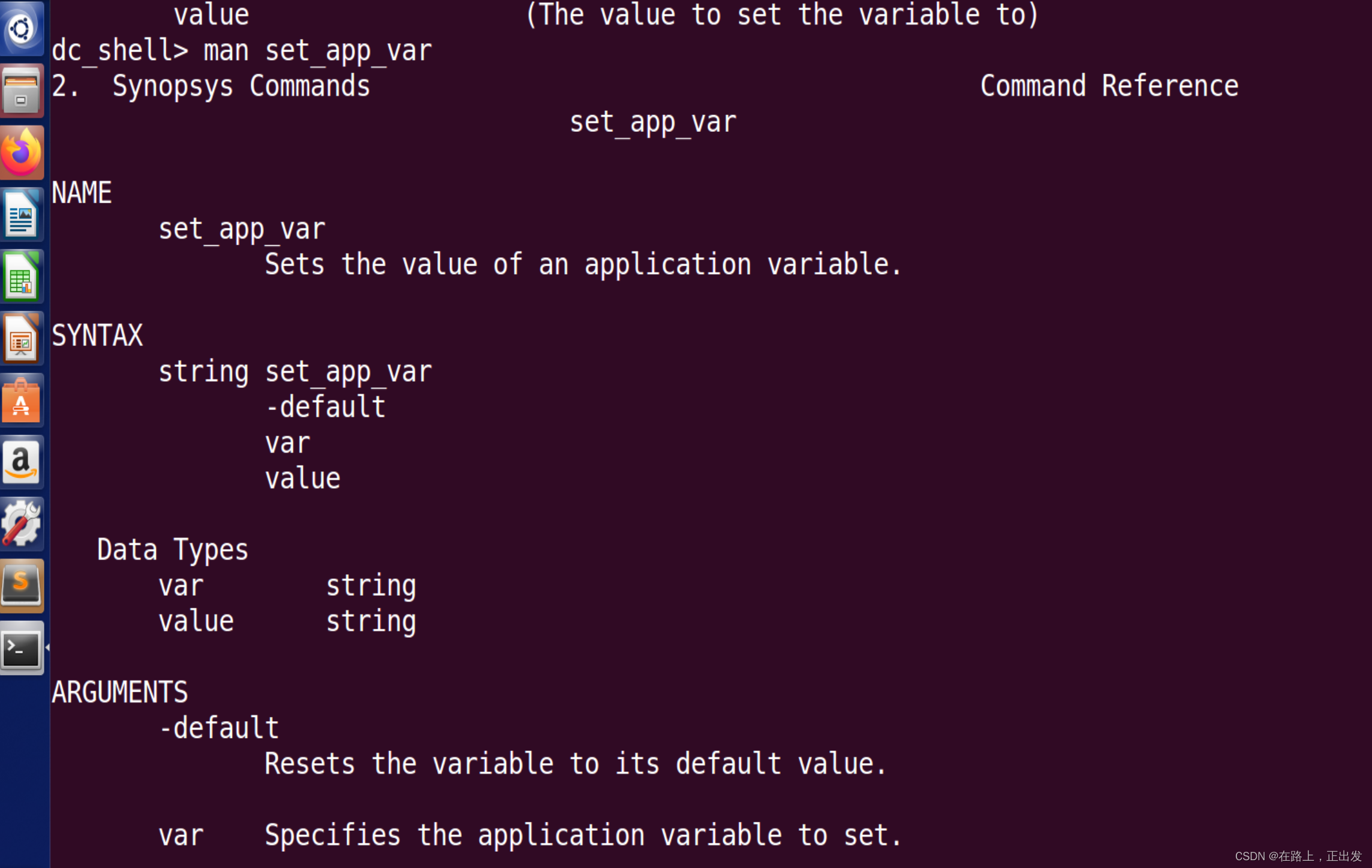

man

查看某一个命令的详细用法

示例:

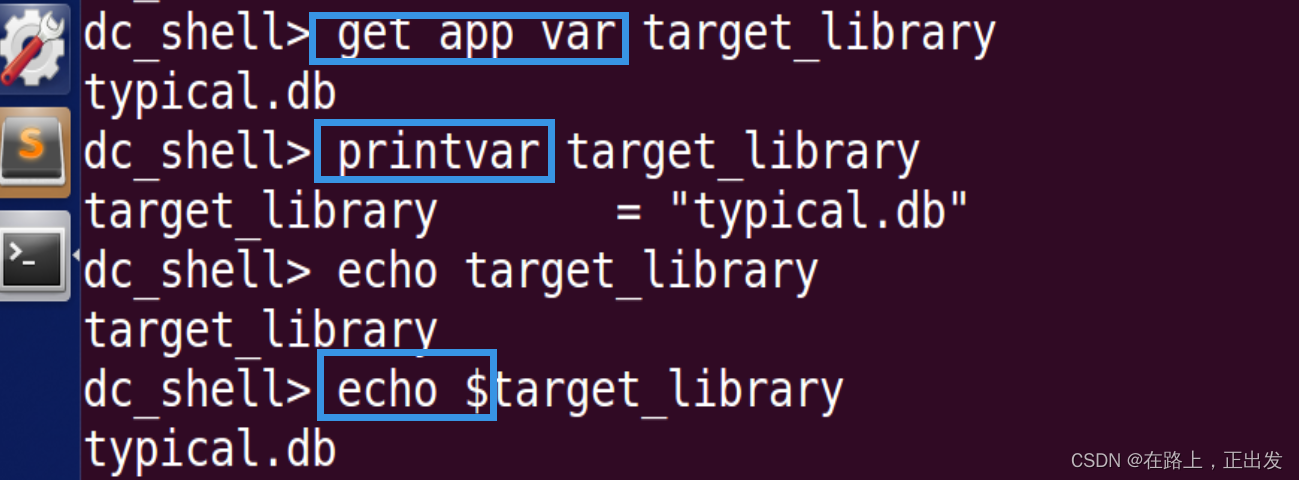

打印环境变量

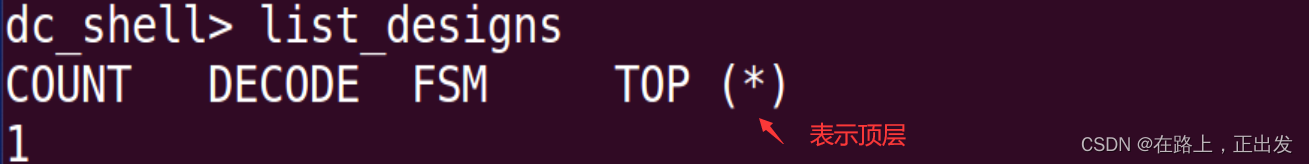

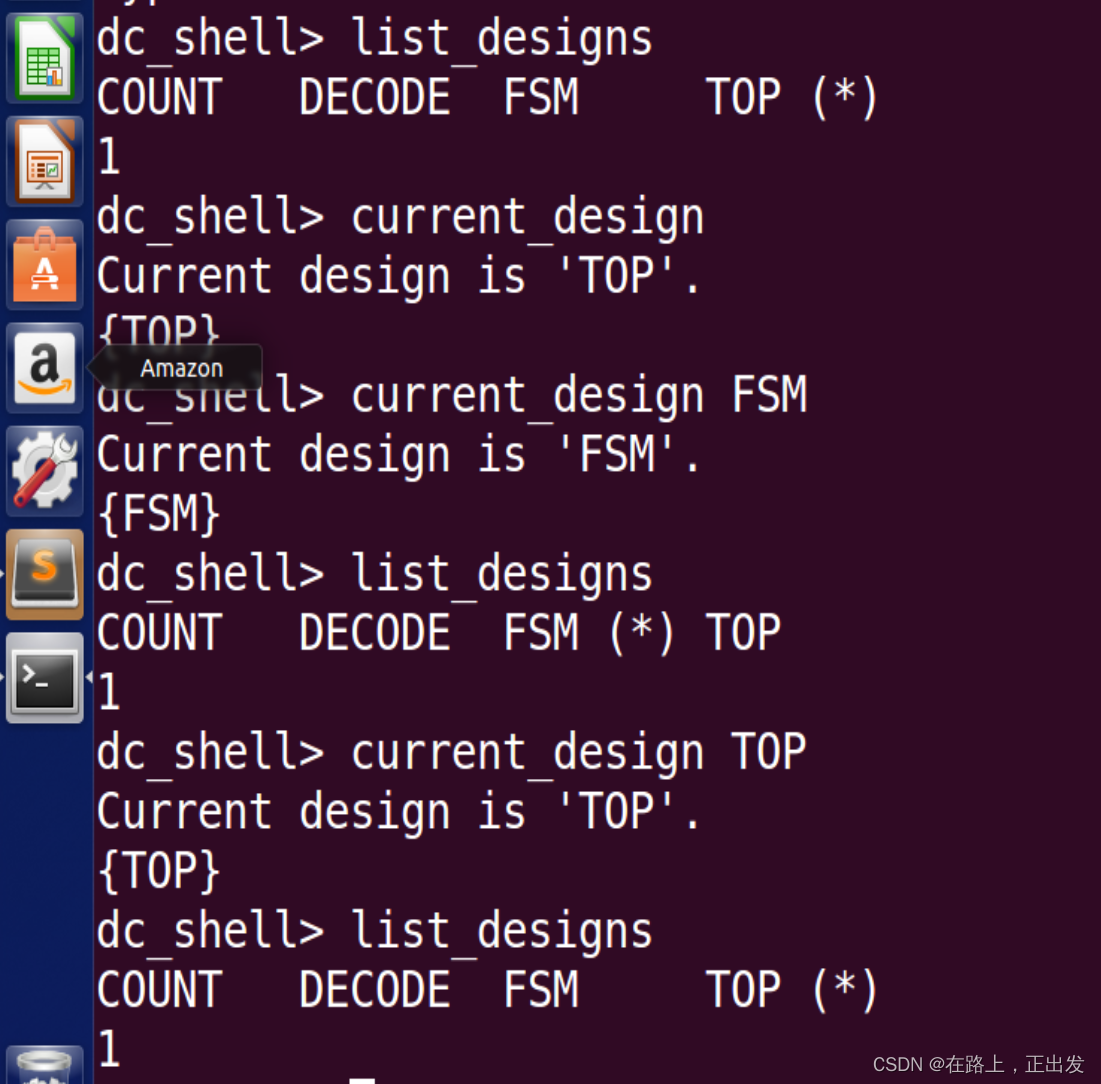

list_designs

current_design

参考说明

1、数字IC设计之综合工具Synopsys DC(2)

2、新新新手Icer练习(二):Synopsys Design Compiler (DC) 基础操作

欢迎交流~~~

![[附源码]SSM计算机毕业设计电子病历信息管理系统JAVA](https://img-blog.csdnimg.cn/ef1a6f7297e94e8ba0c7f955cb57666a.png)