目录

标题1.首先是七段数码管

标题二:有限状态机控制的8*8位乘法器

标题三:单周期MIPS CPU设计

标题1.首先是七段数码管

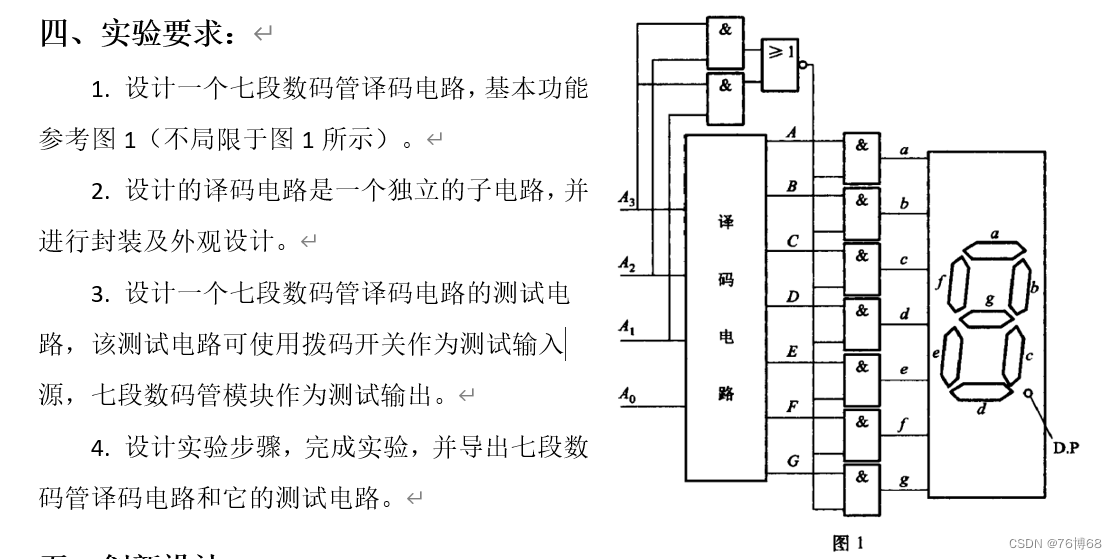

1看一下实验要求:

2.接下来就是详细设计:

1. 组合逻辑设计

由于7段数码管由7个发光的数码管构成,因为我们想用二进制将0-9这几个数字表示出来。所以他需要4位数字才能够把这7个数码管表示的数字都囊括其中,这7位输出来控制发光二极管来显示数字0~9。

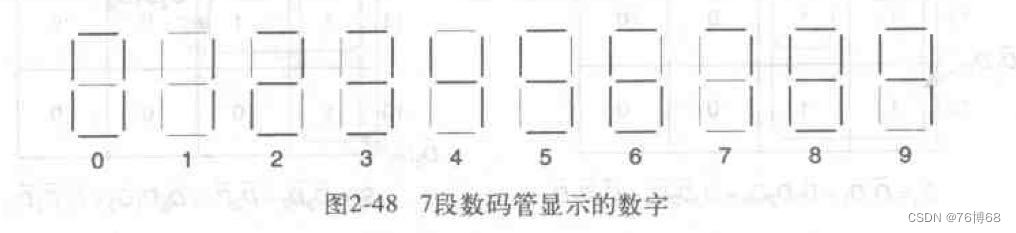

首先先列出七段数码管显示的数字:

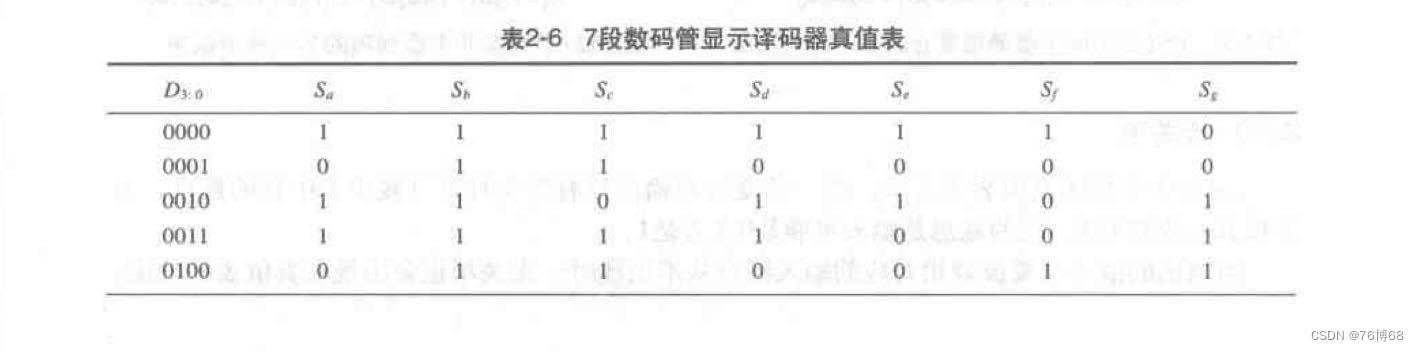

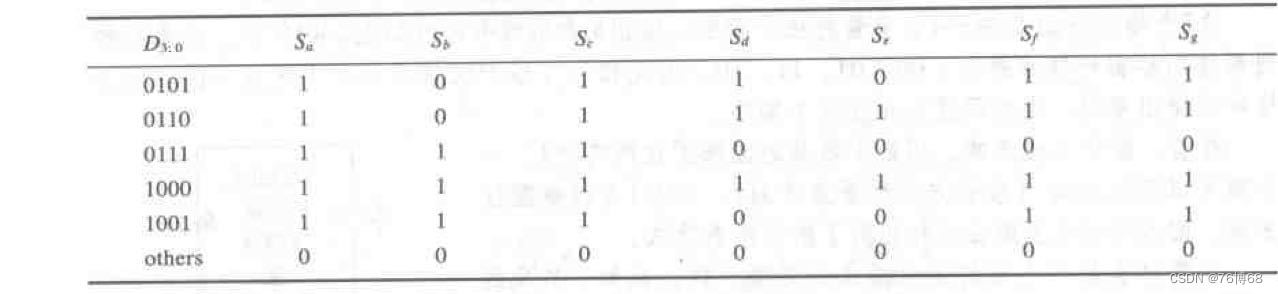

由此可见,例如:当想要输出零这个数字时,除了g这段数码管不亮以外,其他的数码管都要亮,以此类推,我们用二进制表示要输出的数字,比如0001那就是要输出1,0010就是要输出2。由此我们可以得到7段数码管显示译码器真值表:

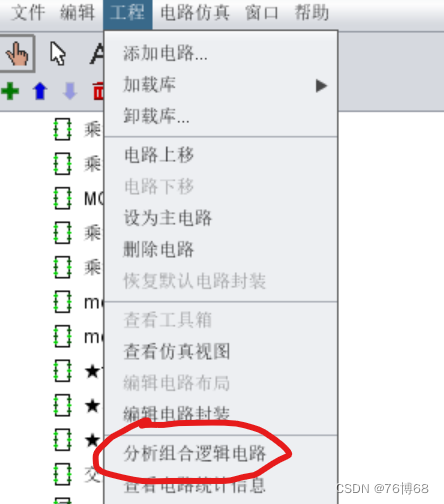

得到真值表后,接着便是组合逻辑电路的实现。这里利用logisim里的自动生成电路功能:

得到真值表后,接着便是组合逻辑电路的实现。这里利用logisim里的自动生成电路功能:

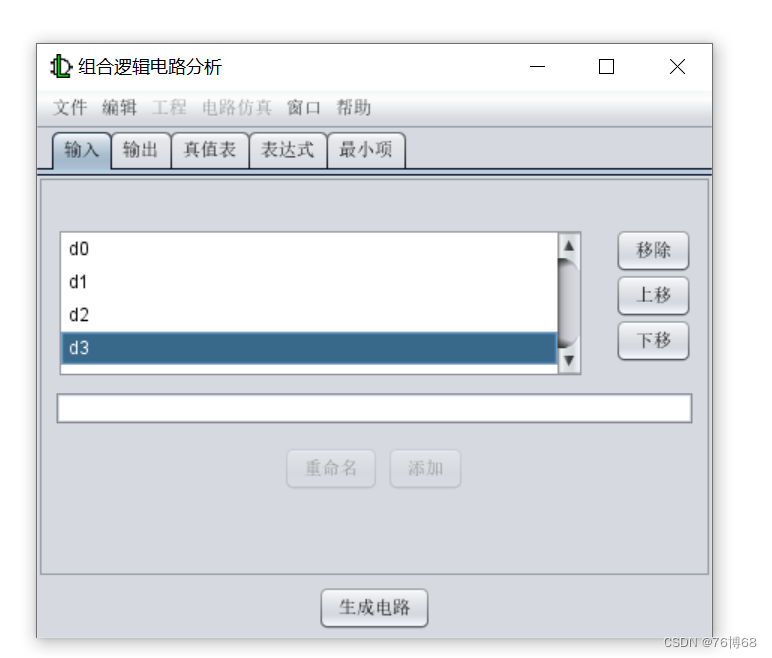

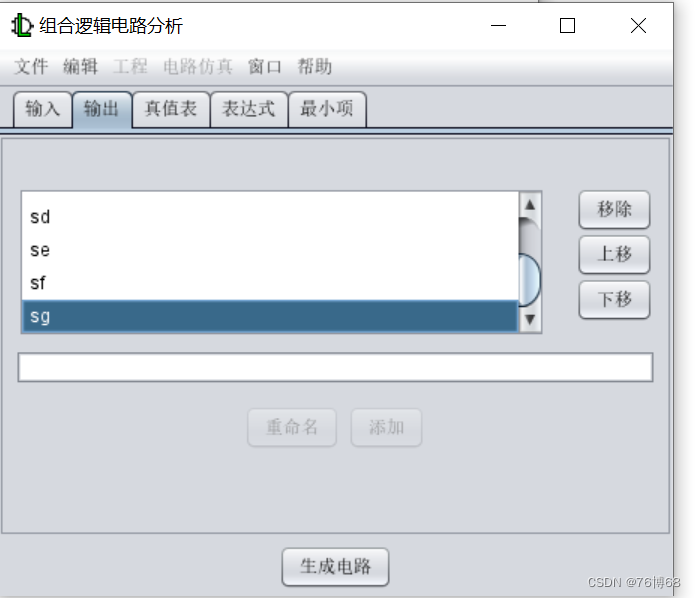

然后确定输入和输出

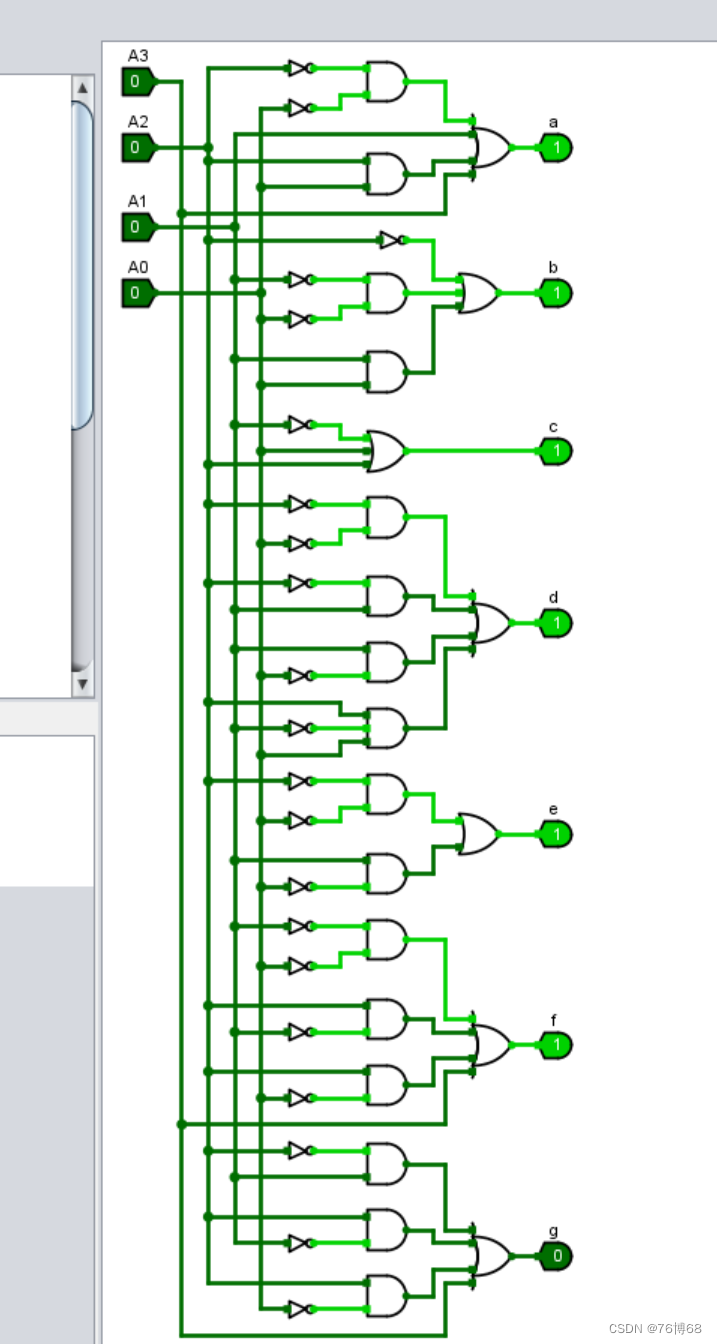

然后选择真值表的形式依次填入上面得到的译码器真值表(注意和上表一致,others部分全部设置为0),表达式和最小项不用管,设置完成后点击生成电路。就会得到这样一个译码电路:

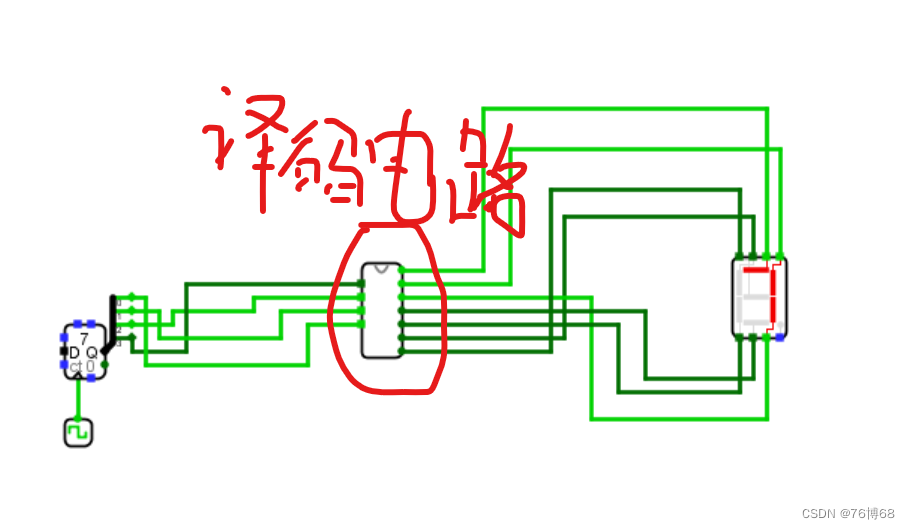

接着就是电路的实现,我用一个计数器加时钟来实现输入,当clock时钟为上升沿时,计数器加一,然后用分线器变成二进制输入到封装好的译码电路,七段数码管直接用logisim里的。测试结果完美!

标题二:有限状态机控制的8*8位乘法器

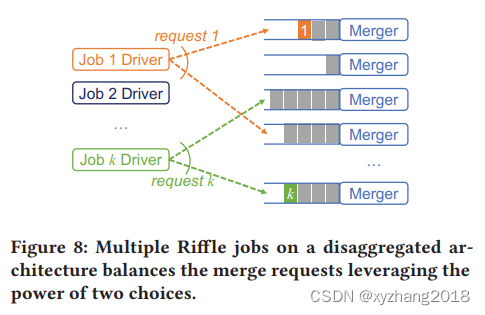

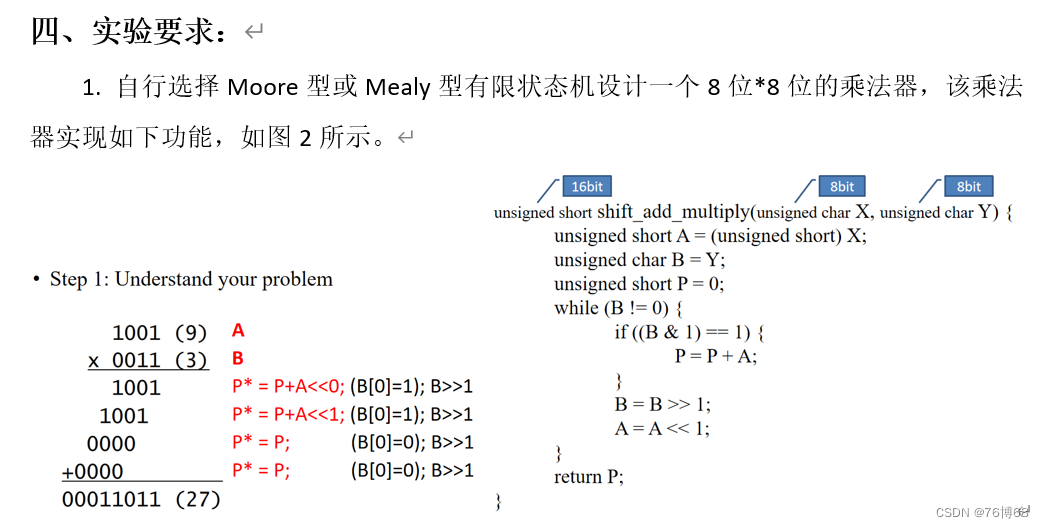

注意,这个乘法器不是普通的乘法器,它是由Moore型有限状态机控制的乘法器

1.实验要求:

2.详细设计:

时序逻辑设计

首先,由于采用有限状态机作为控制电路,我们需要先确认有限状态机的输入与输出

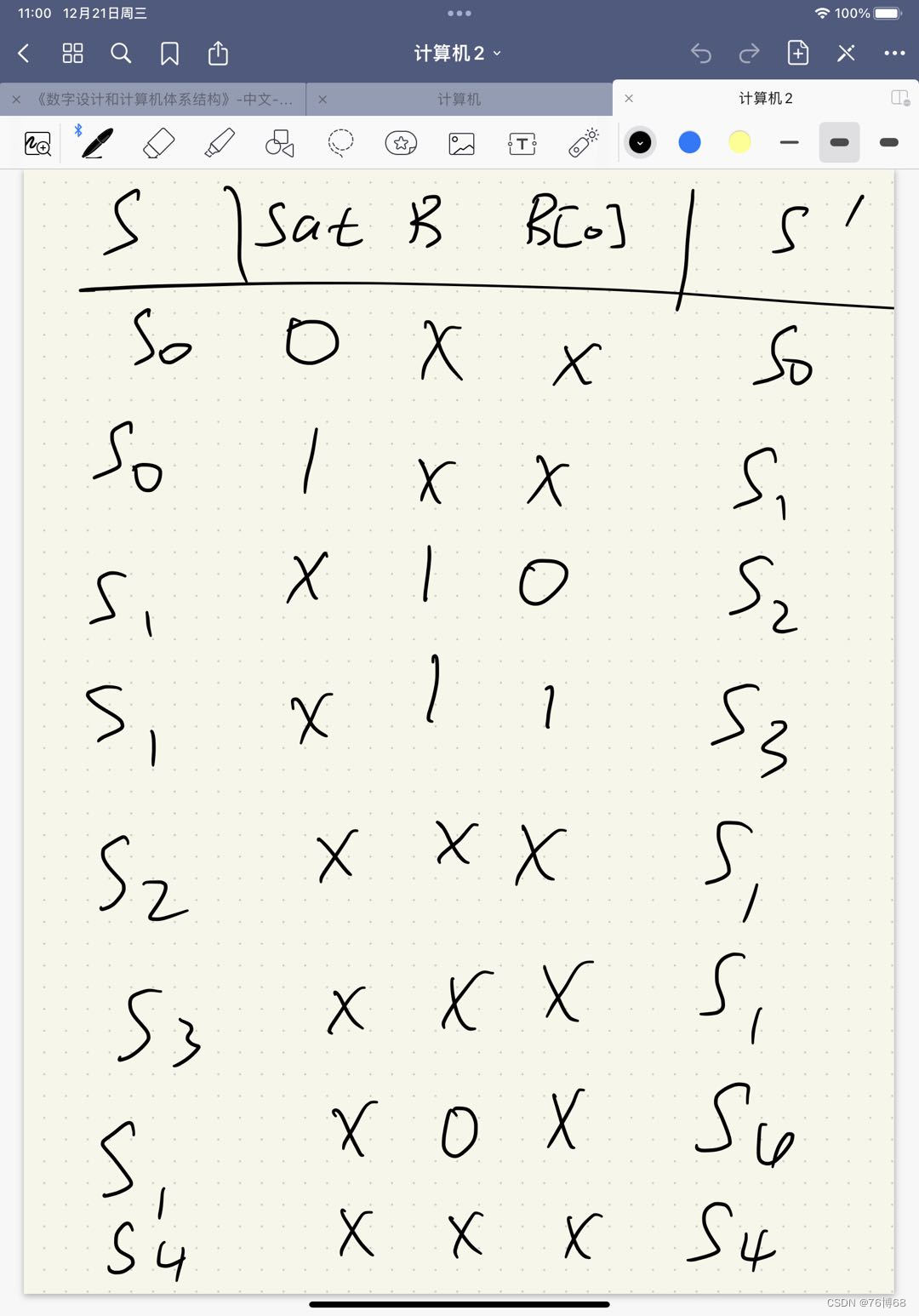

由此可见,有限状态机有三个输入,7个输出(因为还有一个done信号,表示运算结束),这里我们不采用ALU,使用普通的加法器,因此LP信号可以不用给出,所以少了一个输出,变成了6个。接下来便是控制电路的设计。首先先画出状态转换图,如下,sat表示start信号:

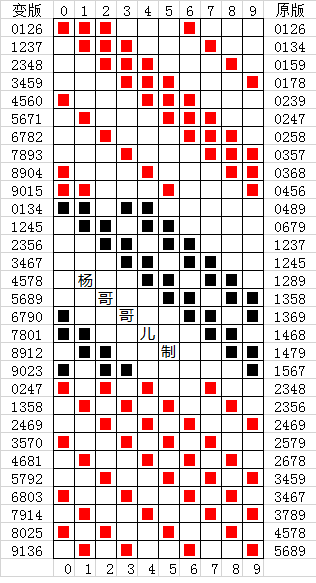

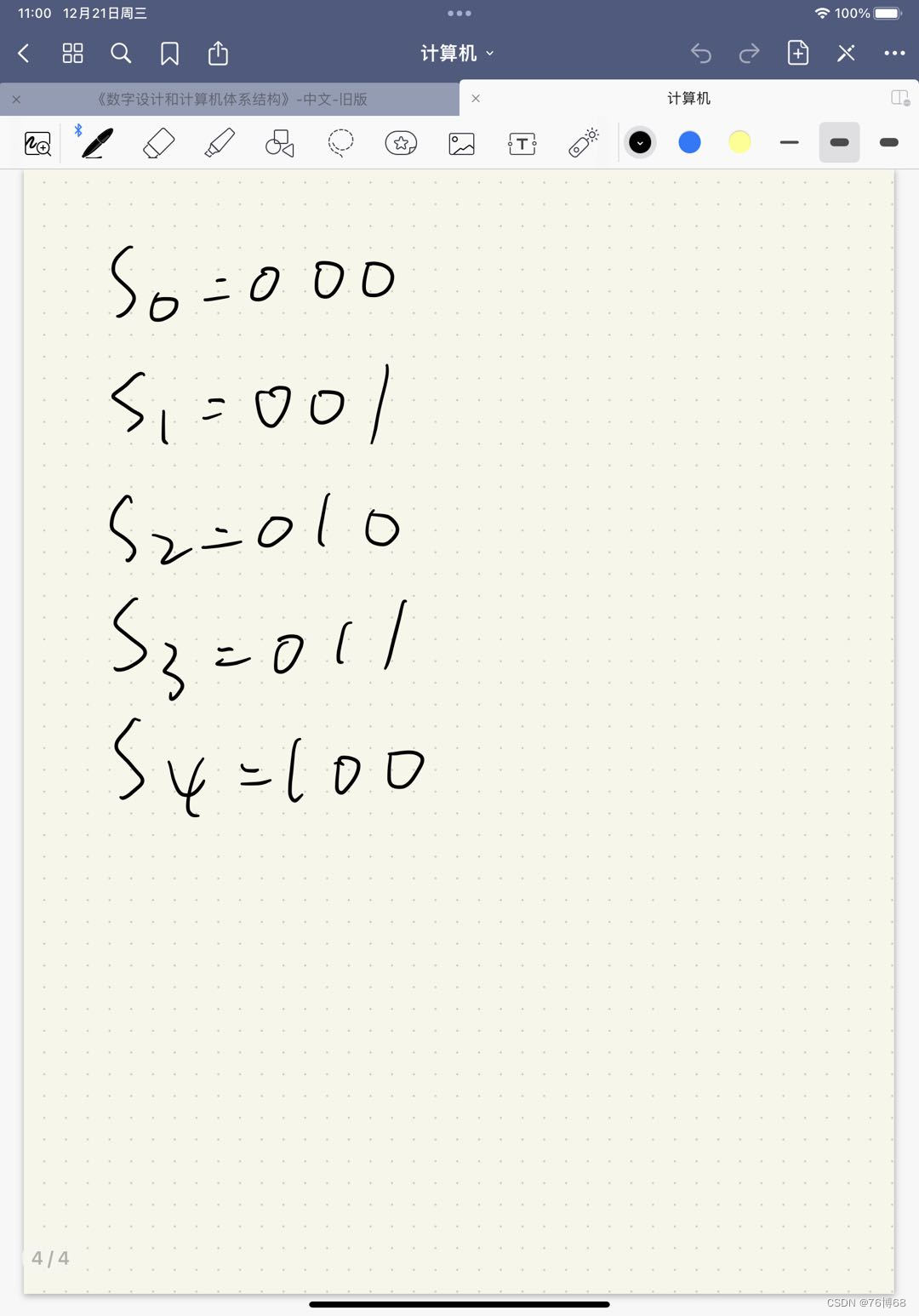

然后便是状态转换表,我们采用二进制编码重写状态转换表和输出表,这样使用的数位少一点。当然了,用独热编码也是OK的,因为有5个状态。独热编码需要5位数字,00001,00010,00100,01000,10000。数位太多了。

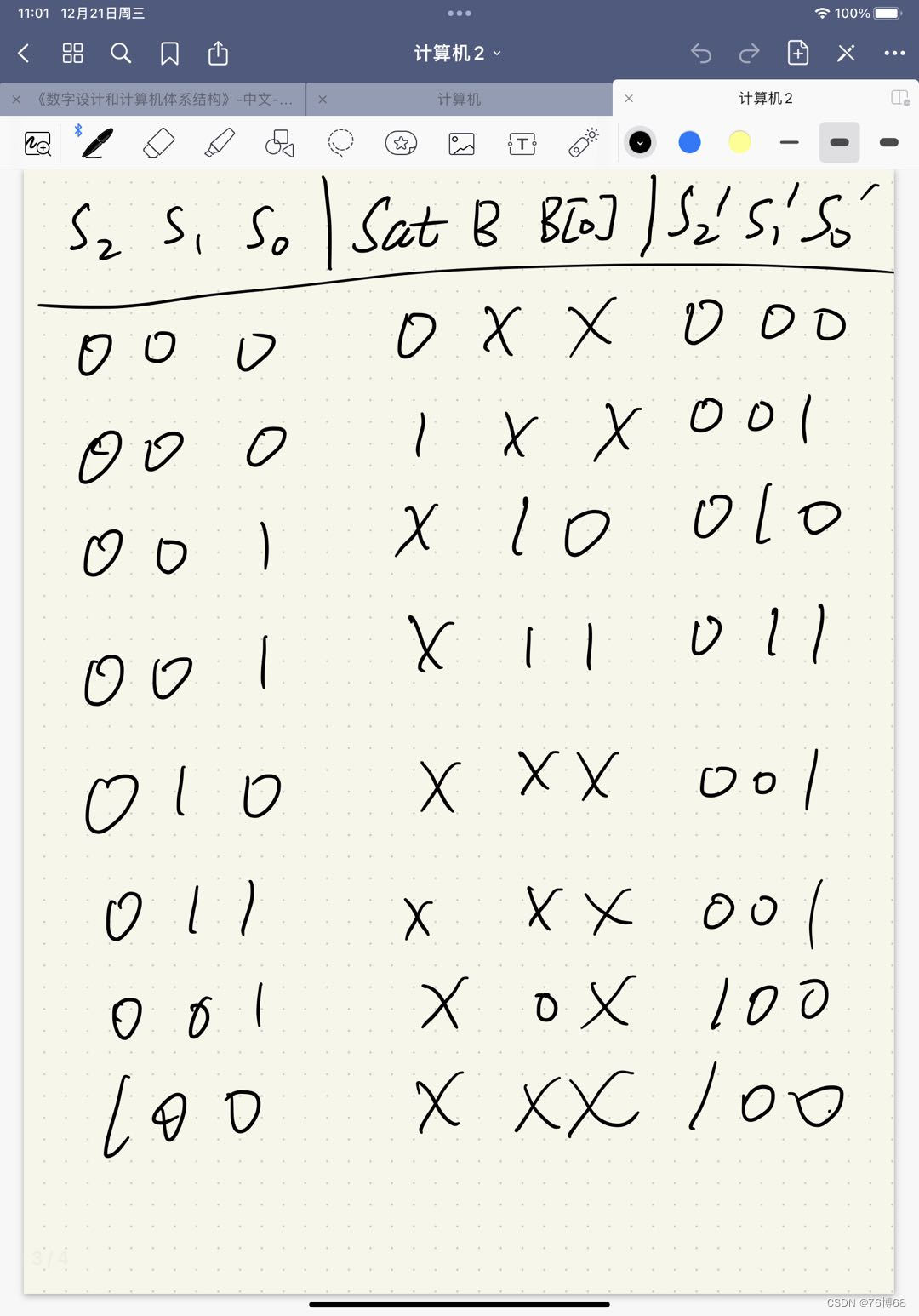

用二进制编码重写状态转换表:

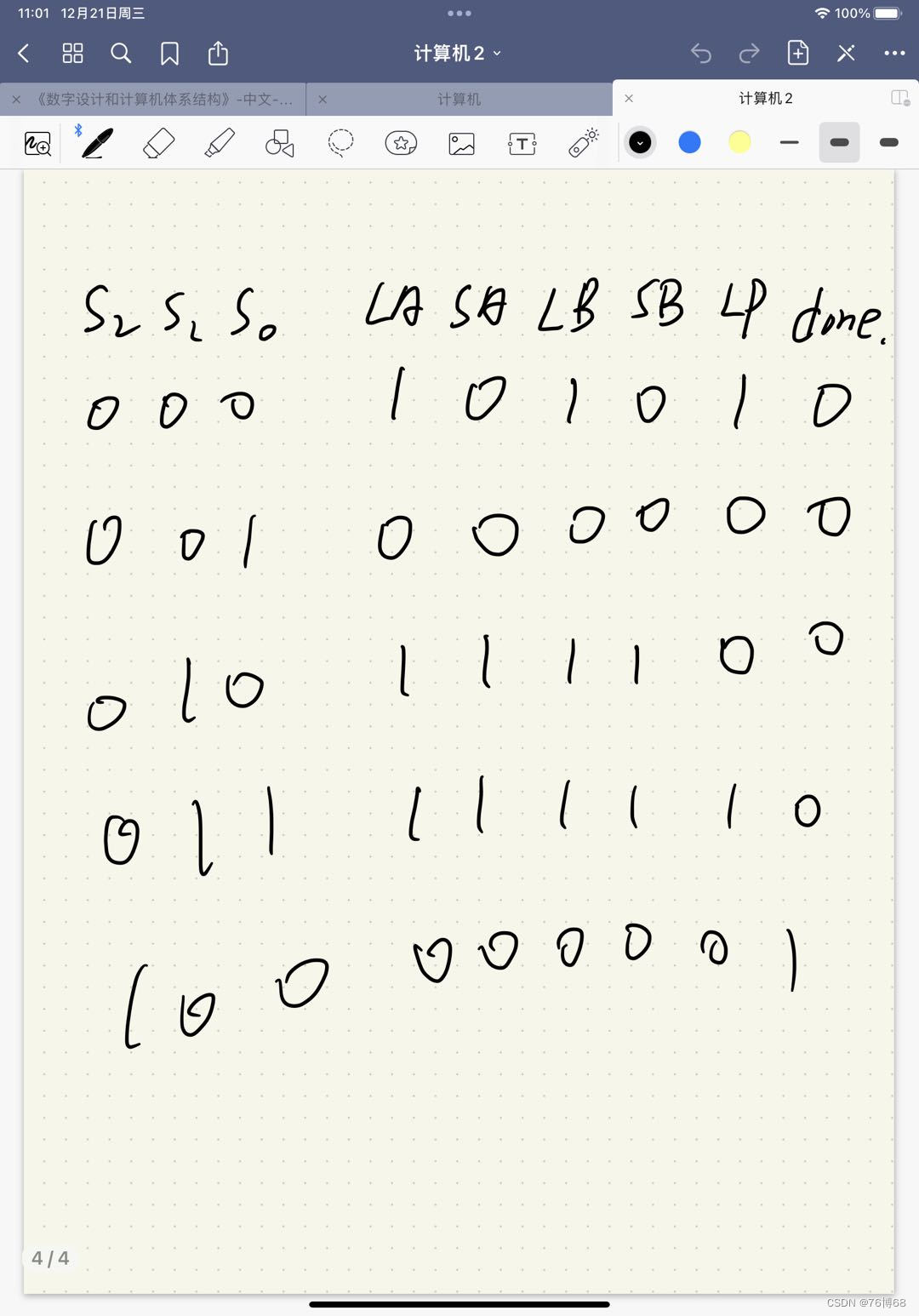

然后再写输出表:

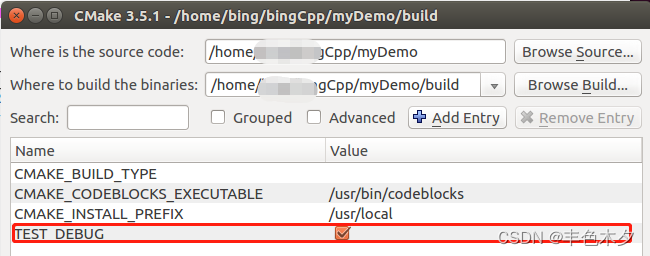

由于已经得到了二进制编码的状态转换表和输出表,接着用logisim自动生成电路按照这些表自动生成就好。

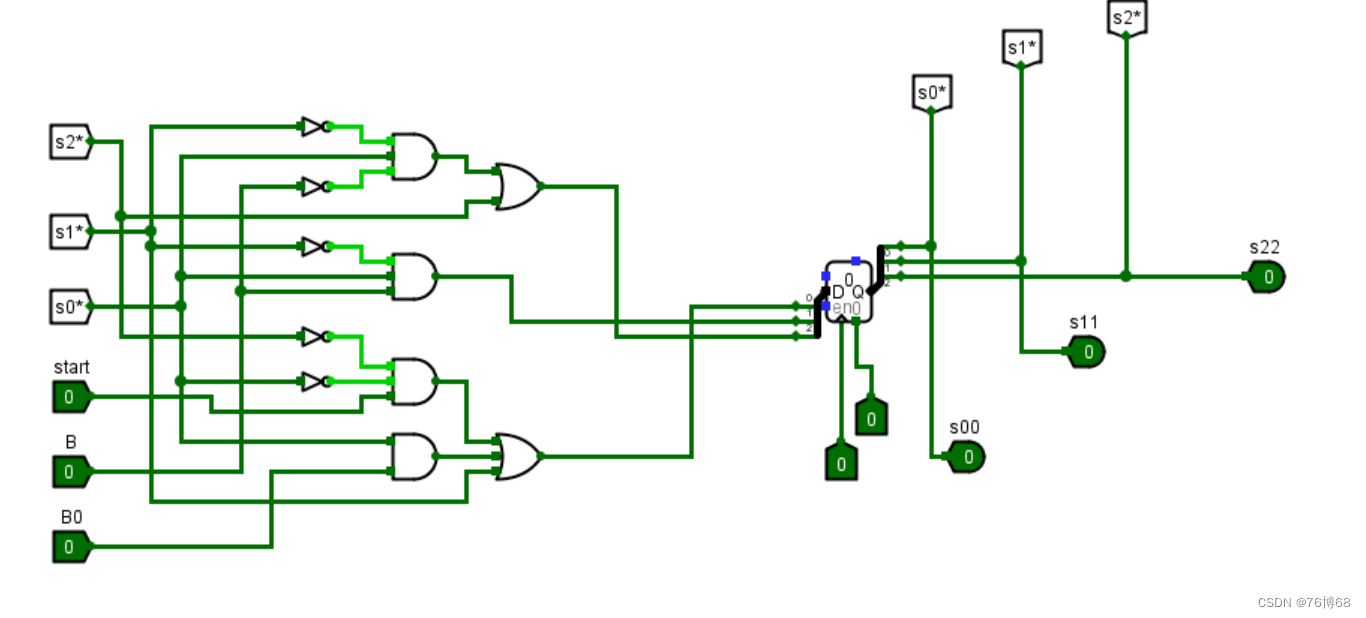

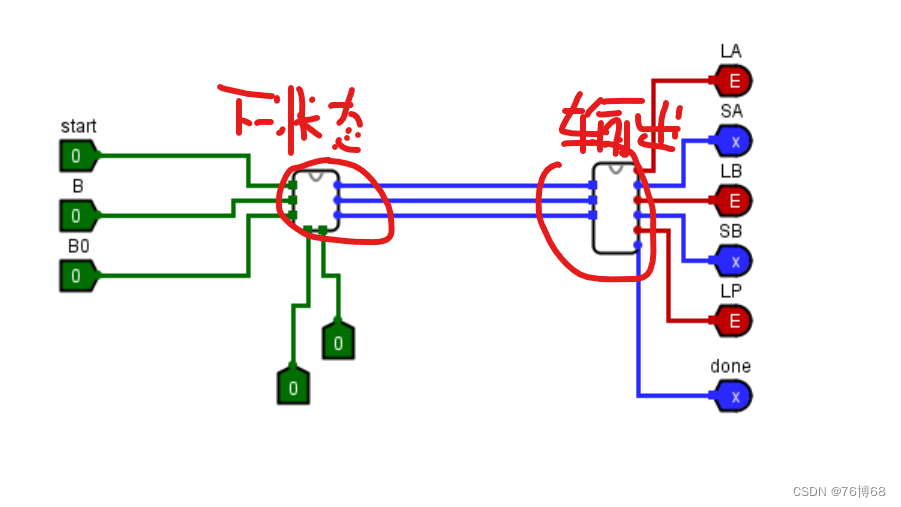

这是下一状态的电路图:

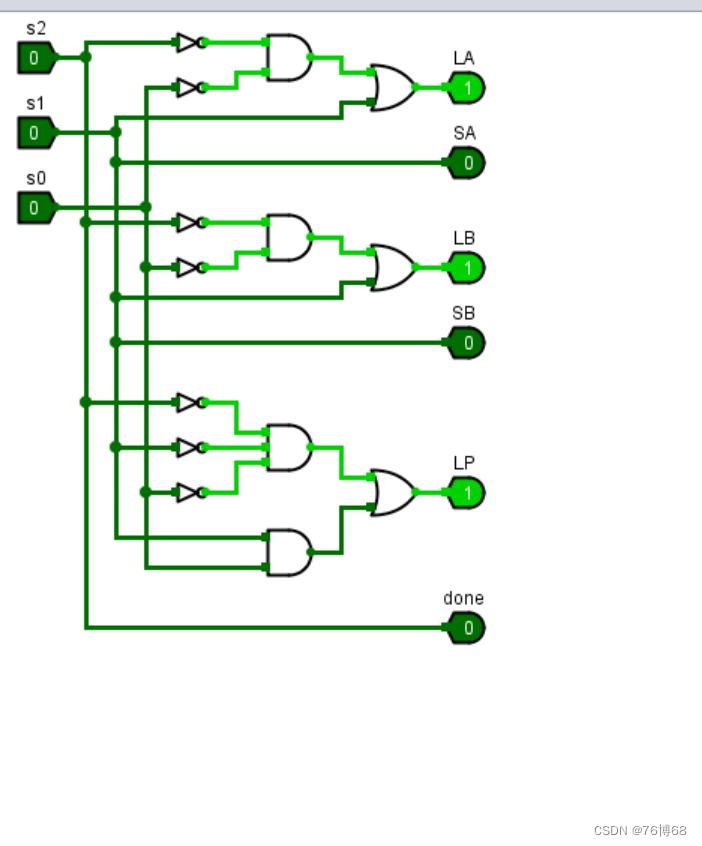

还有就是输出的电路图:

然后将这两个组合在一起就是有限状态机:

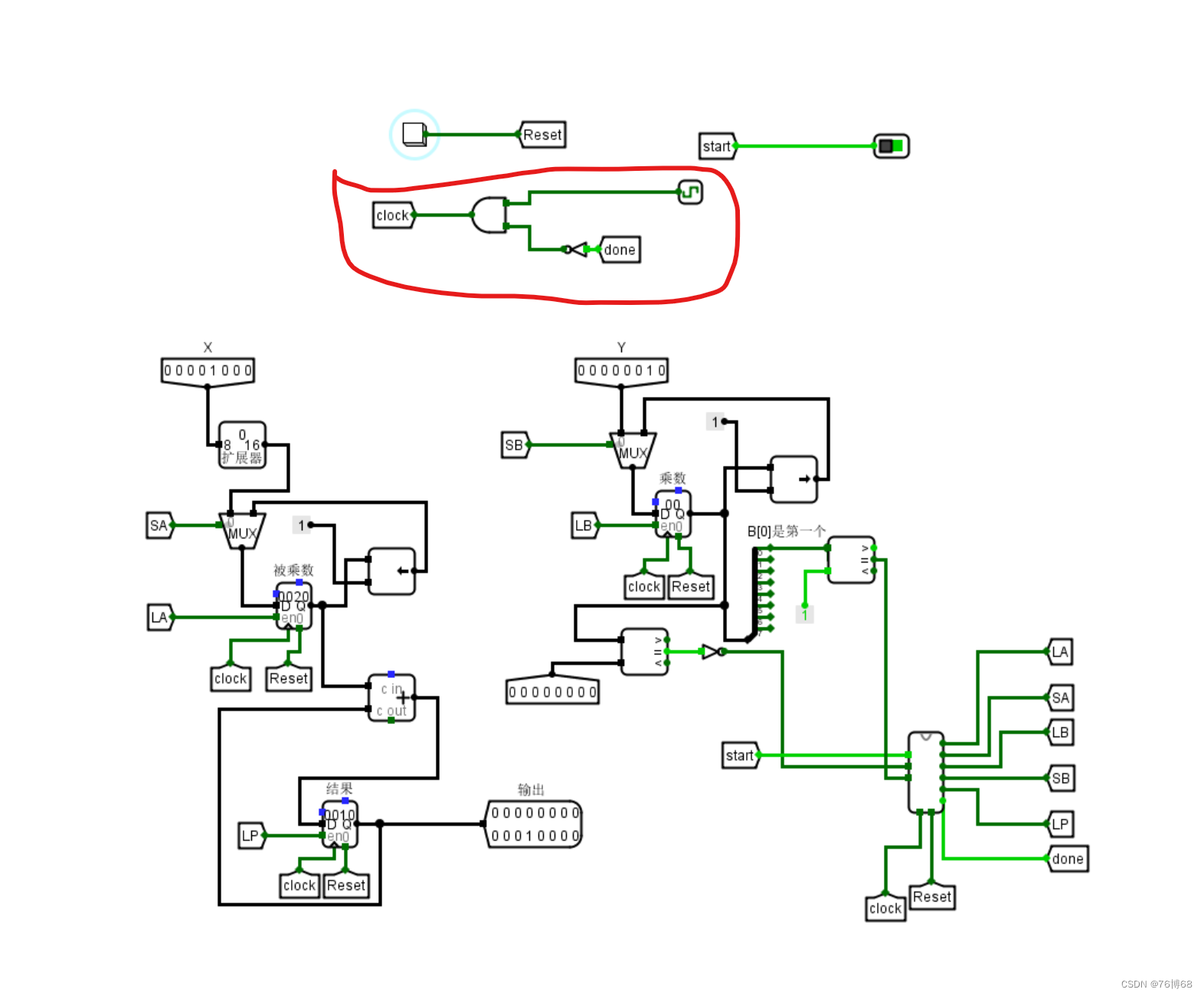

得到有限状态机控制电路后就可以开始组件全部的电路:

注意:当乘法器运行结束后的那个done信号出现之后他应该连到哪里去?这个done信号表明整个电路应该结束,所以我把它跟电路的时钟用与门连接起来,这样一来只要done信号出现,那么时钟将不再起作用,那么自然整个电路就停下来了。

运行的时候先输入运行的二进制数字,再点开start信号,最后再开时钟。

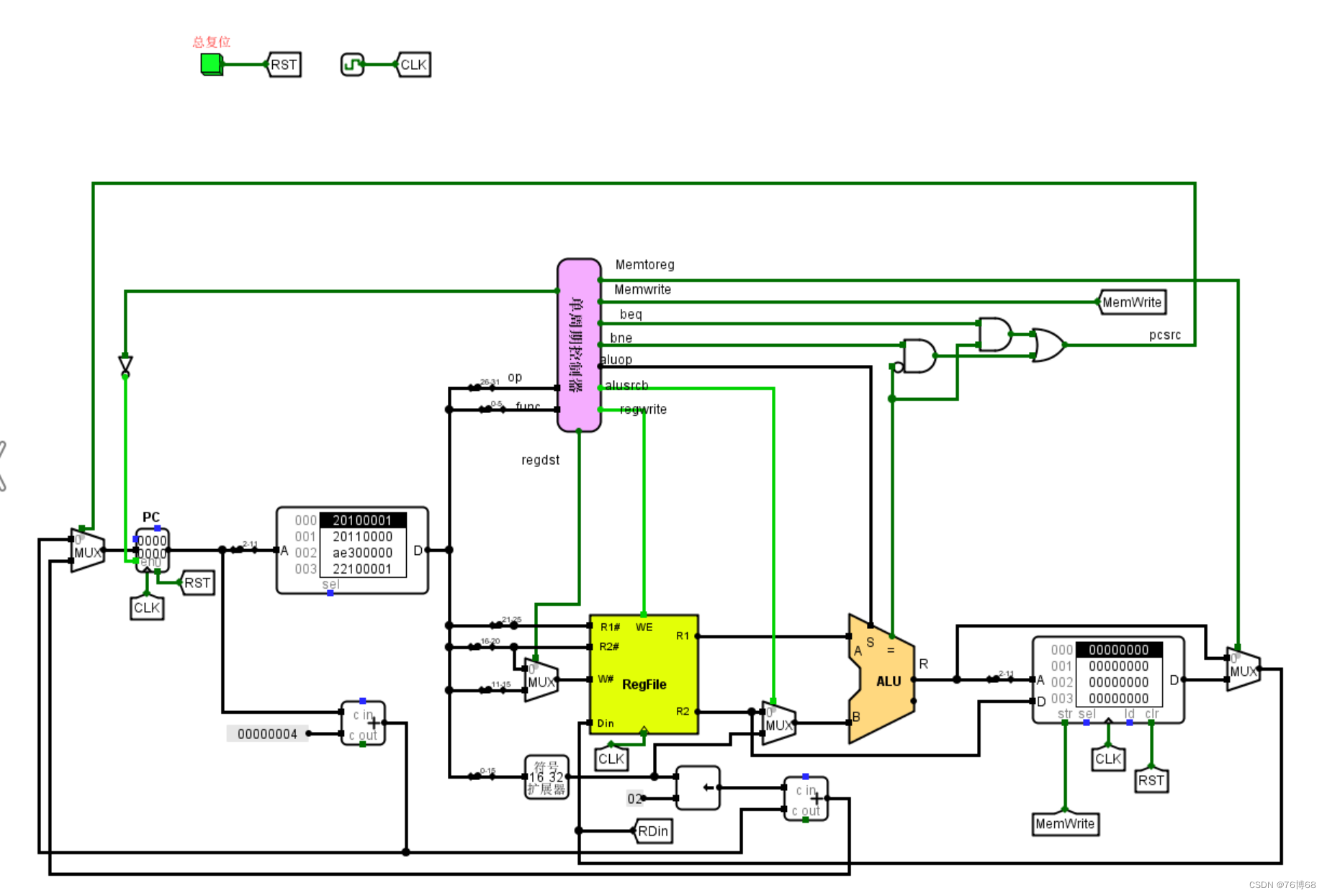

标题三:单周期MIPS CPU设计

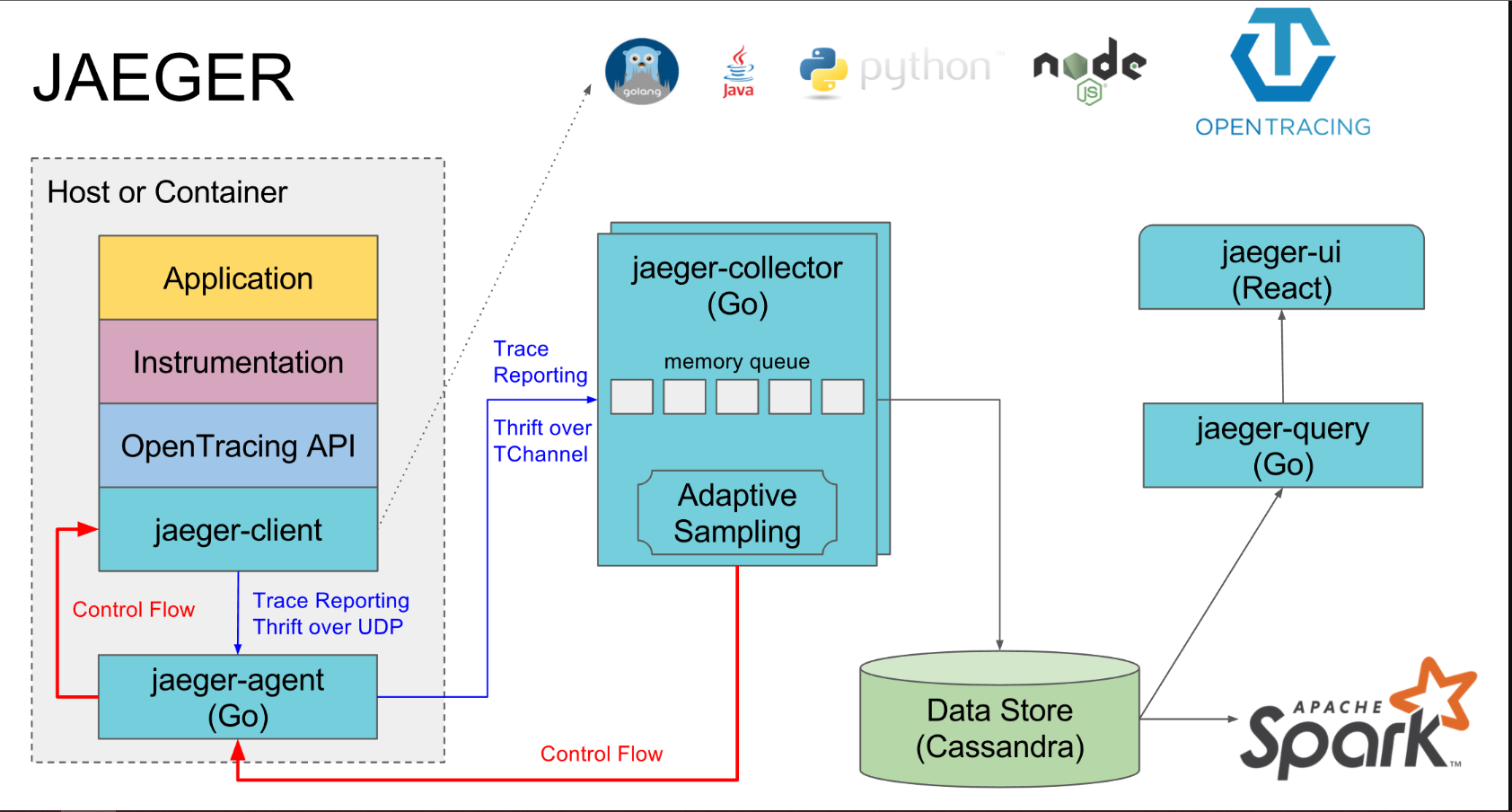

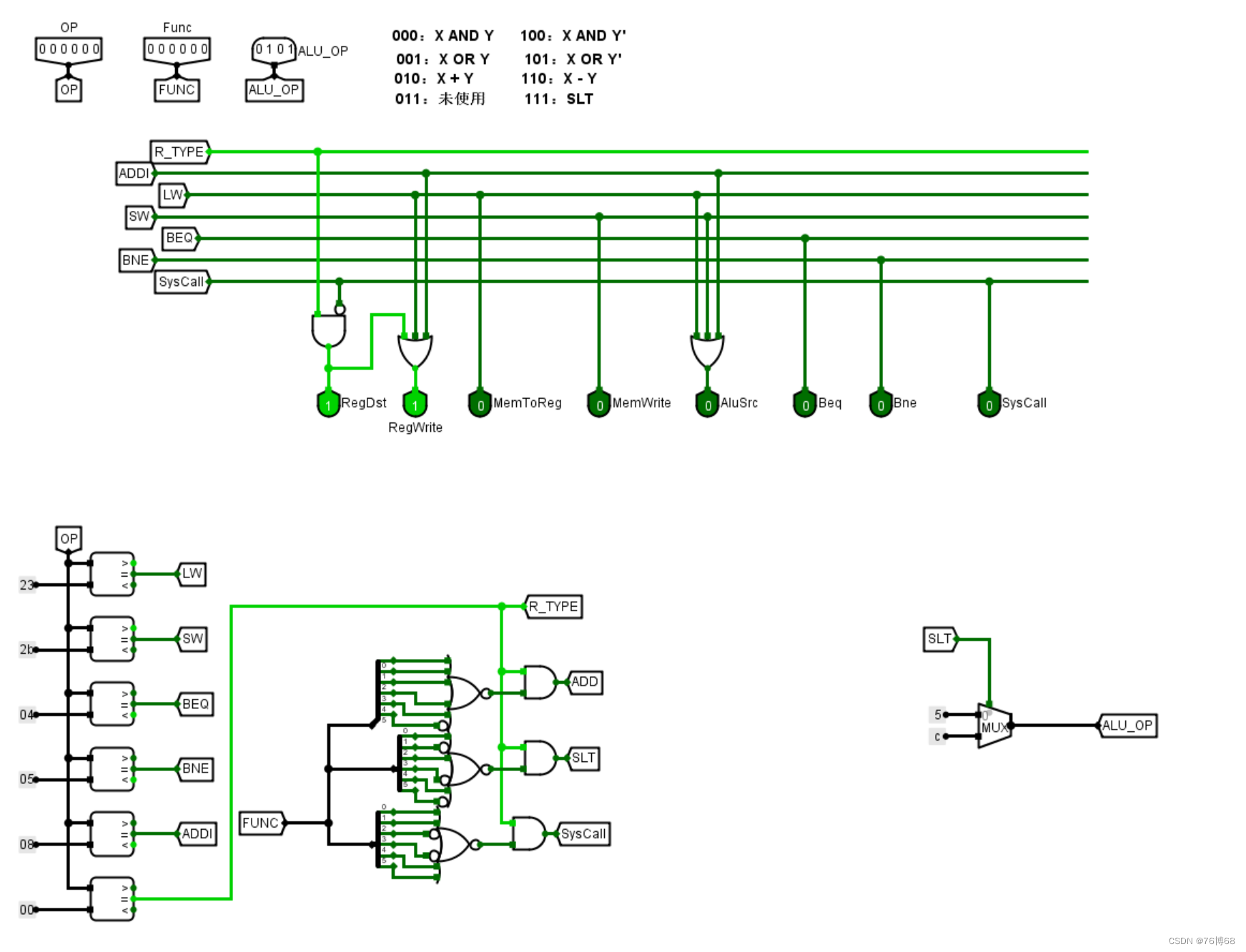

单周期控制器(也就是cpu控制器,起了另一个名字):设计:

接下来详细介绍控制器的实现:

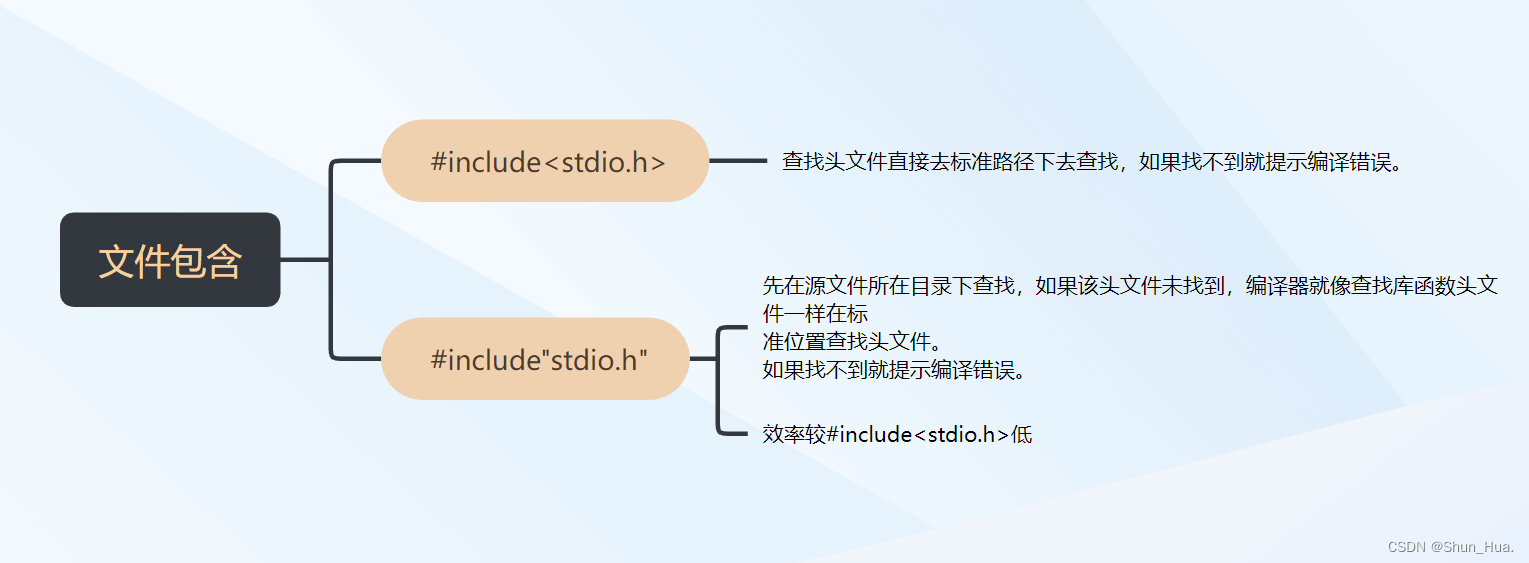

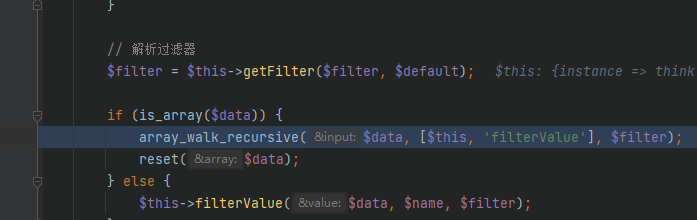

首先由于整个控制器是需要op以及func作为控制信号的指导,所以需要两个输入引脚将这两个信号输入,对于非R类型的指令而言,只需比较他的op是多少就那么这条指令就成立,比如lw的op指令是23(16进制),用一个比较器比较就可以得出。

而对于R类型的指令,由于R类型的数据的op都是000000,那么接下来就要看它的function,只需比较function就可以得出他们这几条指令,如图:

封装如下:

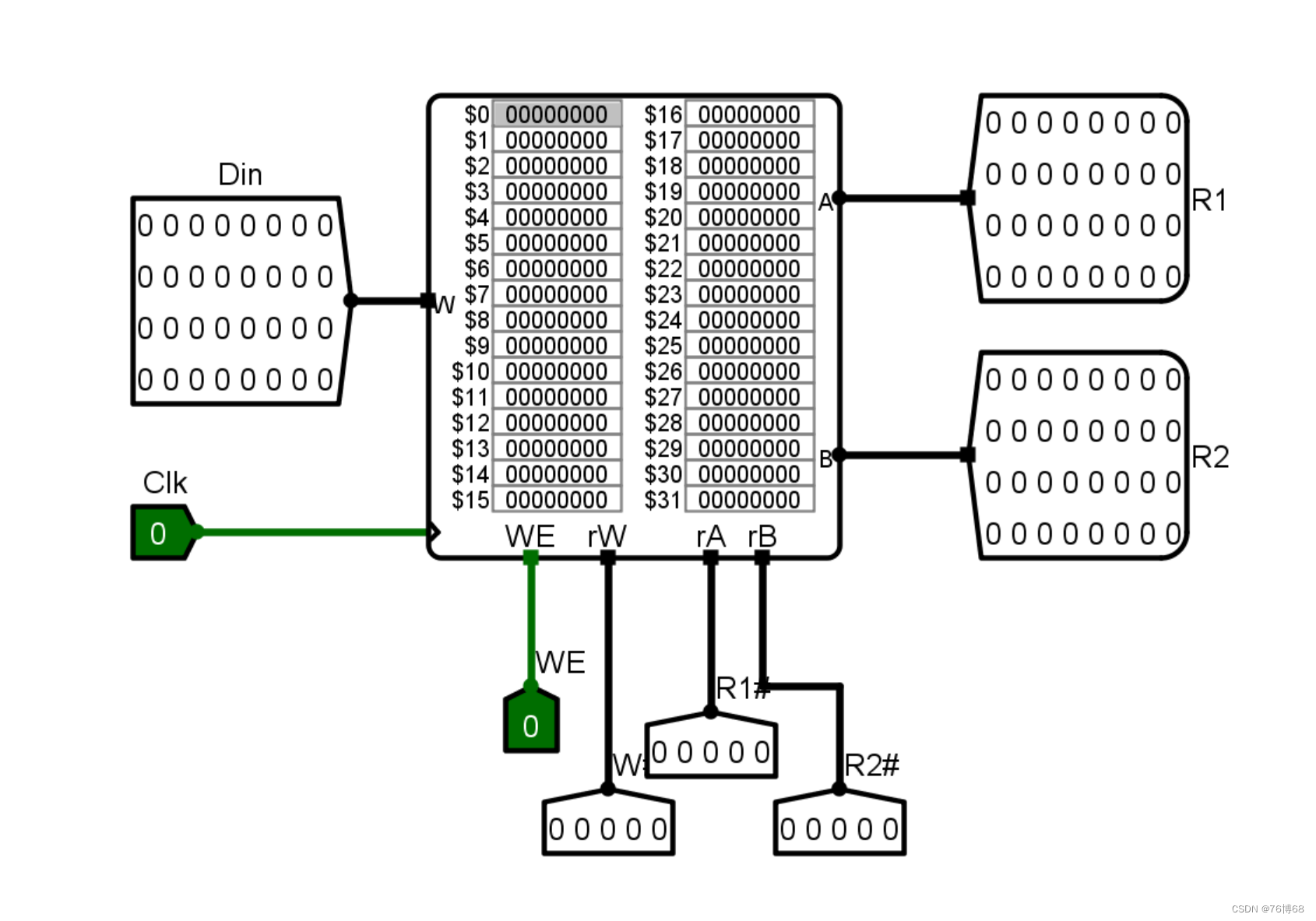

寄存器文件RegFile设计:

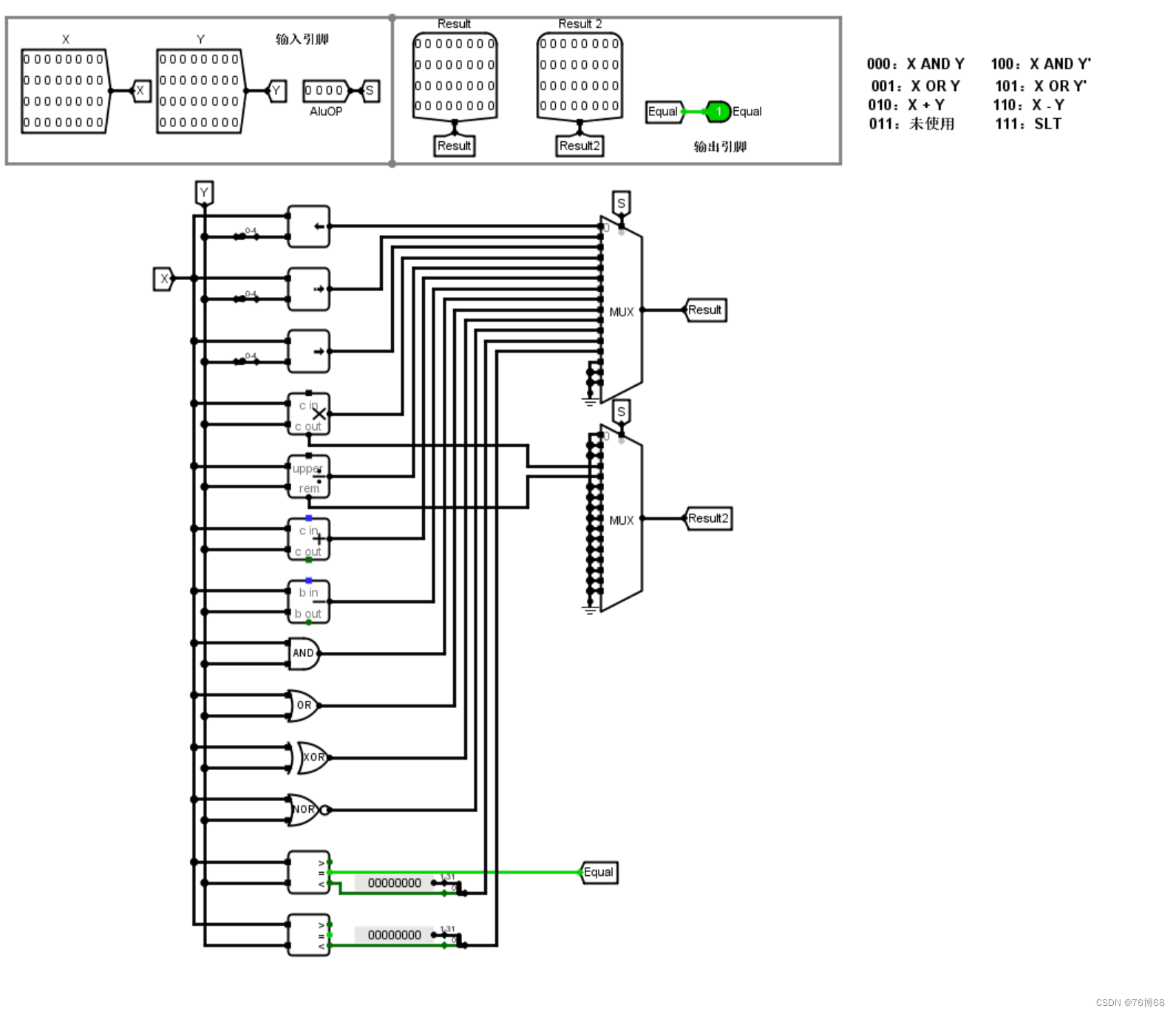

ALU设计:

总设计:

********************************************************************************************************

2023/1/24

正月初三,风轻轻吹.......