控制单元的功能

文章目录

- 控制单元的功能

- 9.1 微操作命令的分析

- 9.1.1 取指周期

- 9.1.2 间址周期

- 9.1.3 执行周期

- 9.1.4 中断周期

- 9.2 控制单元的功能

- 9.2.1 控制单元的外特性

- 9.2.2 控制信号举例

- 9.2.3 多级时序系统

- 9.2.4 控制方式

- 控制单元的设计

- 10.1 组合逻辑设计

- 10.1.1 组合逻辑控制单元框图

- 10.1.2 微操作的节拍安排

- 10.1.3 组合逻辑设计步骤

- 10.2 微程序设计

- 10.2.1 微程序设计思想的产生

- 10.2.2 微程序控制单元框图及工作原理

- 10.2.3 微指令的编码方式(控制方式)

- 10.2.4 微指令序列地址的形成

- 10.2.5 微指令格式

- 10.2.6 静态微程序设计和动态微程序设计

- 10.2.7 毫微程序设计

- 10.2.8 串行微程序控制和并行微程序控制

- 10.2.9 微程序设计举例

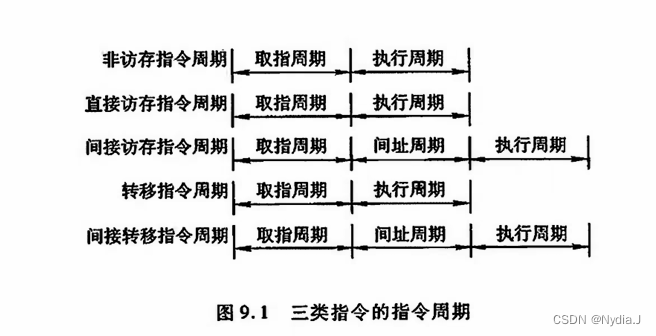

9.1 微操作命令的分析

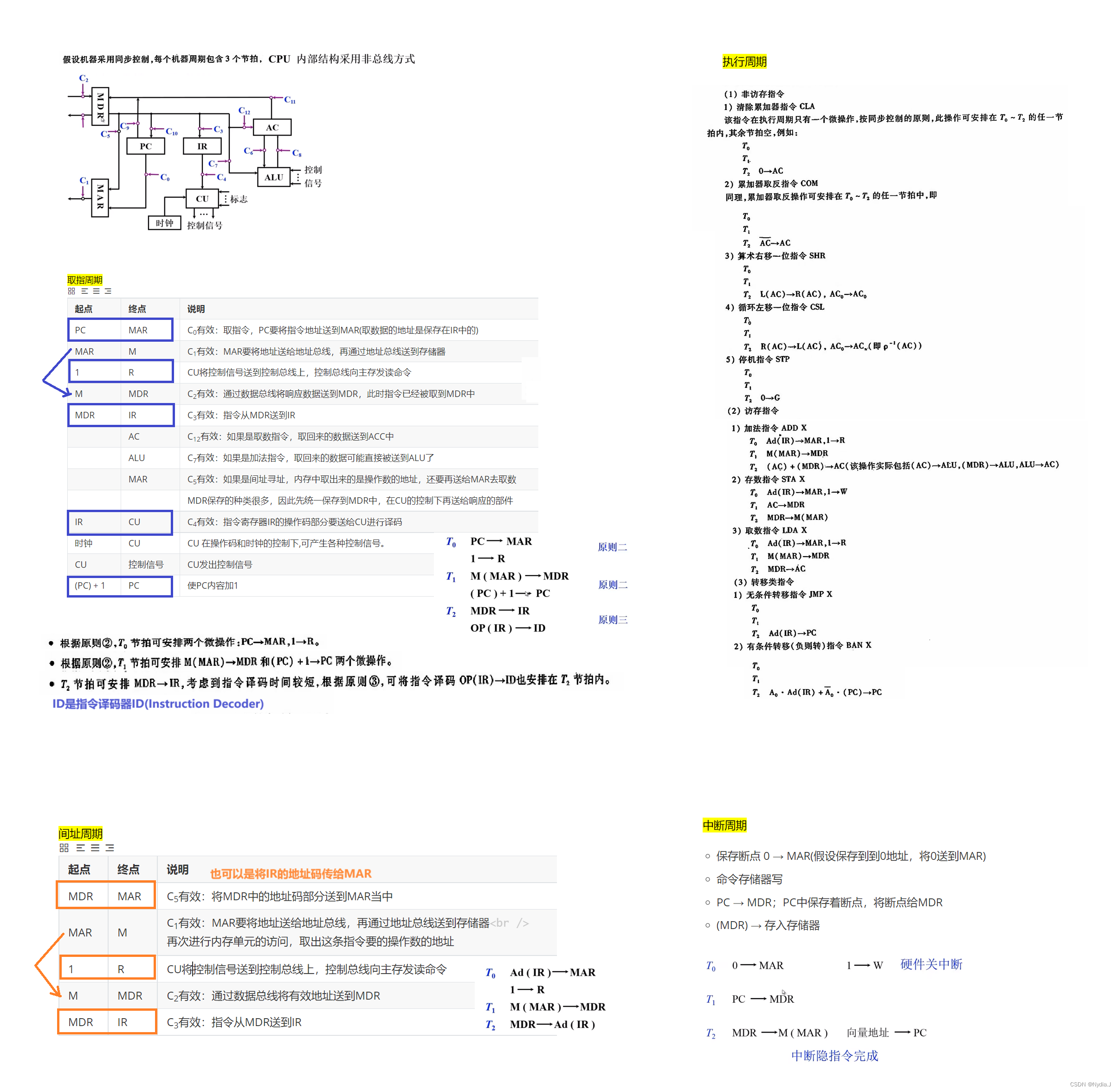

9.1.1 取指周期

9.1.2 间址周期

9.1.3 执行周期

-

非访存指令

指令 微操作 说明 CLA clear ACC,对ACC清零 0 → ACC COM 取反 ACC ‾ \overline{\text{ACC}} ACC → ACC SHR 算术右移,左边补上的是原来的符号位 L(ACC) → R(ACC), ACC0 → ACC0,就是将原来的符号位写回到最高位 CSL 循环左移 R(ACC) → L(ACC),ACC0 → ACCn STP 停机指令 0 → G,计算机有个停机标志,置0即停机 -

访存指令

指令 微操作 说明 ADD X 加法指令 将地址X中的数取出与ACC中相加再存入ACC中 Ad(IR) → MAR 操作数地址仍然是在IR中的,要将加数从内存取出 1 → R M(MAR) → MDR (ACC) + (MDR) → ACC STA X 存数指令 ACC中保存的数据存到内存单元给定的地址X中 Ad(IR) → MAR 将X的地址传给存储器 1 → W 写的指令传给主存 ACC → MDR MDR → M(MAR) LDA X 取数指令 X中的数据加载到ACC中 Ad(IR) → MAR 将X的地址传给存储器 1 → R M(MAR) → MDR MDR → ACC -

转移指令

指令 微操作 说明 JMP X —— 无条件转移 Ad(IR) → PC BAN X —— 条件转移 A0 ⋅ Ad(IR) + A0 ‾ \overline{\text{A0}} A0 ⋅ (PC) → PC 负则转,

如果上一条指令的结果是负数,

就跳转到X地址的指令,

上一条指令的运算结果是在ACC中的,

判断正负就看ACC的最高位A0 即可

9.1.4 中断周期

| 任务 | 微操作 | 说明 |

|---|---|---|

| 保存断点 | 0 → MAR(程序断点存入"0"地址) 或 (SP)−1 → MAR(程序断点进栈) | 保存断点就是将断点送入到内存单元中,有两种方式: 1. 程序断点存入"0"地址 2. 程序断点进栈 二者在操作上唯一的不同就是:断点保存的地址不同 |

| 1 → W | ||

| PC → MDR | 程序断点原在PC中的 | |

| MDR → M(MAR) | ||

| 形成中断服务程序入口地址 | (中断识别程序入口地址)M → PC | 软件查询法 |

| 向量地址 → PC | 硬件查询法 | |

| 关中断 | 0 → EINT | EINT置0,就关中断了 |

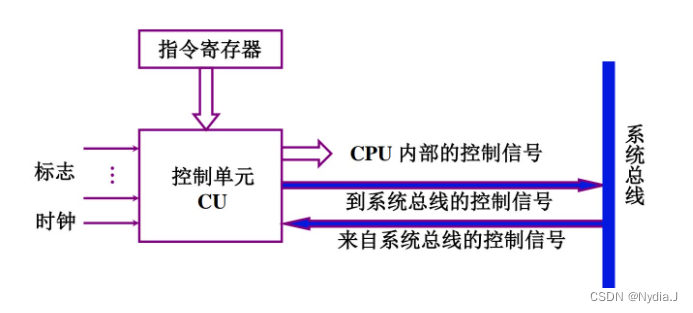

9.2 控制单元的功能

9.2.1 控制单元的外特性

-

输入信号

输入信号 说明 指令寄存器 OP(IR) → CU,IR保存了要执行的那条指令,将指令的操作码送到CU进行译码,指出指令要做的操作,控制信号与操作码有关 时钟 为了使控制单元按一定的先后顺序、一定的节奏发出各个控制信号,控制单元必须受时钟控制,即每一个时钟脉冲使控制单元发送一个操作命令,或发送一组需要同时执行的操作命今 标志 控制单元有时需依赖CPU当前所处的状态(如ALU操作的结果)产生控制信号

如BAN指令,控制单元要根据上条指令的结果是否为负而产生不同的控制信号;

再如条件转移指令所需要判断的条件就是标志外来信号 (来自系统总线(控制总线)的控制信号)

来自CPU外部的信号也会进入CU,以便CU对整个系统的硬件资源发出命令,进行管理。比如INTR中断请求,HRQ总线请求 -

输出信号

输出信号 指令举例 说明 CPU内部的各种控制信号,控制CPU内部的部件做相应的操作 Ri → Rj 寄存器之间的数据传输 (PC)+1 → PC 更新PC指令 ALU 算术运算(加、减)、逻辑运算(与、或) CPU内部运算器执行的操作 送至控制总线的信号,控制IO、总选、存储体的信号 MREQ ‾ \overline{\text{MREQ}} MREQ 访问存储体控制信号 IO ‾ \overline{\text{IO}} IO/M 访IO/存储体的控制信号,低电平是IO,高电平是存储体 RD 存储器读命令 WR 存储器写命令 INTA 中断响应信号,CPU发出,响应中断源的中断请求 HLDA 总线应答信号,响应外设发出的总线使用请求

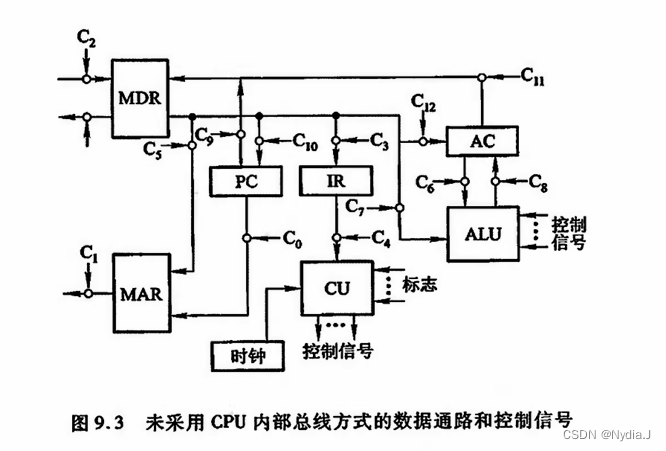

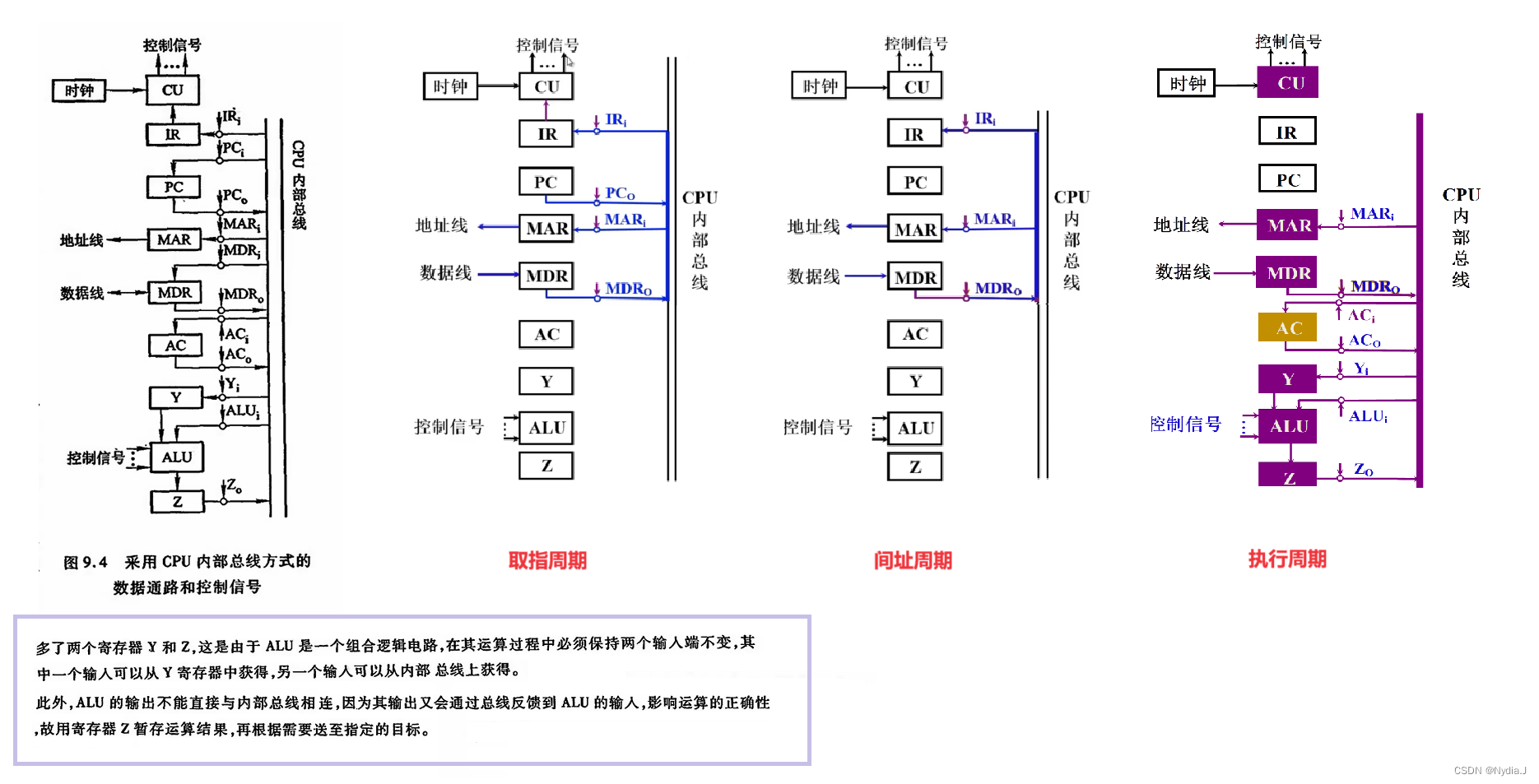

9.2.2 控制信号举例

-

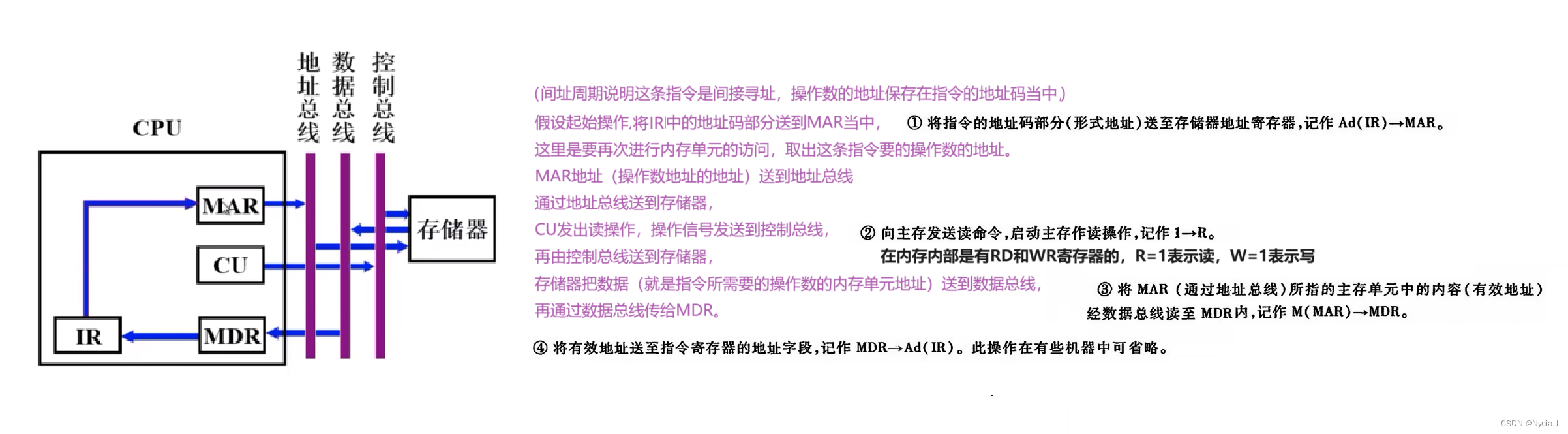

不采用 CPU 内部总线的方式

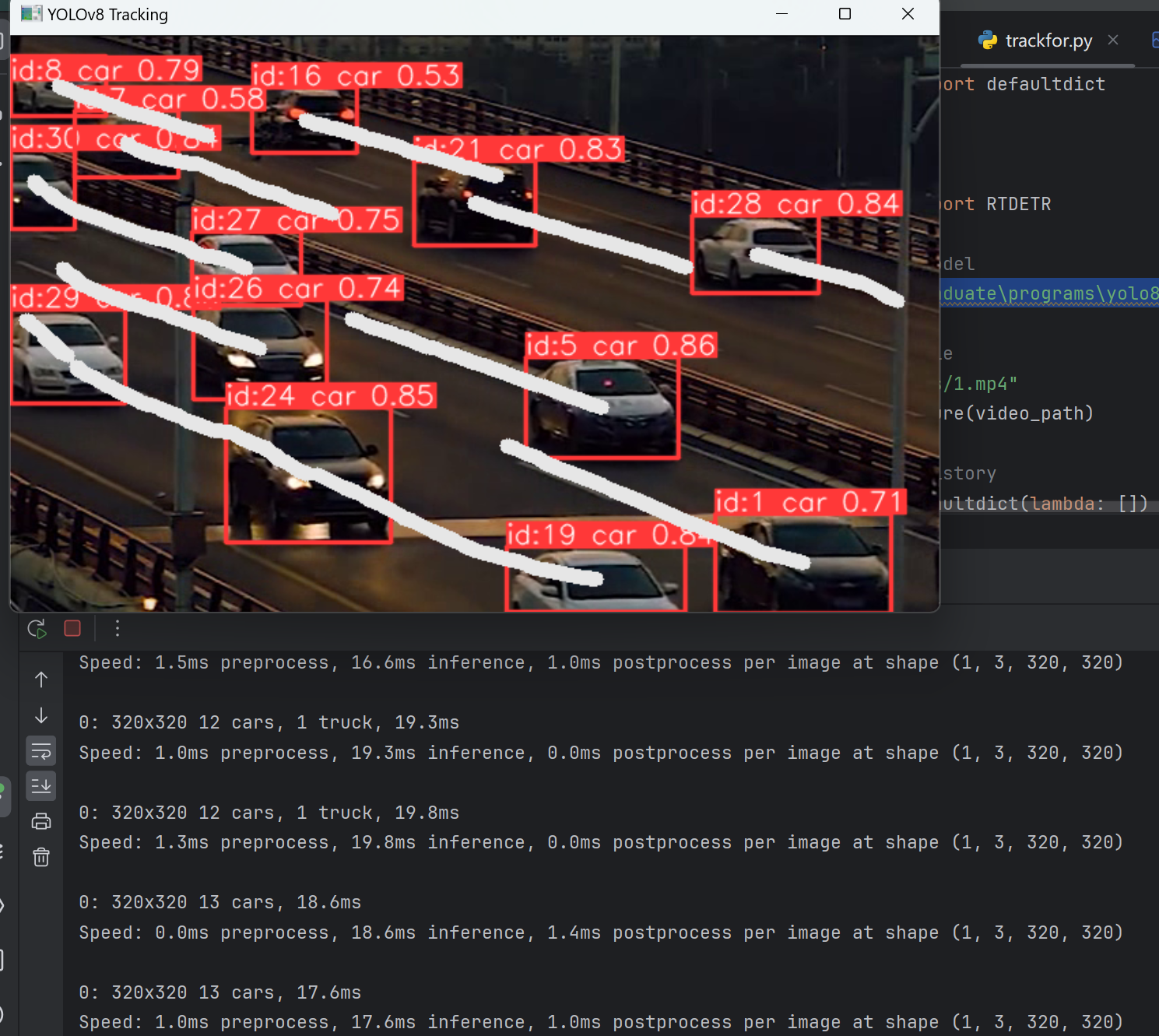

以ADD @X为例

取指周期

起点 终点 说明 PC MAR C0有效:取指令,PC要将指令地址送到MAR(取数据的地址是保存在IR中的) MAR M C1有效:MAR要将地址送给地址总线,再通过地址总线送到存储器 1 R CU将控制信号送到控制总线上,控制总线向主存发读命令 M MDR C2有效:通过数据总线将响应数据送到MDR,此时指令已经被取到MDR中 MDR IR C3有效:指令从MDR送到IR AC C12有效:如果是取数指令,取回来的数据送到ACC中 ALU C7有效:如果是加法指令,取回来的数据可能直接被送到ALU了 MAR C5有效:如果是间址寻址,内存中取出来的是操作数的地址,还要再送给MAR去取数 MDR保存的种类很多,因此先统一保存到MDR中,在CU的控制下再送给响应的部件 IR CU C4有效:指令寄存器IR的操作码部分要送给CU进行译码 时钟 CU CU 在操作码和时钟的控制下,可产生各种控制信号。 CU 控制信号 CU发出控制信号 (PC) + 1 PC 使PC内容加1 间址周期

起点 终点 说明 MDR MAR C5有效:将MDR中的地址码部分送到MAR当中 MAR M C1有效:MAR要将地址送给地址总线,再通过地址总线送到存储器

再次进行内存单元的访问,取出这条指令要的操作数的地址1 R CU将控制信号送到控制总线上,控制总线向主存发读命令 M MDR C2有效:通过数据总线将有效地址送到MDR MDR IR C3有效:指令从MDR送到IR 执行周期

起点 终点 说明 MDR MAR C5有效:将MDR中的地址码部分送到MAR当中 MAR M C1有效:MAR要将地址送给地址总线,再通过地址总线送到存储器 1 R CU将控制信号送到控制总线上,控制总线向主存发读命令 M MDR C2有效:通过数据总线将操作数送到MDR(此时加数在MDR,被加数在AC) 控制信号 ALU C6、C7同时有效:通过CPU内部控制总线对ALU发“ADD”加控制信号,完成AC的内容和MDR的内容相加。 (AC) + (MDR) AC C8同时有效:将求和结果存入 AC。 C9和C10分别是控制PC的输出和输人的控制信号,

C11和C12分别是控制AC的输出和输入的控制信号。 -

采用 CPU 内部总线方式

以ADD @X为例

取指周期

起点 终点 说明 PC MAR PCo和MARi有效:PC的值经由CPU内部总线送到MAR(保存的是下一条要执行的指令地址) MAR 地址线 MAR把地址送到地址线 1 R CU发出读命令,读命令是通过控制线送到存储器 数据线 MDR 读出来的指令通过数据线送到MDR(保存的是取回来的间接寻址的加法值) MDR IR MDRo和IRi有效:在控制信号的控制之下输出到CPU内部总线,通过总线输入到IR中

IR就保存了要执行的加法指令OP(IR) CU 指令寄存器IR的操作码部分要送给CU进行译码 (PC) + 1 PC 使PC内容加1 间址周期

起点 终点 说明 MDR MAR MDRo和MARi有效:MDR通过CPU的内部总线将形式地址送入到MAR中 MAR 地址线 MAR将地址送到地址线 1 R CU发出读命令,读命令是通过控制线送到存储器 数据线 MDR 读出的内容(有效地址)经过数据线送入到MDR中 MDR IR MDRo和IRi有效:MDR通过CPU的内部总线将有效地址送入到IR中 执行周期

起点 终点 说明 MDR MAR MDRo和MARi有效:MDR通过CPU的内部总线将操作数的地址送入到MAR中 MAR 地址线 MAR将地址送到地址线 1 R CU发出读命令,读命令是通过控制线送到存储器 数据线 MDR 读出的内容(操作数)经过数据线送入到MDR中 MDR Y MDRo和Yi有效:MDR通过CPU的内部总线将操作数送入到Y寄存器中 Y ALU Y中操作数送到ALU,另一个操作数在AC中 AC ALU ACo和ALUi有效:AC中操作数经由CPU内部总线送到ALU中 (AC) + (Y) Z 加法结果保存到Z中 Z AC Zo和ACi有效:加法结果经由CPU内部总线送到AC中

9.2.3 多级时序系统

-

机器周期

-

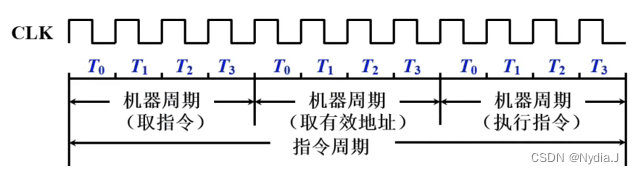

概念:所有指令执行过程中的一个基准时间

-

确定机器周期需考虑的因素:每条指令的执行步骤,每一步骤所需的时间,将每个步骤划分到不同机器周期中

-

基准时间的确定:

-

通常情况下:

在指令执行的过程中(取指、间址、执行、中断)以完成最复杂指令功能的微操作的时间为准

实际上,最复杂的通常都是是访存操作,因此,以访问一次存储器的时间为基准若指令字长 = 存储字长,取指周期 = 机器周期

-

-

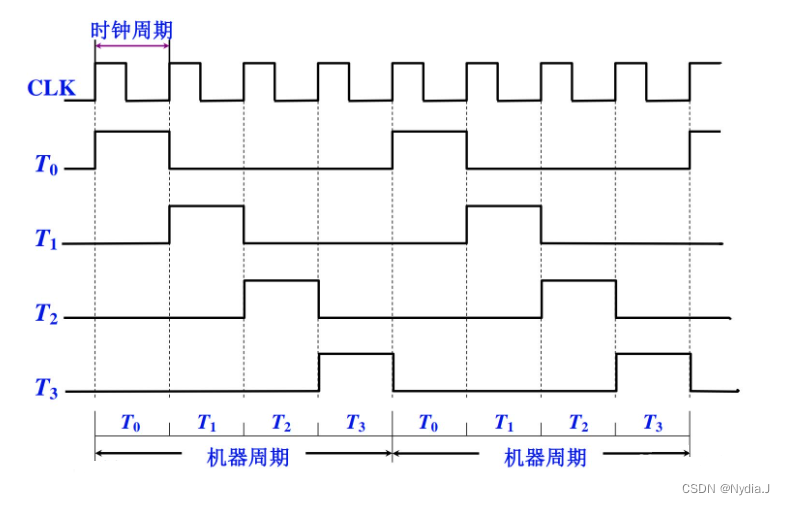

时钟周期

-

一个机器周期内可完成若干个微操作,每个微操作需一定的时间,有些微操作在一个时钟周期内完成,有些微操作可能花费多个时钟周期(比如对内存的访问)

将一个机器周期分成若干个时间相等的时间段(节拍、状态、时钟周期),由时钟周期控制在一个机器周期内部微操作的先后顺序。 -

时钟周期是控制计算机操作的最小单位时间。用时钟周期控制产生一个或几个微操作命令(控制几个微操作命令的情况一般是指这些微操作可以并行执行)

-

-

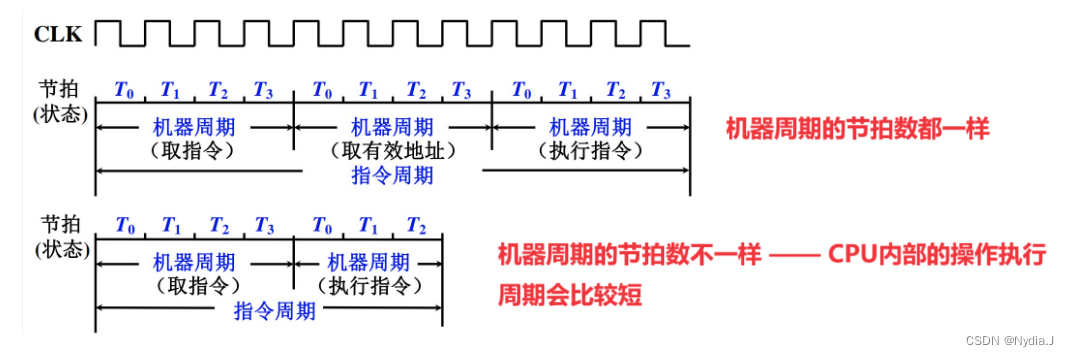

多级时序系统

-

机器周期、节拍(状态)组成多级时序系统;

-

一个指令周期包含若干个机器周期、一个机器周期包含若干个时钟周期。

-

机器速度与机器主频的关系

-

机器速度不仅与主频有关 ,还与一个机器周期中所含时钟周期(主频的倒数)数以及指令周期中所含的机器周期数有关。

即使这两个一样,一台采用流水,一台采用非流水,结果也是不一样的。 -

假设两台机器都采用非流水方式,并且在一个指令周期当中,包含的机器周期的数量是相同的 ,在机器周期所含节拍数也相同的,那么两机平均指令执行速度之比就等于两机主频之比

M I P S 1 M I P S 2 = f 1 f 2 \frac{MIPS_1}{MIPS_2} = \frac{f_1}{f_2} MIPS2MIPS1=f2f1

-

9.2.4 控制方式

产生不同微操作命令序列所用的时序控制方式

-

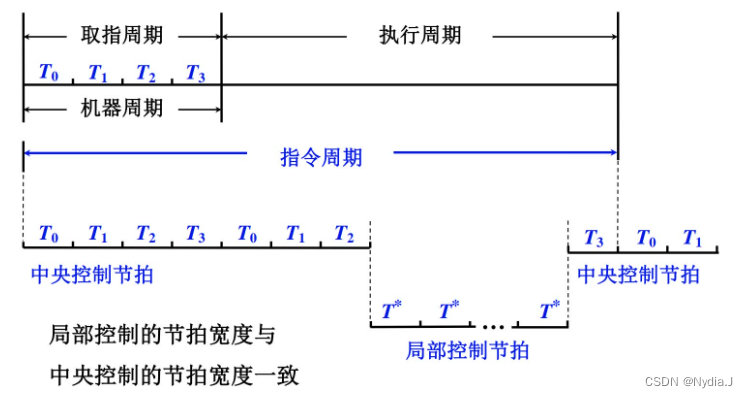

同步控制方式 - 任何一条指令或指令中任何一个微操作的执行都是事先确定的,并且都是受统一基准时标的时序信号所控制的方式。(一定有一个统一的,定宽定距的时钟作为标准,每一个微操作都是在这个时钟的控制下,在指定的节拍产生。)

-

采用定长的机器周期

每个机器周期含有相同数量的节拍数,这个时候机器周期以最长的微操作序列和最复杂的微操作作为标准。可能会在某些执行阶段造成时间浪费。 -

采用不定长的机器周期

每个机器周期内的节拍数可以不等,这种控制方式可解决微操作执行时间不统一的问题。 通常把大多数微操作安排在一个较短的机器周期内完成,而对某些复杂的微操作,采用延长机器周期或增加节拍的办法来解决。 -

采用中央控制和局部控制相结合的方法

将机器的大部分指令安排在统一的、较短的机器周期内完成,称为中央控制,而将少数操作复杂的指令中的某些操作(如乘除法和浮点运算等)采用局部控制方式来完成

-

-

异步控制方式

- 无基准时标信号

- 无固定的周期节拍和严格的时钟同步

- 采用 应答方式

- 当CU发出执行某一微操作的控制信号后,等待执行部件完成了该操作后发回“回答”(或“结束”)信号,再开始新的微操作,使CPU没有空闲状态,但因需要采用各种应答电路,故其结构比同步控制方式复杂

-

联合控制方式

- 同步控制和异步控制相结合。这种方式对各种不同指令的微操作实行大部分统一、小部分区别对待的办法。

- 对每条指令都有的取指令操作,采用同步方式控制;

对那些时间难以确定的微操作,如 I/O操作,则采用异步控制,

以执行部件送回的“回答"信号作为本次微操作的结束。

-

人工控制方式

为了调机和软件开发的需要,在机器面板或内部设置一些开关或按键,来达到,工控制的目的。

(1) Reset(复位)键

按下 Reset 键,使计算机处于初始状态。当机器出现死锁状态或无法继续运行时,可按此键。若在机器运行时按此键,将会破坏机器内某些状态而引起错误,因此要慎用。有些微型计算机未设此键,当机器死锁时,可采用停电后再加电的办法重新启动计算机。

(2) 连续或单条执行转换开关

由于调机的需要,有时需要观察执行完一条指令后的机器状态,有时又需要观察连续运行程序后的结果,设置连续或单条执行转换开关,能为用户提供这两种选择。 (3) 符合停机开关

这组开关指示存储器的位置,当程序运行到与开关指示的地址相符时,机器便停止运行,称为符合停机。

控制单元的设计

10.1 组合逻辑设计

10.1.1 组合逻辑控制单元框图

10.1.2 微操作的节拍安排

- 安排微操作时序的原则

- ① 原则一 微操作的先后顺序不得随意更改

- ② 原则二 被控对象不同 的微操作尽量安排在一个节拍内完成(可以并行操作且没有先后顺序的微操作)

- ③ 原则三 占用 时间较短 的微操作尽量安排在一个节拍内完成 并允许有先后顺序

10.1.3 组合逻辑设计步骤

10.2 微程序设计

10.2.1 微程序设计思想的产生

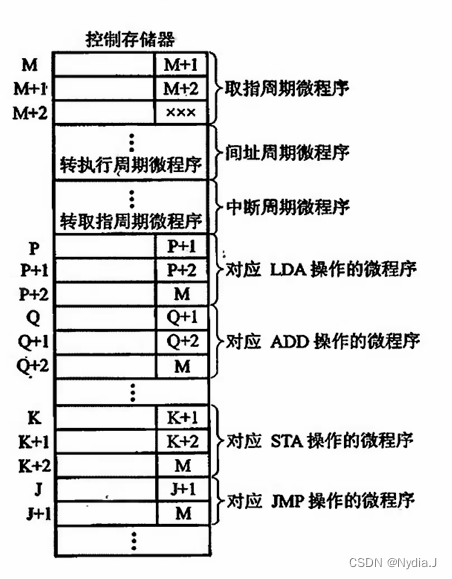

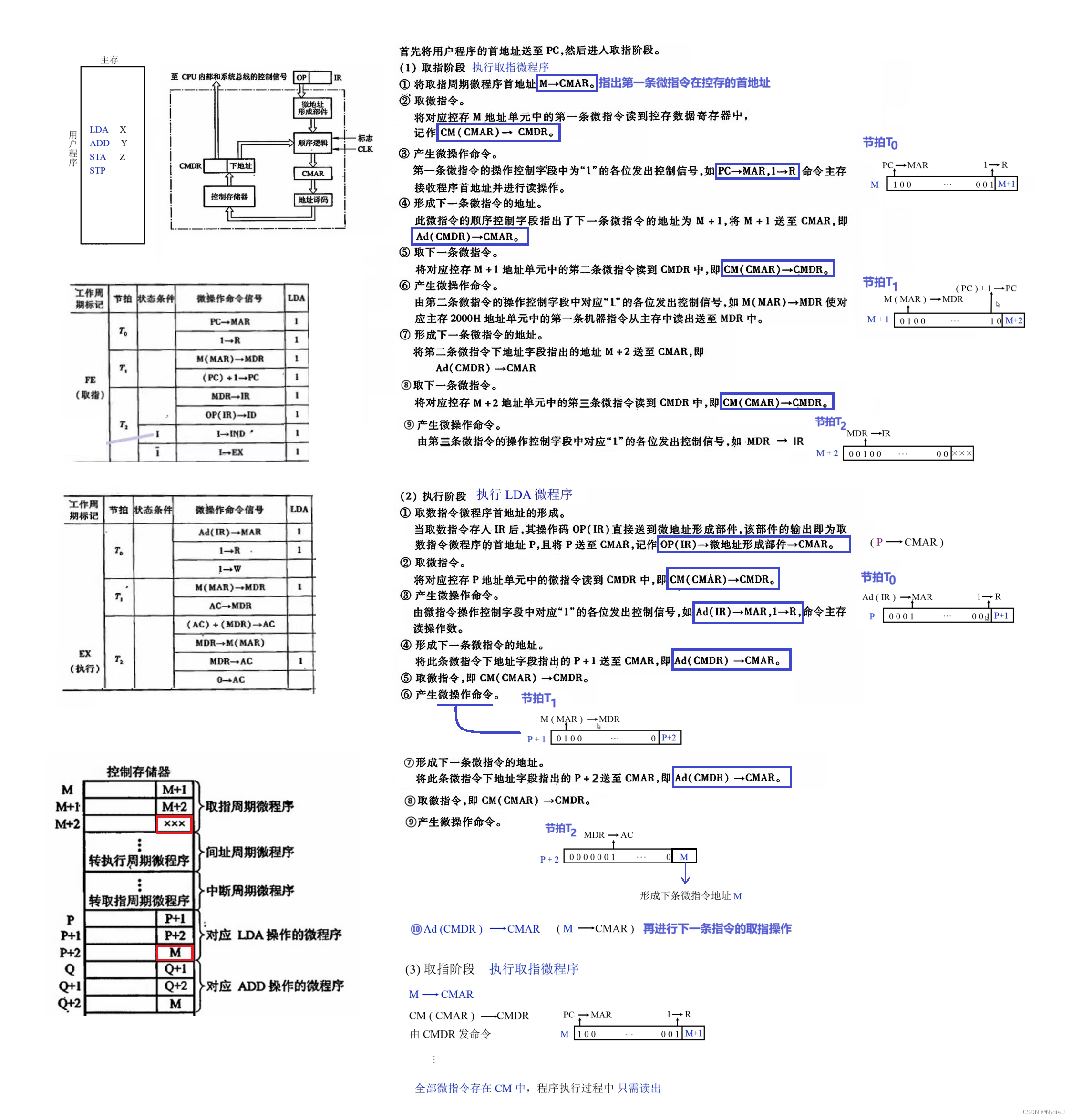

完成一条机器指令 需要 一个或者多个微操作命令,这些微操作命令存储起来变成微指令,每个节拍对应一个微指令,那么多个节拍对应的多个微指令就构成了微程序。微指令由0、1组成,每一个位置对应某一种或某一个微操作命令。即一条机器指令对应一个微程序。

微程序存入ROM中,执行时把微指令一条一条的从ROM读出,根据读出的微指令中有效控制信号的位置发出相应的信号,让计算机执行相应的操作 —— 存储逻辑(把逻辑信号存储在存储器中)

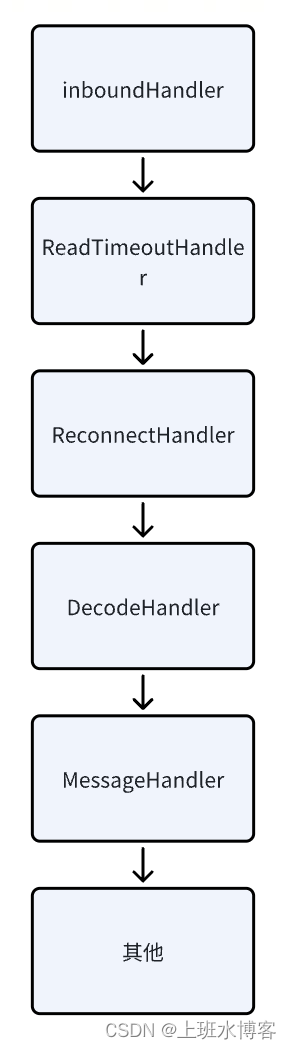

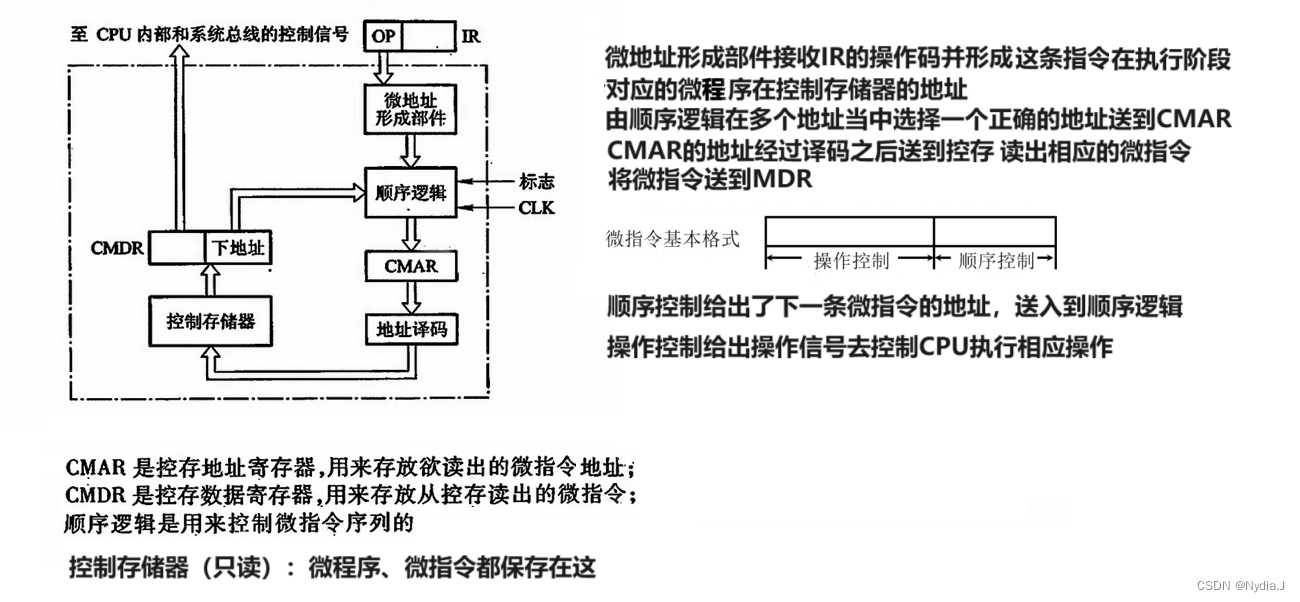

10.2.2 微程序控制单元框图及工作原理

-

机器指令对应的微程序

-

微程序控制单元的基本框图

-

工作原理

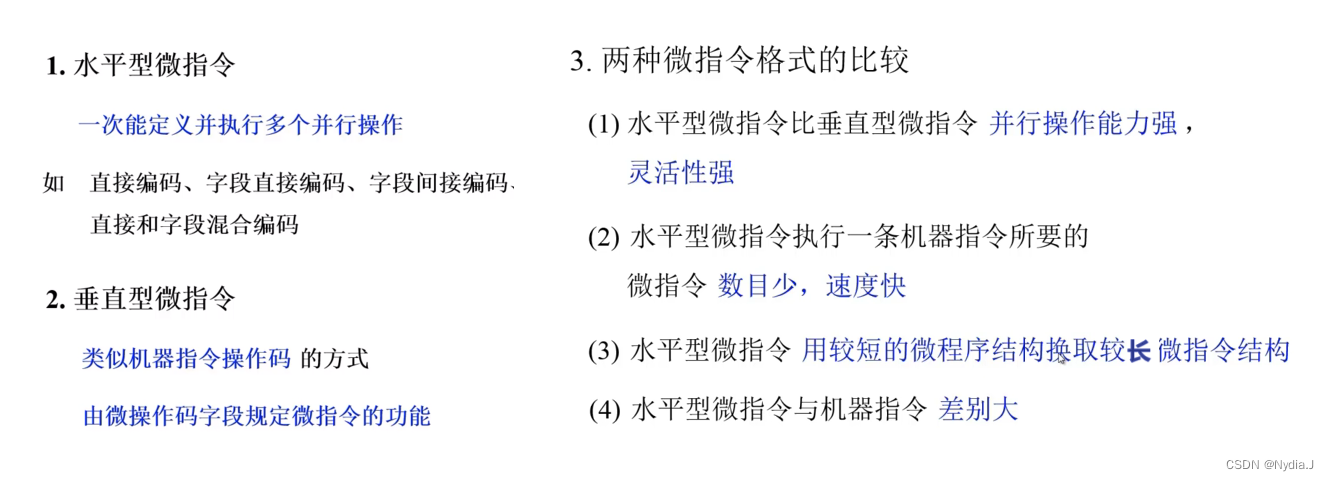

10.2.3 微指令的编码方式(控制方式)

-

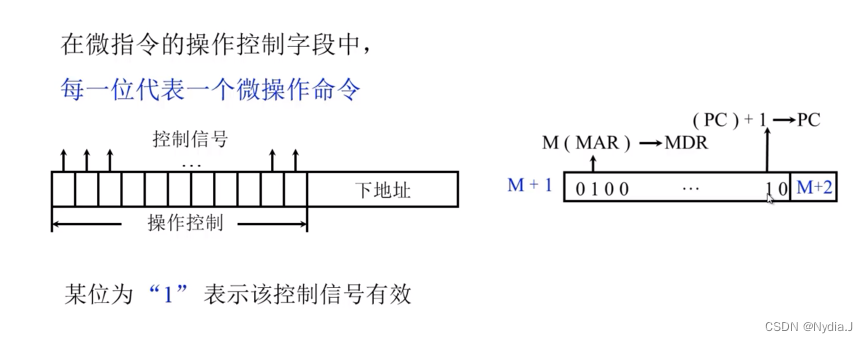

直接编码(直接控制)方式

-

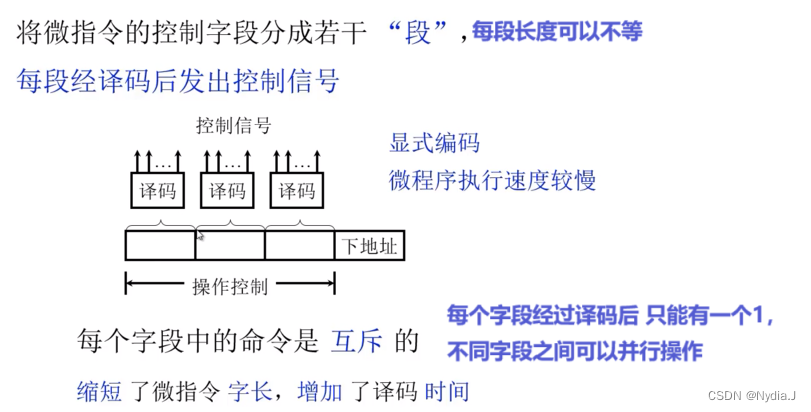

字段直接编码方式

-

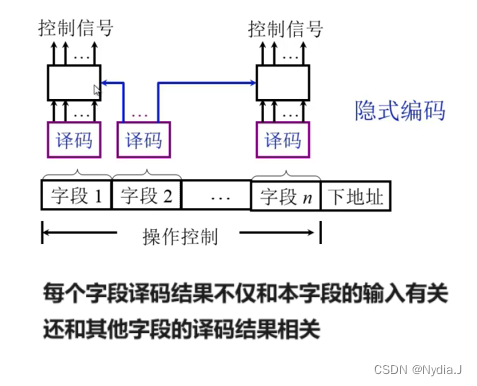

字段间接编码方式

-

混合编码

直接编码和字段编码(直接和间接)混合使用

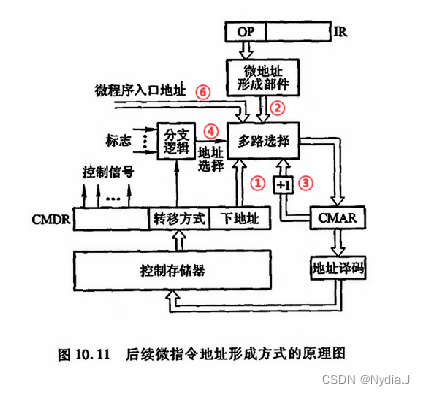

10.2.4 微指令序列地址的形成

-

直接由微指令的下地址字段指出

-

根据机器指令的操作码形成

当机器指令取至指令寄存器后,微指令的地址由操作码经微地址形成部件形成。微地址形成部件实际是一个编码器,其输人为指令操作码,输出就是对应该机器指令微程序的首地址。

-

增量计数器法

在很多情况下,后续微指令的地址是连续的,因此对于顺序地址,微指令可采用增量计数法,即(CMAR)+1 CMAR来形成后续微指令的地址。

-

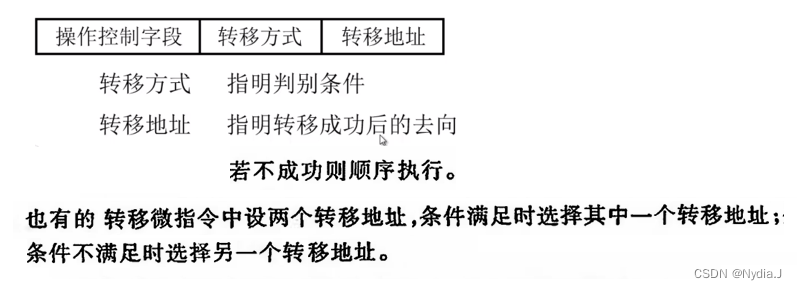

分支转移

-

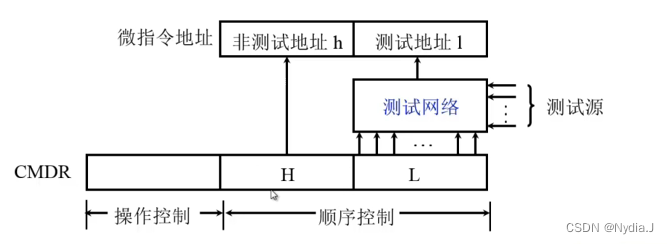

通过测试网络 - 用于微程序小范围内跳转

-

由硬件产生微程序人口地址

第一条微指令地址由专门 硬件产生

中断/间址周期 由硬件产生中断周期微程序首地址

10.2.5 微指令格式

10.2.6 静态微程序设计和动态微程序设计

- 静态微程序设计:通常指令系统是固定的,对应每一条机器指令的微程序是计算机设计者事先编好的,因此一般微程序无须改变,其控制存储器采用ROM。

- 动态微程序设计:人们可以通过改变微指令和微程序来改变机器的指令系统,有利于仿真,采用 EPROM作为控制存储器。但是这种设计对用户的要求很高,目前难以推广。

10.2.7 毫微程序设计

微程序可看做是解释机器指令的,毫微程序可看做是解释微程序的,而组成微程序的毫微指令则是用来解释微指令的。

10.2.8 串行微程序控制和并行微程序控制

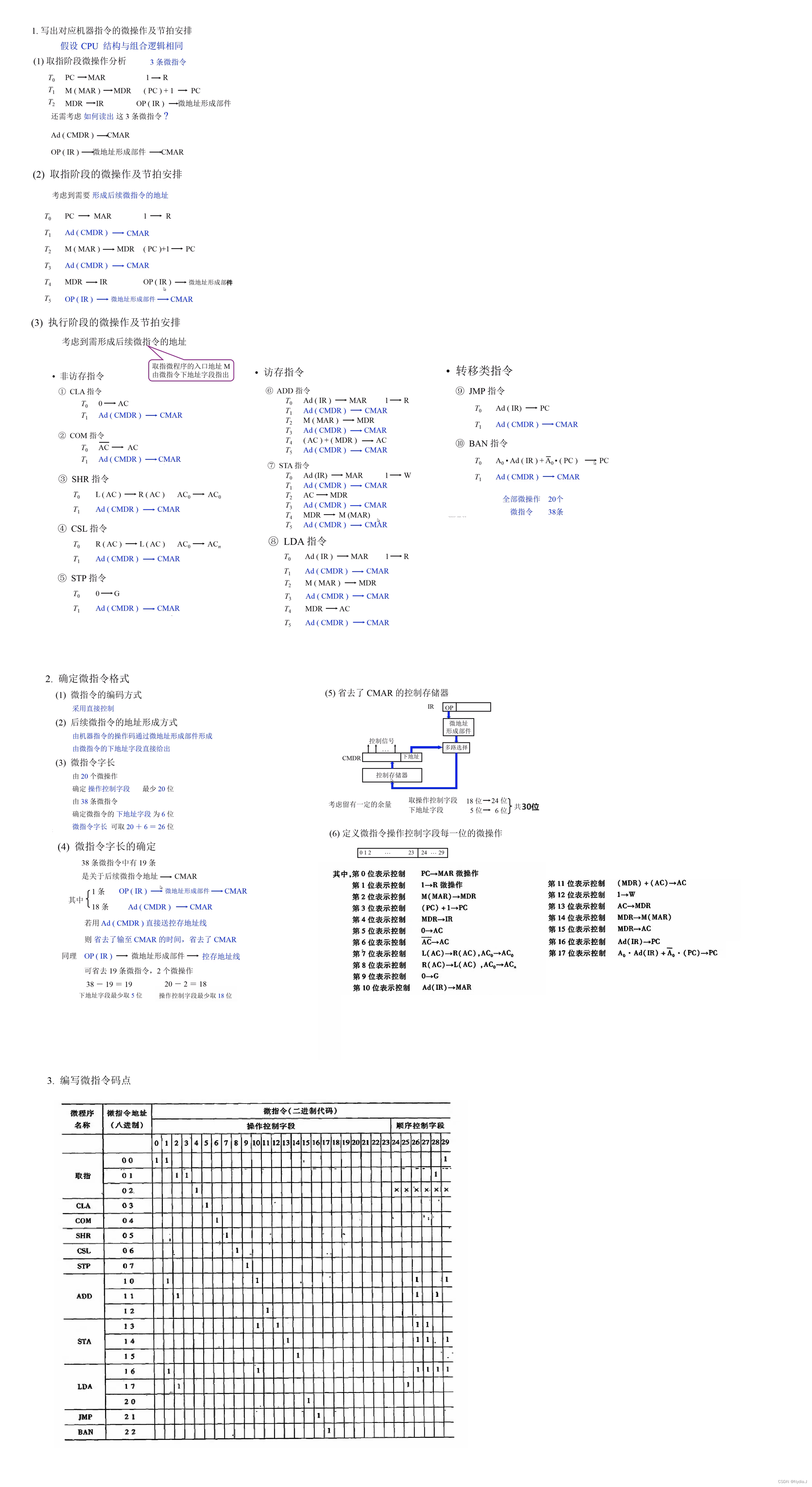

10.2.9 微程序设计举例

参考:

教材:计算机组成原理 (唐朔飞).pdf

博客:https://blog.csdn.net/weixin_51825055/article/details/133738724

视频:https://www.bilibili.com/video/BV1t4411e7LH?p=126&vd_source=a89593e8d33b31a56b894ca9cad33d33