黑金的教程做的实在太拉闸了,于是自己摸索信号采集模块的使用方法。

ADC模块:AN9238

FPGA开发板:AX7020;Xilinx 公司的 Zynq7000 系列的芯片XC7Z020-2CLG400I,400引脚 FBGA 封装。

往期回顾:

从零开始利用MATLAB进行FPGA设计(六)用ADC采集信号教程1

目录

1.引脚绑定

2.ILA在线调试

1.引脚绑定

工程文件总体结构如下:

引脚绑定:

############## clock and reset define##################

create_clock -period 20.000 [get_ports clk50m]

set_property IOSTANDARD LVCMOS33 [get_ports clk50m]

set_property PACKAGE_PIN U18 [get_ports clk50m]

set_property IOSTANDARD LVCMOS33 [get_ports reset_n]

set_property PACKAGE_PIN N15 [get_ports reset_n]

##############AX7020 and AX7010 J11##################

set_property PACKAGE_PIN F16 [get_ports {ad2_in[0]}]

set_property PACKAGE_PIN F20 [get_ports {ad2_in[1]}]

set_property PACKAGE_PIN F19 [get_ports {ad2_in[2]}]

set_property PACKAGE_PIN G20 [get_ports {ad2_in[3]}]

set_property PACKAGE_PIN G19 [get_ports {ad2_in[4]}]

set_property PACKAGE_PIN H18 [get_ports {ad2_in[5]}]

set_property PACKAGE_PIN J18 [get_ports {ad2_in[6]}]

set_property PACKAGE_PIN L20 [get_ports {ad2_in[7]}]

set_property PACKAGE_PIN L19 [get_ports {ad2_in[8]}]

set_property PACKAGE_PIN M20 [get_ports {ad2_in[9]}]

set_property PACKAGE_PIN M19 [get_ports {ad2_in[10]}]

set_property PACKAGE_PIN K18 [get_ports {ad2_in[11]}]

set_property PACKAGE_PIN H20 [get_ports {ad1_in[1]}]

set_property PACKAGE_PIN J20 [get_ports {ad1_in[0]}]

set_property PACKAGE_PIN L17 [get_ports {ad1_in[3]}]

set_property PACKAGE_PIN L16 [get_ports {ad1_in[2]}]

set_property PACKAGE_PIN M18 [get_ports {ad1_in[5]}]

set_property PACKAGE_PIN M17 [get_ports {ad1_in[4]}]

set_property PACKAGE_PIN D20 [get_ports {ad1_in[7]}]

set_property PACKAGE_PIN D19 [get_ports {ad1_in[6]}]

set_property PACKAGE_PIN E19 [get_ports {ad1_in[9]}]

set_property PACKAGE_PIN E18 [get_ports {ad1_in[8]}]

set_property PACKAGE_PIN G18 [get_ports {ad1_in[11]}]

set_property PACKAGE_PIN G17 [get_ports {ad1_in[10]}]

set_property PACKAGE_PIN H17 [get_ports clk65m_1]

set_property IOSTANDARD LVCMOS33 [get_ports clk65m_1]

set_property PACKAGE_PIN F17 [get_ports clk70m_1]

set_property IOSTANDARD LVCMOS33 [get_ports clk70m_1]

set_property IOSTANDARD LVCMOS33 [get_ports {ad1_in[*]}]

set_property IOSTANDARD LVCMOS33 [get_ports {ad2_in[*]}]

#set_property IOB true [get_ports ad2_in[*]]

#set_property IOB true [get_ports ad1_in[*]]

create_debug_core u_ila_0 ila

set_property ALL_PROBE_SAME_MU true [get_debug_cores u_ila_0]

set_property ALL_PROBE_SAME_MU_CNT 1 [get_debug_cores u_ila_0]

set_property C_ADV_TRIGGER false [get_debug_cores u_ila_0]

set_property C_DATA_DEPTH 1024 [get_debug_cores u_ila_0]

set_property C_EN_STRG_QUAL false [get_debug_cores u_ila_0]

set_property C_INPUT_PIPE_STAGES 0 [get_debug_cores u_ila_0]

set_property C_TRIGIN_EN false [get_debug_cores u_ila_0]

set_property C_TRIGOUT_EN false [get_debug_cores u_ila_0]

set_property port_width 1 [get_debug_ports u_ila_0/clk]

connect_debug_port u_ila_0/clk [get_nets [list pll_inst/inst/clk_out1]]

set_property PROBE_TYPE DATA_AND_TRIGGER [get_debug_ports u_ila_0/probe0]

set_property port_width 12 [get_debug_ports u_ila_0/probe0]

connect_debug_port u_ila_0/probe0 [get_nets [list {v_ad_inst/ad1_in[0]} {v_ad_inst/ad1_in[1]} {v_ad_inst/ad1_in[2]} {v_ad_inst/ad1_in[3]} {v_ad_inst/ad1_in[4]} {v_ad_inst/ad1_in[5]} {v_ad_inst/ad1_in[6]} {v_ad_inst/ad1_in[7]} {v_ad_inst/ad1_in[8]} {v_ad_inst/ad1_in[9]} {v_ad_inst/ad1_in[10]} {v_ad_inst/ad1_in[11]}]]

create_debug_port u_ila_0 probe

set_property PROBE_TYPE DATA_AND_TRIGGER [get_debug_ports u_ila_0/probe1]

set_property port_width 12 [get_debug_ports u_ila_0/probe1]

connect_debug_port u_ila_0/probe1 [get_nets [list {v_ad_inst/ad2_in[0]} {v_ad_inst/ad2_in[1]} {v_ad_inst/ad2_in[2]} {v_ad_inst/ad2_in[3]} {v_ad_inst/ad2_in[4]} {v_ad_inst/ad2_in[5]} {v_ad_inst/ad2_in[6]} {v_ad_inst/ad2_in[7]} {v_ad_inst/ad2_in[8]} {v_ad_inst/ad2_in[9]} {v_ad_inst/ad2_in[10]} {v_ad_inst/ad2_in[11]}]]

create_debug_port u_ila_0 probe

set_property PROBE_TYPE DATA_AND_TRIGGER [get_debug_ports u_ila_0/probe2]

set_property port_width 12 [get_debug_ports u_ila_0/probe2]

connect_debug_port u_ila_0/probe2 [get_nets [list {v_ad_inst/ad_ch2[0]} {v_ad_inst/ad_ch2[1]} {v_ad_inst/ad_ch2[2]} {v_ad_inst/ad_ch2[3]} {v_ad_inst/ad_ch2[4]} {v_ad_inst/ad_ch2[5]} {v_ad_inst/ad_ch2[6]} {v_ad_inst/ad_ch2[7]} {v_ad_inst/ad_ch2[8]} {v_ad_inst/ad_ch2[9]} {v_ad_inst/ad_ch2[10]} {v_ad_inst/ad_ch2[11]}]]

create_debug_port u_ila_0 probe

set_property PROBE_TYPE DATA_AND_TRIGGER [get_debug_ports u_ila_0/probe3]

set_property port_width 12 [get_debug_ports u_ila_0/probe3]

connect_debug_port u_ila_0/probe3 [get_nets [list {v_ad_inst/ad_ch1[0]} {v_ad_inst/ad_ch1[1]} {v_ad_inst/ad_ch1[2]} {v_ad_inst/ad_ch1[3]} {v_ad_inst/ad_ch1[4]} {v_ad_inst/ad_ch1[5]} {v_ad_inst/ad_ch1[6]} {v_ad_inst/ad_ch1[7]} {v_ad_inst/ad_ch1[8]} {v_ad_inst/ad_ch1[9]} {v_ad_inst/ad_ch1[10]} {v_ad_inst/ad_ch1[11]}]]

set_property C_CLK_INPUT_FREQ_HZ 300000000 [get_debug_cores dbg_hub]

set_property C_ENABLE_CLK_DIVIDER false [get_debug_cores dbg_hub]

set_property C_USER_SCAN_CHAIN 1 [get_debug_cores dbg_hub]

connect_debug_port dbg_hub/clk [get_nets clk50m_IBUF]

ADC的引脚绑定参考开发板J11的引脚信息。

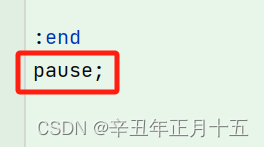

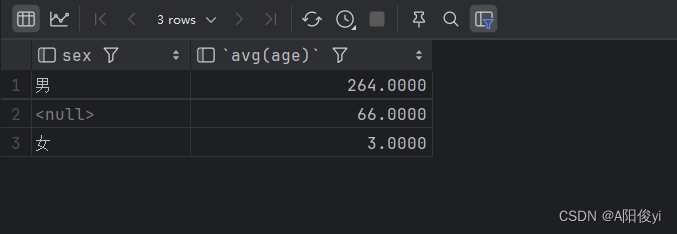

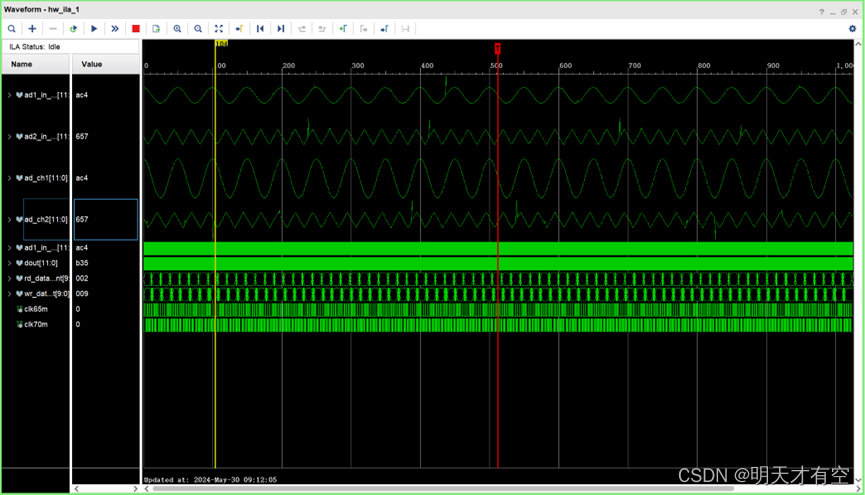

2.ILA在线调试

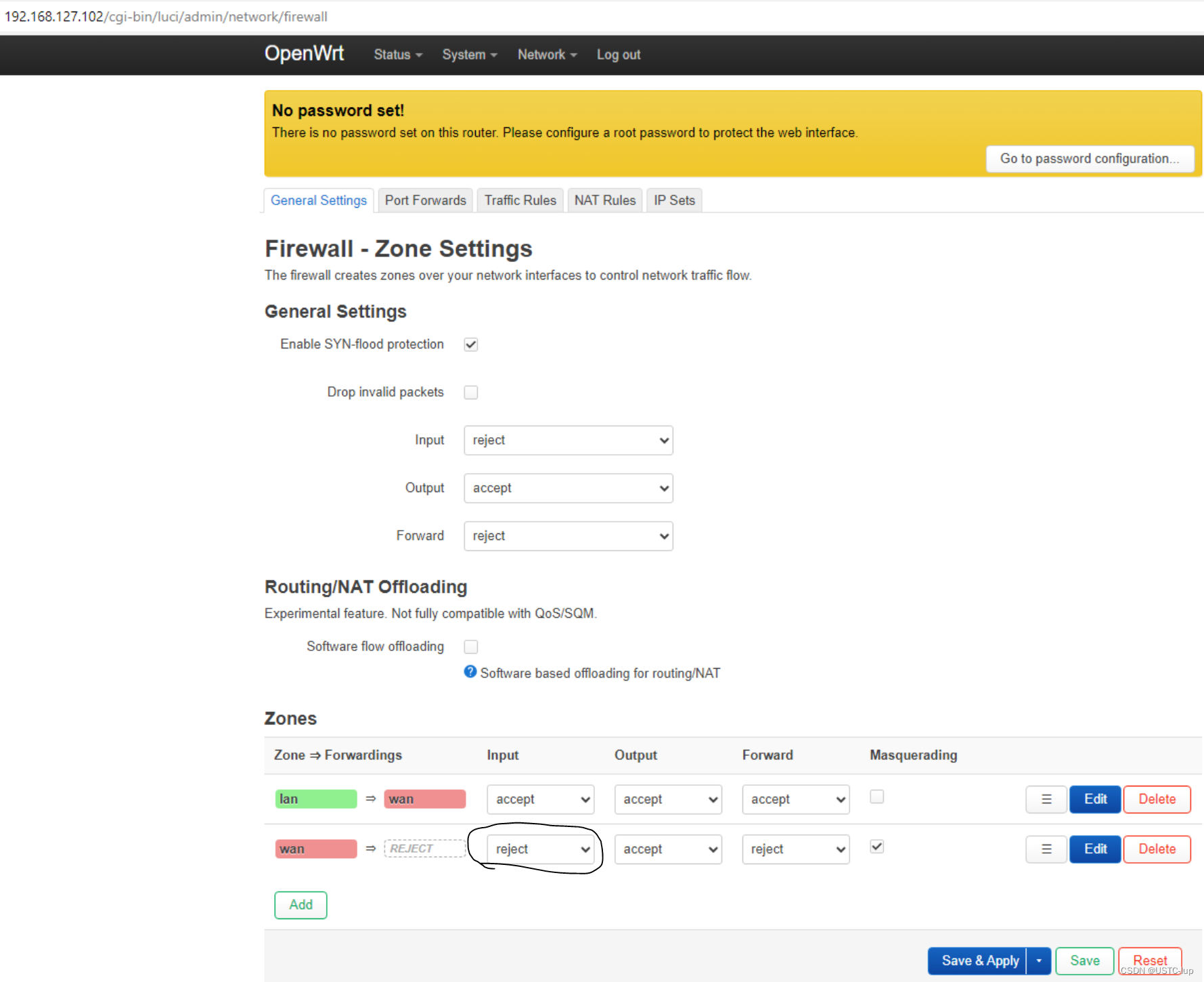

连接好开发板的JTAG接口,给开发板上电。在HARDWARE MANAGER界面点击“Auto Connect”,自动连接设备。选择 xc7z020_1,右键“Program Device...”。在弹出窗口中点击“Program”。

此时弹出在线调试窗口,出现之前添加的信号:

ILA的状态控制和显示窗口包括:

- 循环采样

- 启动采样

- 无条件执行采样

- 停止采样