|

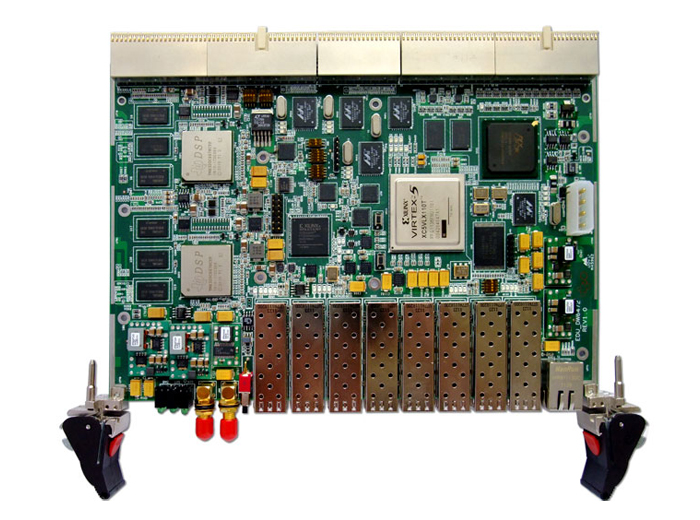

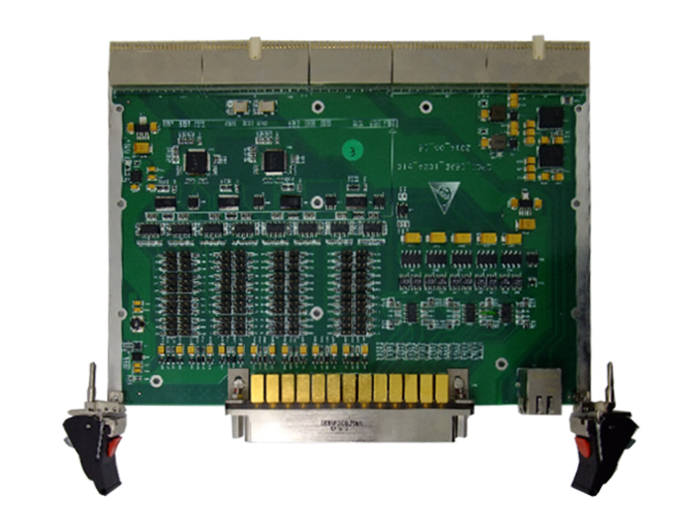

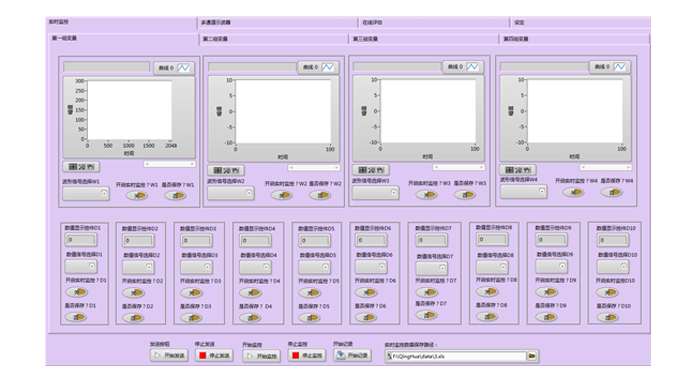

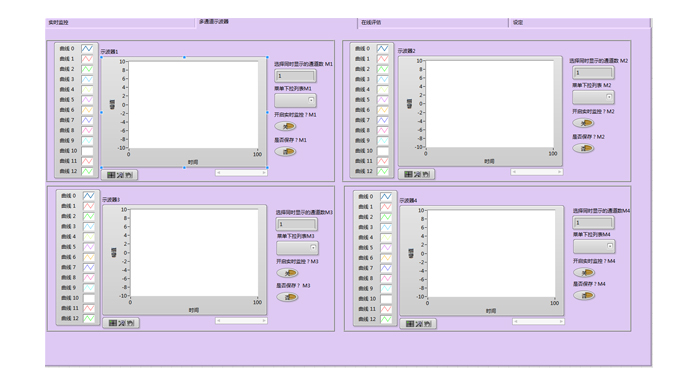

DSP实时分析平台设计方案:924-6U CPCI振动数据DSP实时分析平台

news2026/2/14 20:54:12

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.coloradmin.cn/o/1643141.html

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈,一经查实,立即删除!相关文章

Qt服务器端与客户端交互

Qt做客户端与服务器端交互第一步引入network 第一步引入network后继续编程首先界面设计 创建server和socket

引入QTcpServer,QTcpSocket

MainWindow.h代码如下

#ifndef MAINWINDOW_H

#define MAINWINDOW_H#include <QMainWindow>

#include <QTcpServer&…

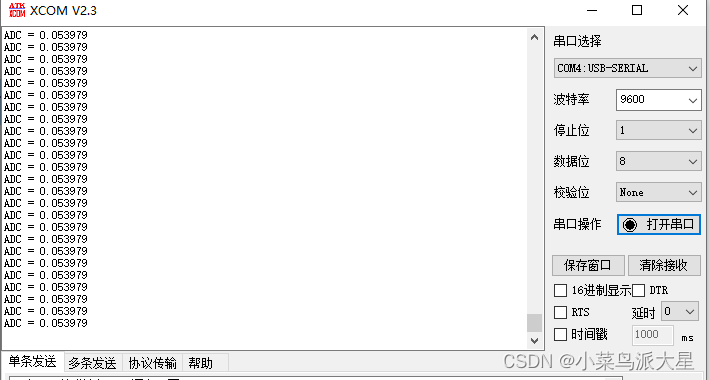

STM32入门学习之ADC

1.ADC在STM32进行数据采集时十分重要。通过ADC可以将外界的数字信号转换为模拟信号,以满足采样的需求。(资料参考于正点原子) STM32 拥有 1~3 个 ADC ( STM32F101/102 系列只有 1 个 ADC ),这些 ADC 可以独立使用&#…

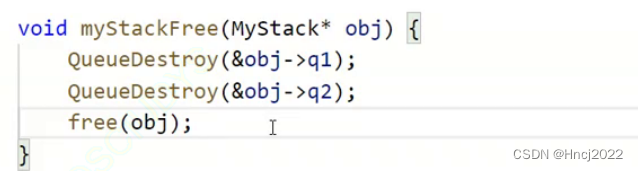

数据结构学习/复习7--栈的实现/括号匹配练习题/队列的实现/队列实现栈练习

一、栈 1.概念及性质 2.栈的实现(top0版) 注意事项:top也可初始为-1,代码需要调整 二、栈练习 1.括号匹配 三、队列 1.概念及性质 2、队列的实现 四、队列练习 1.两个队列实现栈

从零开始学AI绘画,万字Stable Diffusion终极教程(四)

【第4期】图生图

欢迎来到SD的终极教程,这是我们的第四节课

这套课程分为六节课,会系统性的介绍sd的全部功能,让你打下坚实牢靠的基础

1.SD入门

2.关键词

3.Lora模型

4.图生图

5.controlnet

6.知识补充 在前面的课程中,我…

动手写一个简单的Android 表格控件支持固定列

Android 动手写一个简洁版表格控件

简介

源码已放到 Github Gitee

作为在测绘地理信息行业中穿梭的打工人,遇到各种数据采集需求,既然有数据采集需求,那当然少不了数据展示功能,最常见的如表格方式展示。 当然,类似…

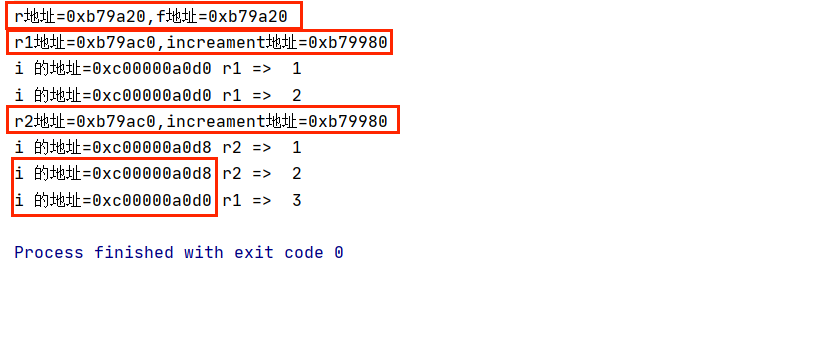

Go 语言基础(一)【基本用法】

前言 最近心情格外不舒畅,不仅仅是对前途的迷茫,这种迷茫倒是我自己的问题还好,关键它是我们这种普通吗喽抗衡不了的。 那就换个脑子,学点新东西吧,比如 Go?

1、Go 语言入门 介绍就没必要多说了࿰…

vue快速入门(五十四)$nextTick的使用

注释很详细,直接上代码 上一篇 新增内容 $nextTick的使用场景演示 源码 App.vue

<template><div id"app"><h3>{{name}}</h3><button click"showfixed">修改</button><form action"post" v-s…

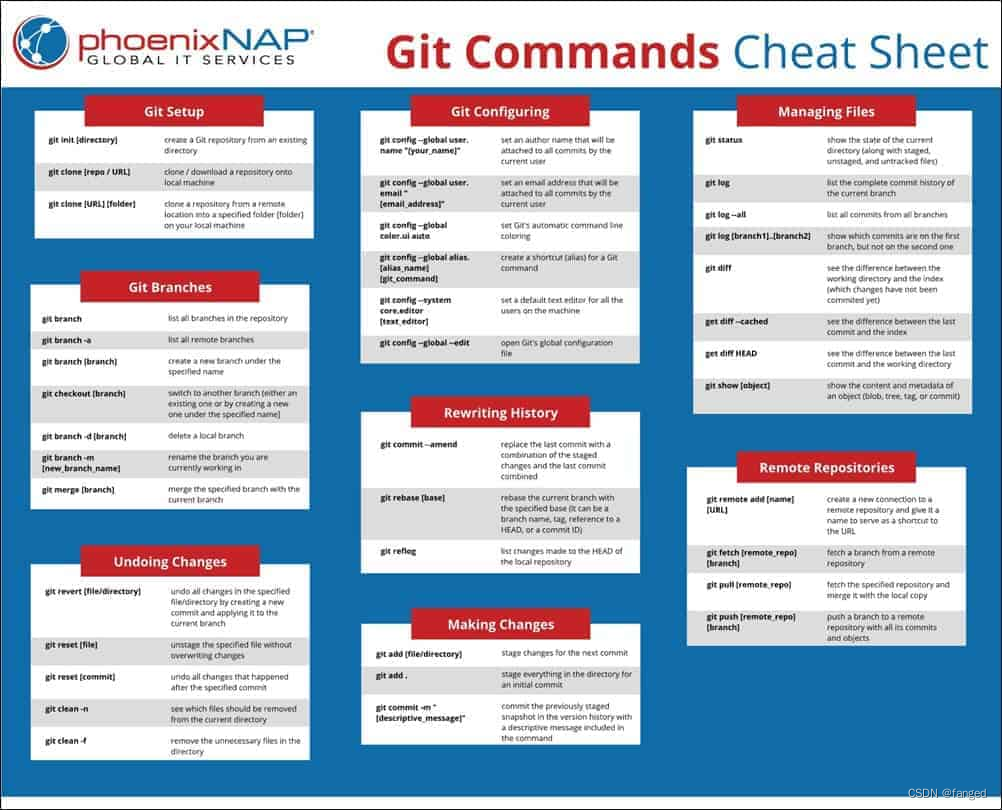

Git常用(持续更新)

常用场景: 初始化:

git config --global user.name "codelabs"

git config --global user.email mycodelabs.com

git init

git remote add origin https://github.com/username/repository.git

git pull origin master

提交:

gi…

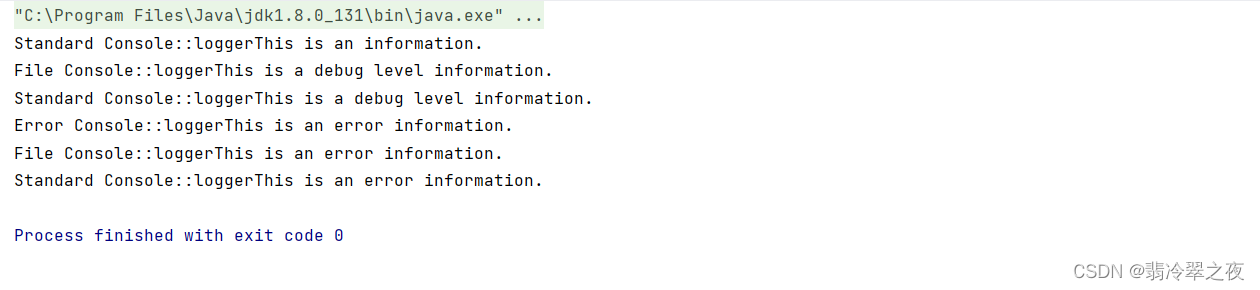

设计模式: 责任链模式

目录 一,责任链模式

二,特点

四,实现步骤

五,代码 一,责任链模式

责任链模式(Chain of Responsibility Pattern)是一种软件设计模式,它属于行为型模式。在这种模式中,…

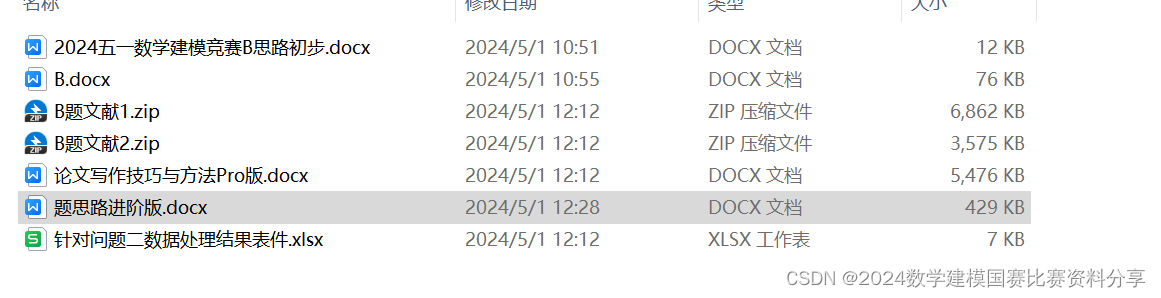

2024五一赛数学建模A题B题C题完整思路+数据代码+参考论文

A题 钢板最优切割路径问题

(完整资料在文末获取) 1. 建立坐标系和表示方法:

在建模之前,我们需要将切割布局转换为数学表示。首先,我们可以将布局中的每个点表示为二维坐标系中的一个点。例如,B1可以表示…

【吊打面试官系列】Java高并发篇 - Thread 类中的 yield 方法有什么作用?

大家好,我是锋哥。今天分享关于 【Thread 类中的 yield 方法有什么作用?】面试题,希望对大家有帮助; Thread 类中的 yield 方法有什么作用? 使当前线程从执行状态(运行状态)变为可执行态&#x…

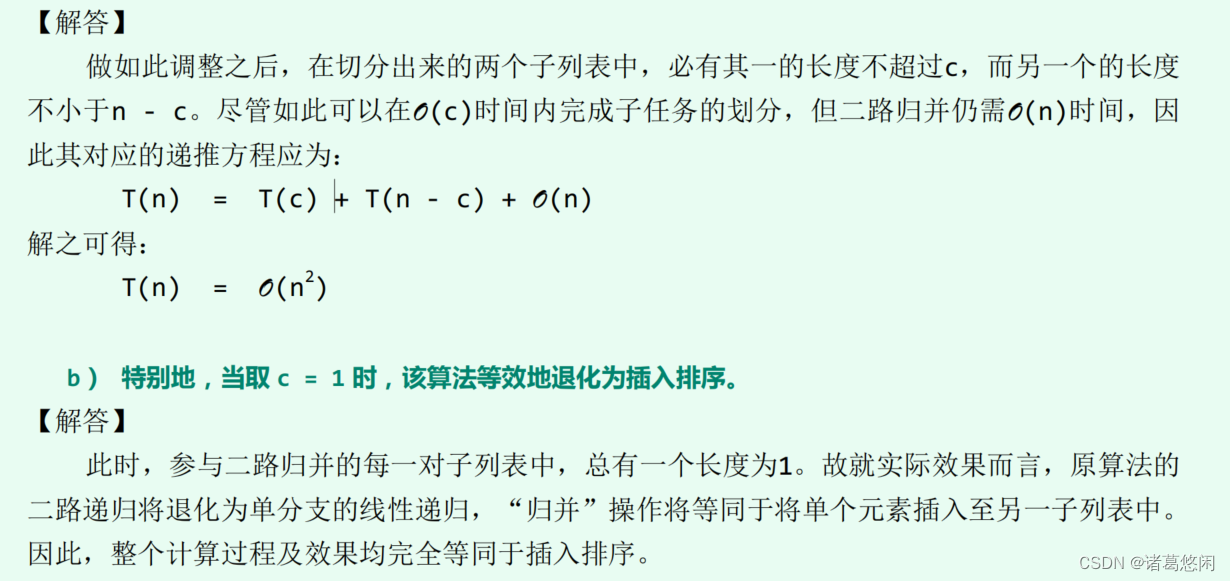

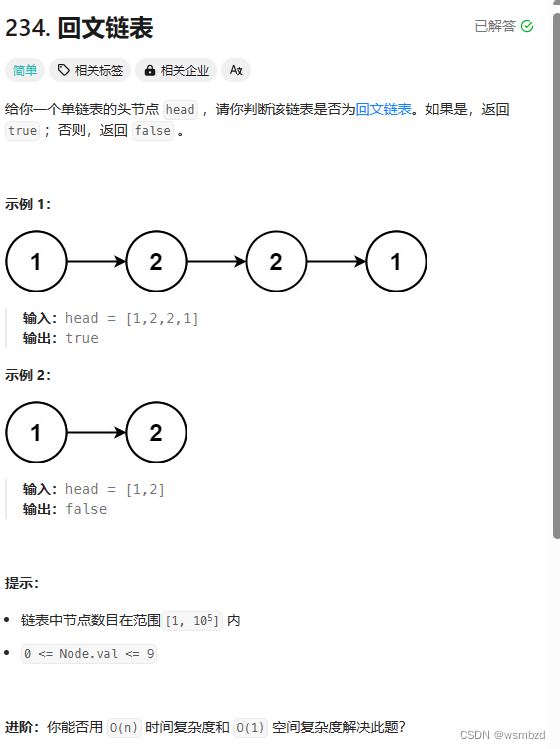

【数据结构(邓俊辉)学习笔记】列表04——排序器

文章目录 0. 统一入口1. 选择排序1.1 构思1.2 实例1.3 实现1.4 复杂度 2. 插入排序2.1 构思2.2 实例2.3 实现2.4 复杂度分析2.5 性能分析 3. 归并排序3.1 二路归并算法3.1.1 二路归并算法原理3.1.2 二路归并算法实现3.1.3 归并时间 3.2 分治策略3.2.1 实现3.2.2 排序时间 4. 总…

源支付V7开源版,源支付开源版,已去除安装扩展

源支付V7开源版,源支付开源版,已去除安装扩展 上传源码

设置伪静态

已去除安装扩展,直接上传就可以安装

开源版通道少了好几个

视频教程:https://www.bilibili.com/video/BV1mZ42177VY/

基于OpenCV-DNN的YOLOv9目标检测实现

⚠申明: 未经许可,禁止以任何形式转载,若要引用,请标注链接地址。 全文共计3077字,阅读大概需要3分钟 🌈更多学习内容, 欢迎👏关注👀【文末】我的个人微信公众号…

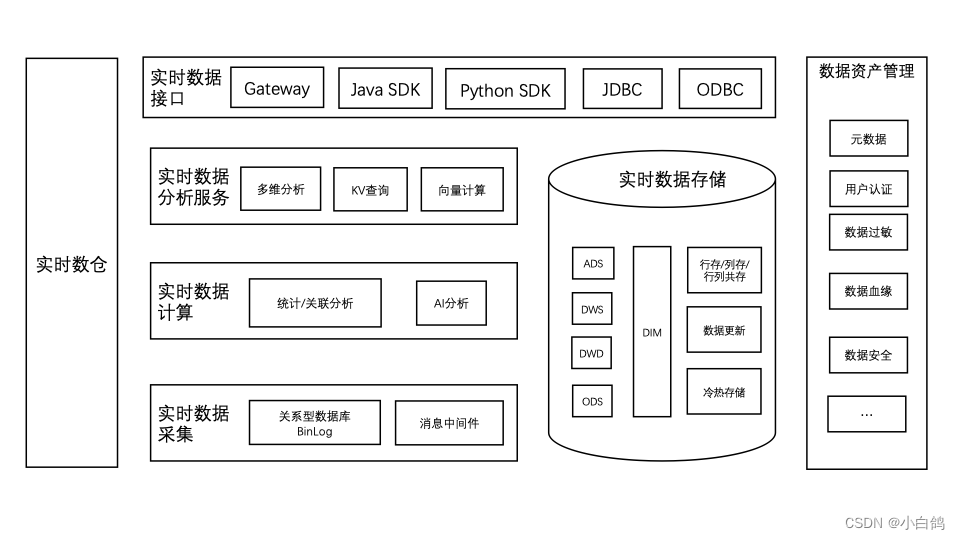

【实时数仓架构】方法论

笔者不是专业的实时数仓架构,这是笔者从其他人经验和网上资料整理而来,仅供参考。写此文章意义,加深对实时数仓理解。

一、实时数仓架构技术演进

1.1 四种架构演进

1)离线大数据架构 一种批处理离线数据分析架构,…

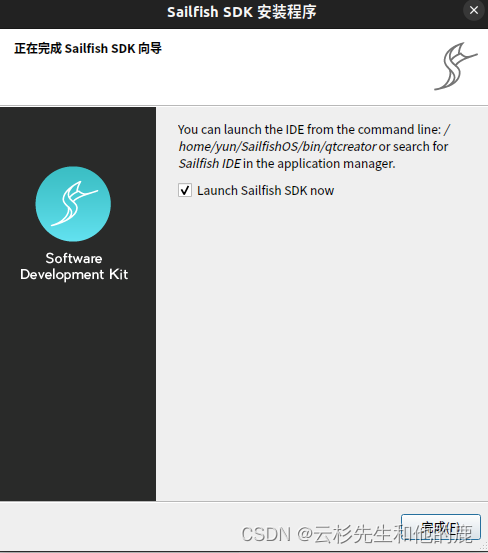

SFOS1:开发环境搭建

一、简介 最近在学习sailfish os的应用开发,主要内容是QmlPython。所以,在开发之前需要对开发环境(virtualBox官方SDKcmake编译器python)进行搭建。值得注意的是,我的开发环境是ubuntu22.04。如果是windows可能大同小异…