计算机组成原理:实现计算机体系结构所体现的属性,具体指令的实现对程序员透明,即研究如何用硬件实现所定义的接口

计算机系统=硬件(计算机的实体,如主机、外设)+软件(由具有各类特殊功能的程序组成)

软件

(1)系统软件:用来管理整个计算机系统。如操作系统、数据库管理系统、标准程序库(库函数)、网络软件(实现TCP/IP协议的软件模块)、语言处理程序(高级语言→机器语言)、服务程序(调试代码的调试程序)

(2)应用软件:按任务需要编制成的各种程序

文章目录

- 一.计算机发展历程

- 1.计算机的四代

- 2.摩尔定律

- 二.计算机硬件的基本组成

- (一)早期冯·诺依曼机

- (二)现代计算机的组织结构

- (三)计算机的功能部件

- 1.输入设备

- 2.输出设备

- 3.存储器

- 4.运算器

- 5.控制器

- (四)中央处理器CPU

- (五)计算机的工作过程

- 四.计算机系统层次结构

- 五.计算机的性能指标

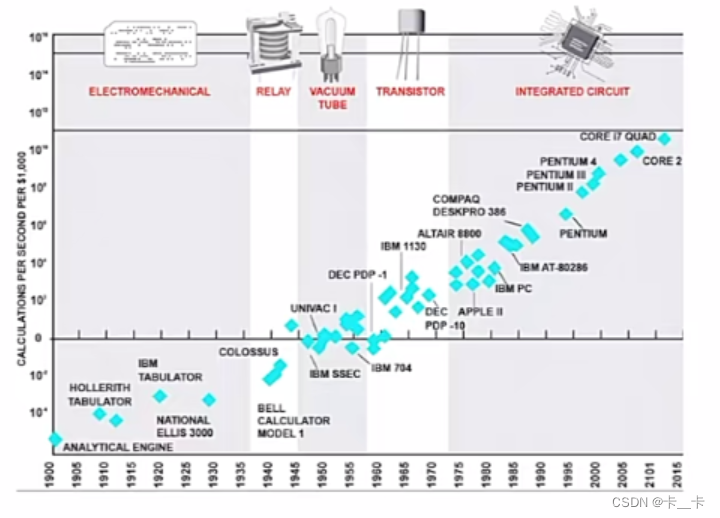

一.计算机发展历程

1.计算机的四代

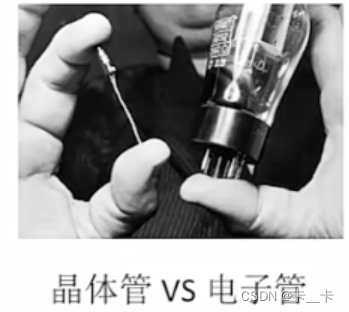

(1)第一代计算机:电子管时代

使用机器语言编程,容量小、体积大、成本高、性能低

(2)第二代计算机:晶体管时代

速度提升,软件使用高级语言,形成操作系统雏形

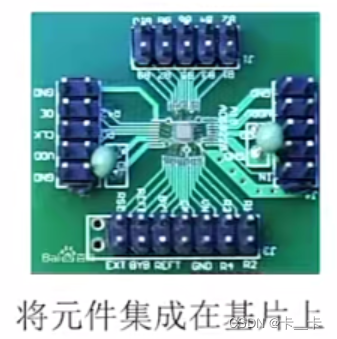

(3)第三代计算机:中小规模集成电路时代

使用半导体存储器,出现分时操作系统,高级语言开始发展

(4)第四代计算机:超大规模集成电路时代

微处理器出现,并行、流水线、高速缓存、虚拟存储器出现

2.摩尔定律

揭示了信息技术进步的速度。集成电路上可容纳的晶体管数目,约每隔18个月便会增加一倍,整体性能也将提升一倍

二.计算机硬件的基本组成

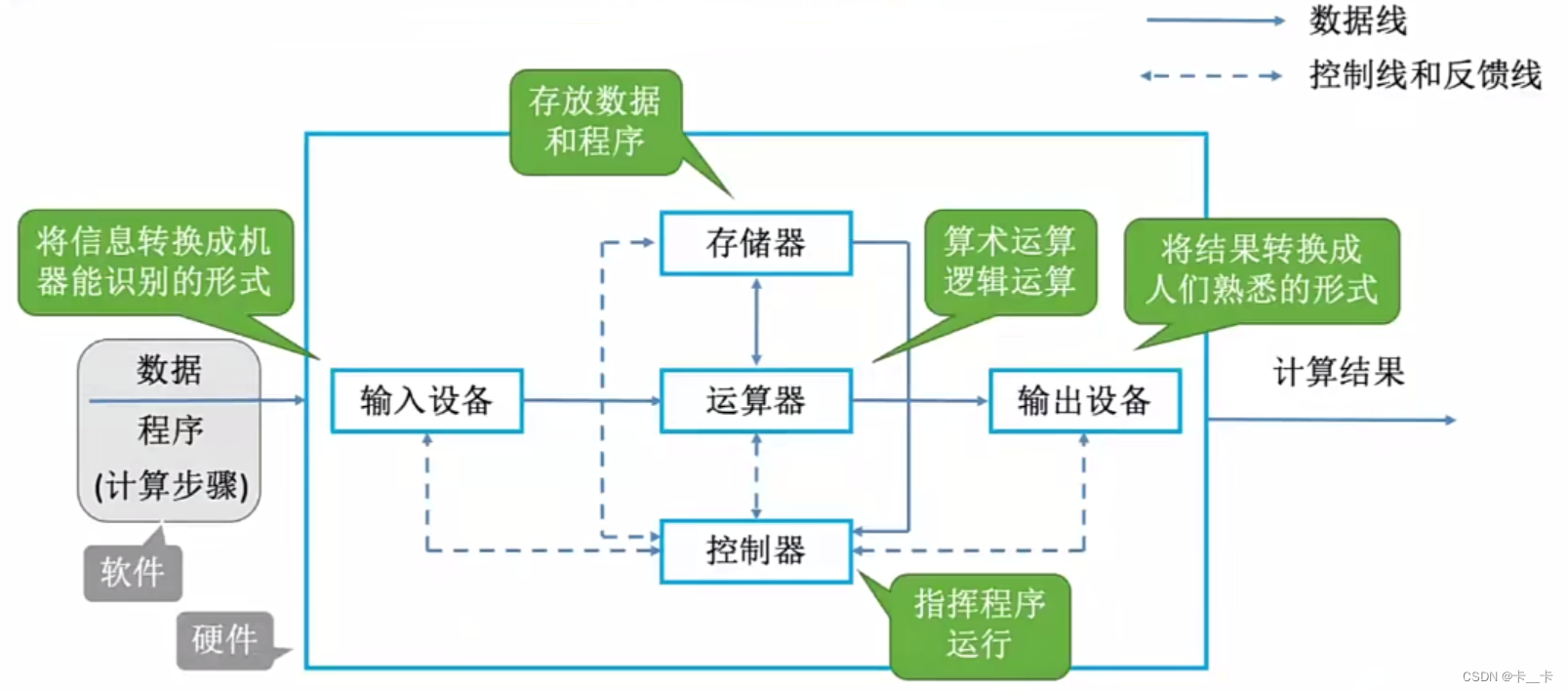

(一)早期冯·诺依曼机

冯·诺依曼提出了存储程序的概念。“存储程序”是指将指令以二进制代码的形式事先输入计算机的主存储器,然后按其在存储器中的首地址执行程序的第一条指令,以后就按该程序的规定顺序执行其他指令,直至程序执行结束。

特点:

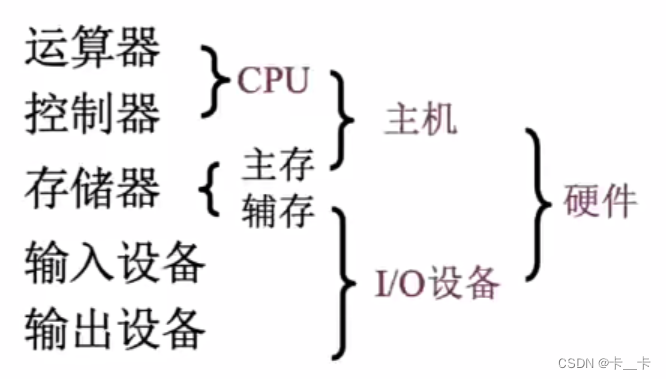

1.计算机硬件系统组成:运算器、存储器、控制器、输入设备、输出设备

2.指令和数据以同等地位存储在存储器中,并可按地址寻访

3.指令和数据均用二进制码表示

4.指令由操作码和地址码组成。操作码指出操作的类型,地址码指出操作数的地址

5.指令在存储器内按顺序存放。通常,指令是顺序执行的,在特定条件下可根据运算结果或根据设定的条件改变执行顺序

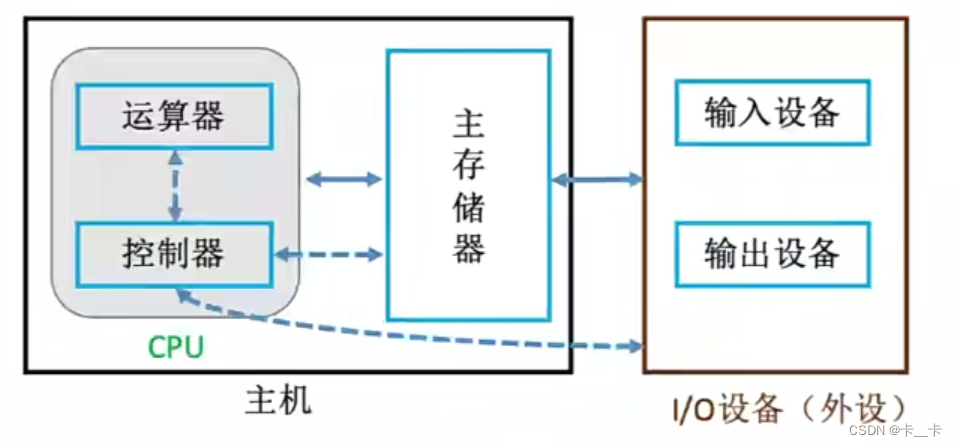

6.早期的冯·诺依曼以运算器为中心,输入/输出设备通过运算器与存储器传送数据

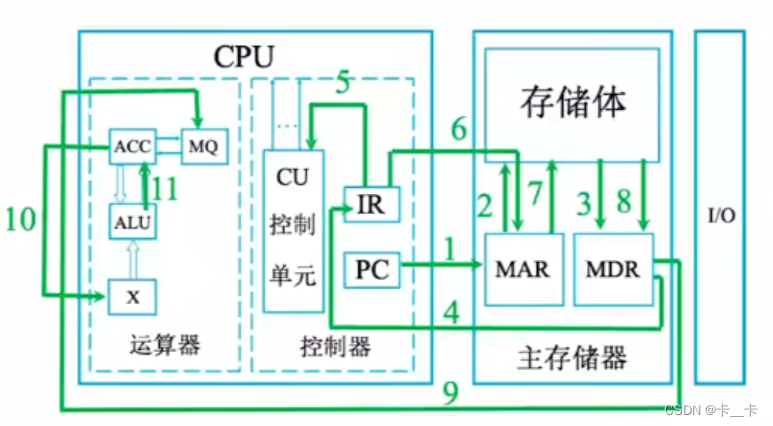

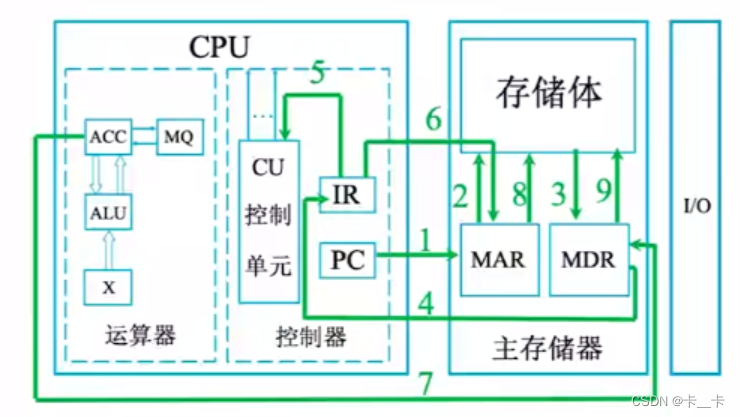

早期冯·诺依曼模型机的CPU包含算术逻辑单元ALU、通用寄存器组GPRs,标志寄存器、控制器、指令寄存器IR、程序计数器PC、存储器地址寄存器MAR、存储器数据寄存器MDR

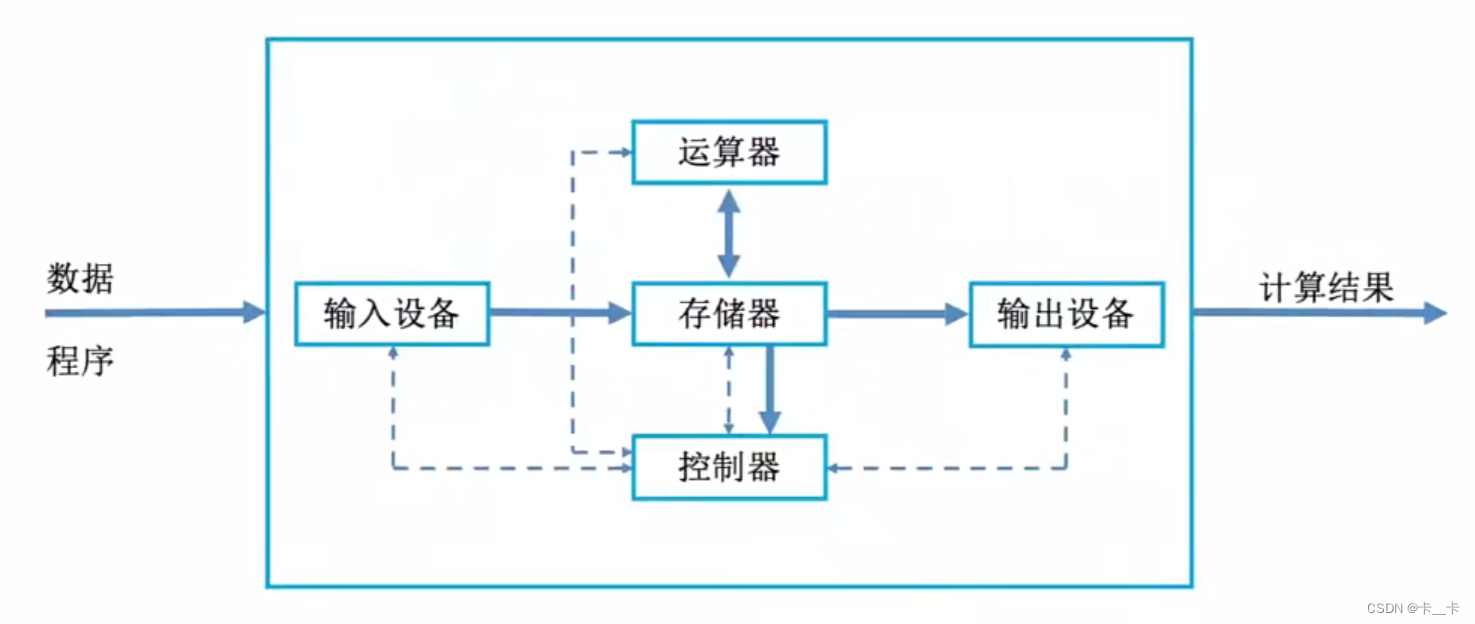

(二)现代计算机的组织结构

随着微电子技术的进步,同时计算机需要处理、加工的信息量也与日俱增,大量I/O设备的速度和CPU的速度差距悬殊,故以运算器为中心的结构不能满足计算机发展的要求。现代计算机已发展为以存储器为中心,使I/O操作尽可能绕过CPU,直接在I/O设备和存储器之间完成,以提高系统的整体运行效率。

(三)计算机的功能部件

1.输入设备

将程序和数据以机器能识别和接收的信息形式输入计算机。如键盘、鼠标、扫描仪、摄像机等。

2.输出设备

将计算机处理的结果以人们能接受的形式或其他系统所要求的信息形式输出。如显示器、打印机

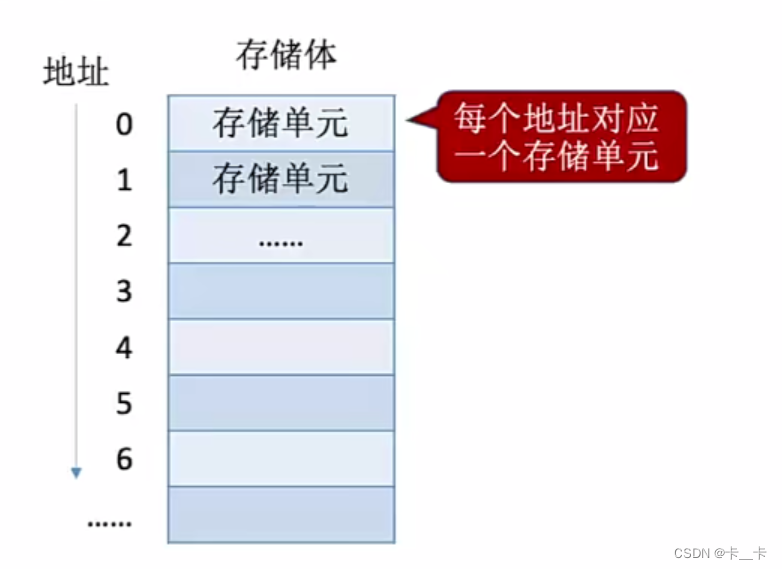

3.存储器

计算机的存储部件,用来存放程序和数据。

存储器分为主存储器(主存)和辅助存储器(辅存)。CPU能够直接访问的存储器是主存,而辅存用于帮助主存记忆更多的信息。辅存中的信息必须调入主存后,才能被CPU访问。

主存组成部分:

(1)存储体:存放二进制信息。存储体由许多存储单元组成,每个存储单元包含若干存储元件,每个存储元件存储一位二进制代码。因此存储单元可存储一串二进制代码,这串代码称为存储字。这串代码的位数称为存储字长。

(2)地址寄存器MAR:存放地址,经过地址译码后找到所选的存储单元。MAR位数反应存储单元的个数,如4位MAR,则有24个存储单元

(3)数据寄存器MDR:用于暂存要从存储器中读/写的信息。MDR的位数=存储字长。如MDR16位,则每个存储单元可以存放16bit,即一个字(word)(字≠字节)的大小是16bit

(4)时序控制器逻辑:用于产生存储器操作需要的各种时序信号

注:在现代CPU中,MAR、MDR、Cache都是存在于CPU中的

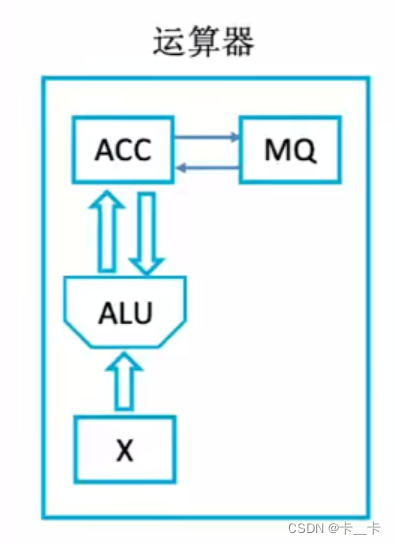

4.运算器

运算器的核心是算数逻辑单元ALU,其功能是进行算术、逻辑运算。(算术运算:加减乘除;逻辑运算:与或非)

运算器组成:

(1)若干通用寄存器。用于暂存操作数和中间结果。如:累加器ACC、乘商寄存器MQ、操作数寄存器X、变址寄存器IX、基址寄存器BR

①ACC:是运算器中既能存放运算前的操作数,又能存放运算结果的寄存器

②MQ:乘法运算时存放乘数、除法时存放商的寄存器

③X:此字母没有专指的缩写含义,可以用作任一部件名,在此表示操作数寄存器,即运算器中工作寄存器之一,用来存放操作数

④IX:存放存储单元在段内的偏移量

⑤BR:用来存放操作数或中间结果,以减少对存储器的访问次数

(2)程序状态寄存器PSW,也称标志寄存器。用于存放ALU运算得到的一些标志信息或处理机状态信息。如:结果是否溢出、有误产生进位

5.控制器

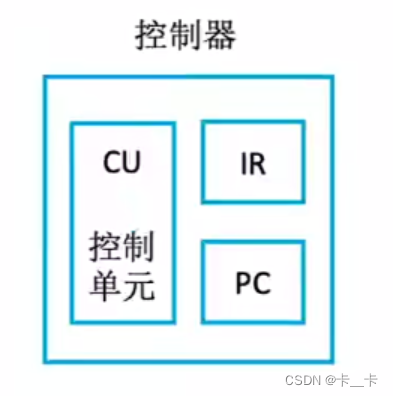

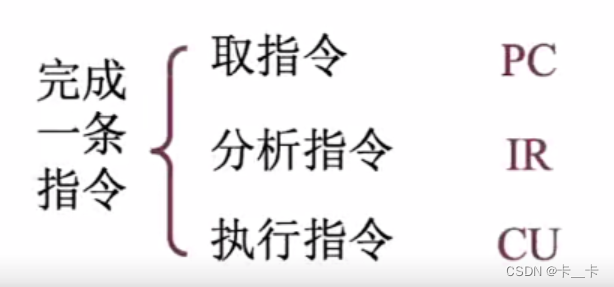

控制器组成:

(1)程序计数器PC:用来当前程序欲执行指令的地址,可以自动加1形成下一条指令的地址,它与MAR之间有一条直接通路

(2)指令寄存器IR:用来存放当前的指令,其内容来自MDR。指令中的操作码OP送至CU,用以分析指令并发出各种微操作命令序列;地址码Ad送往MAR,用以取操作数

(3)控制单元CU

控制单元是控制器的核心部件,其功能是产生微操作命令序列,即分析指令,给出控制信号

(四)中央处理器CPU

中央处理器(CPU)是计算机硬件的核心部件,主要由运算器和控制器组成。CPU和主存共同构成主机,除主机外的其他硬件装置(包括辅存)统称为外部设备,简称外设

(五)计算机的工作过程

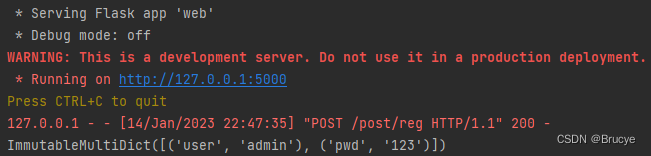

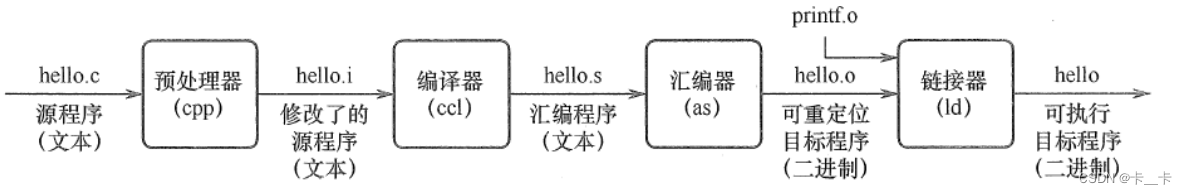

1.从源程序到可执行文件(C语言)

(1)预处理阶段(.c→.i)

预处理器对源程序中以字符#开头的命令进行处理,删除注释等。将.c输出为.i文件

(2)编译阶段(.i→.s)

编译器对预处理后的源程序进行编译,生成.s源程序

(3)汇编阶段(.s→.o)

汇编器将.s翻译成机器语言指令,把这些指令打包成一个称为可重定位目标文件.o

(4)链接阶段(.o→可执行)

链接器将多个可重定位目标文件和标准库函数合并为一个可执行目标文件,或简称可执行文件

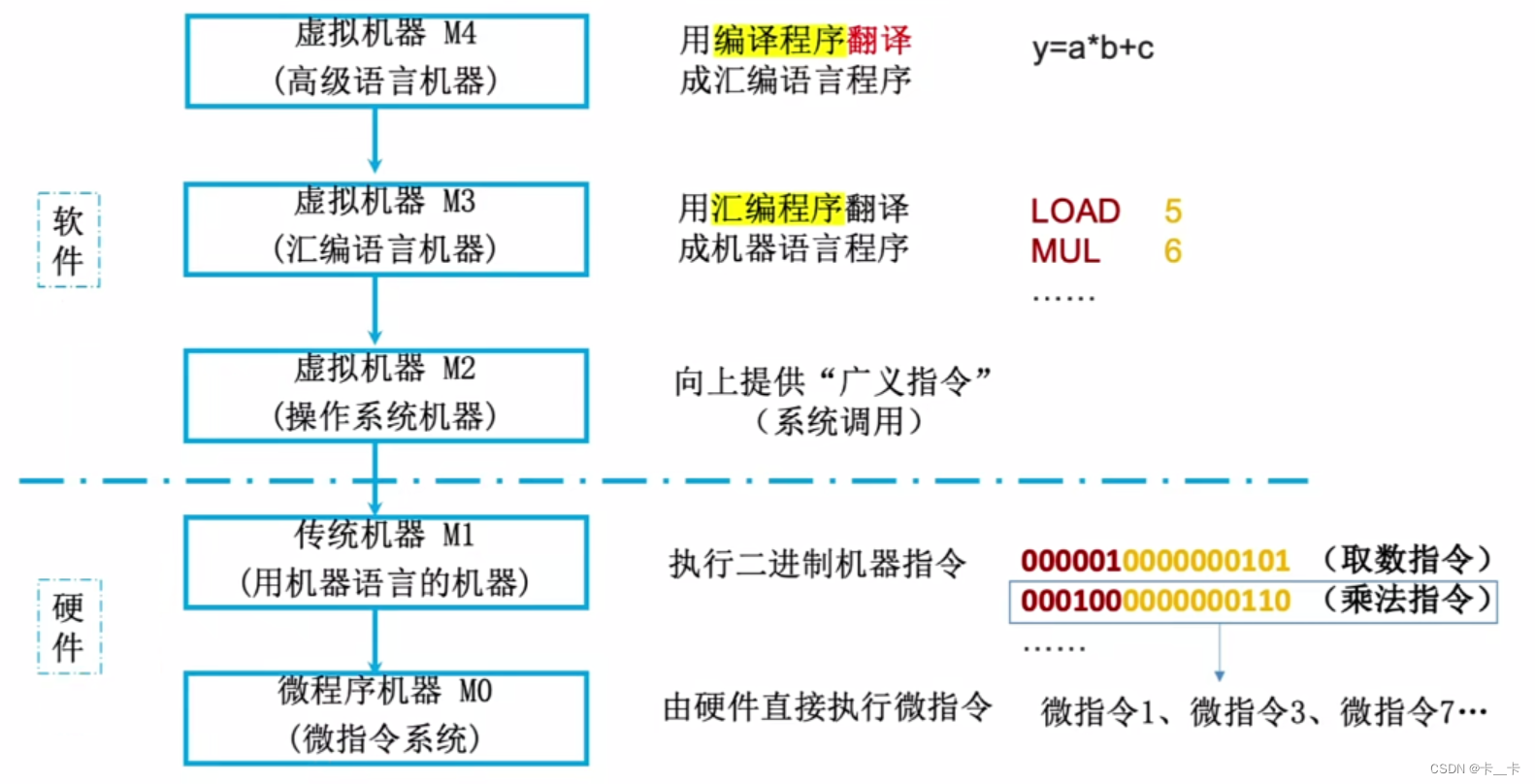

- 翻译包括编译、汇编、解释

①编译程序:将高级语言编写的源程序一次性全部翻译成汇编语言或机器语言,如果源程序不变再次运行不需要重新翻译。如C/C++

②汇编程序:将汇编语言翻译成机器语言

③解释程序:不需要提前编译,在运行程序时翻译一句执行一句,不生成目标程序,效率比较低。如JavaScript、python、shell

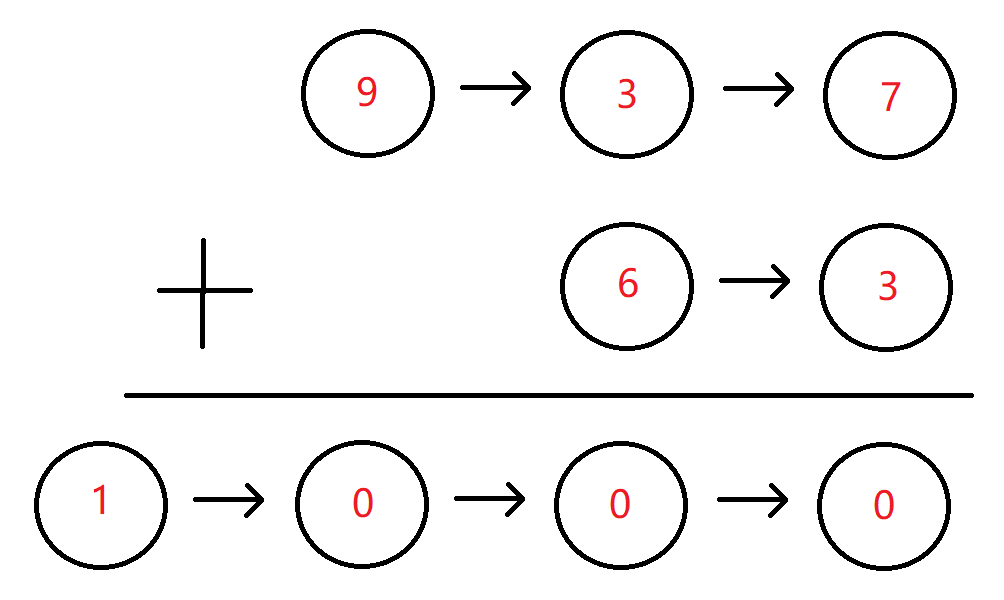

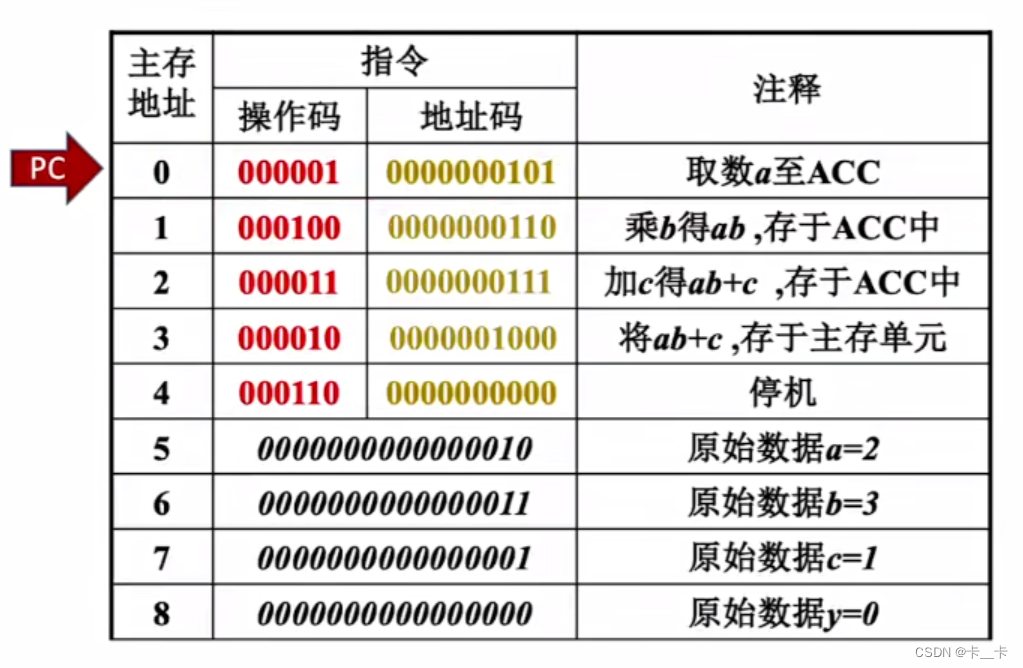

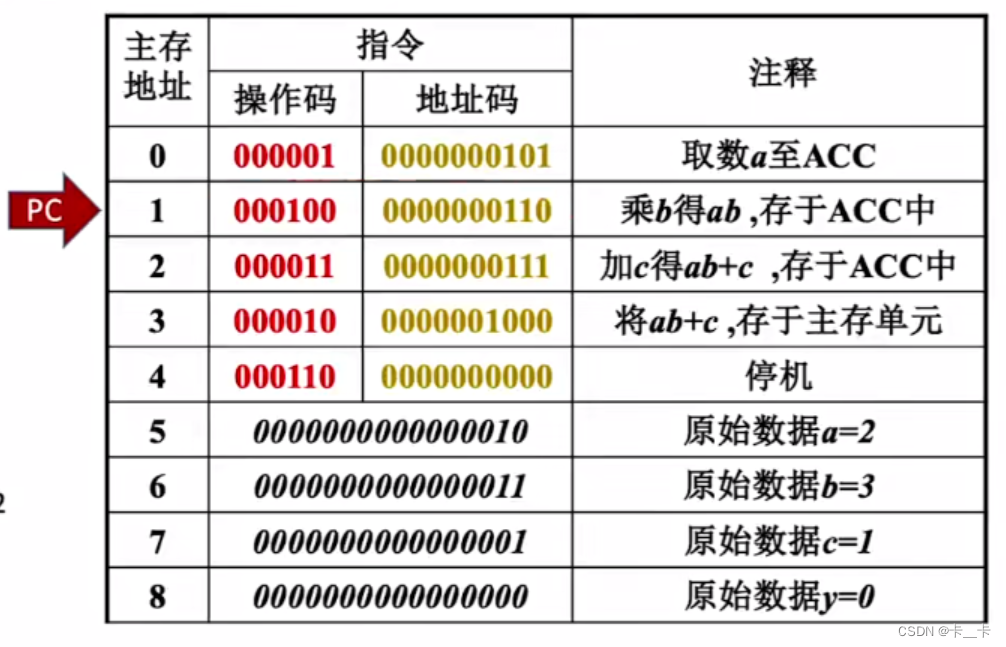

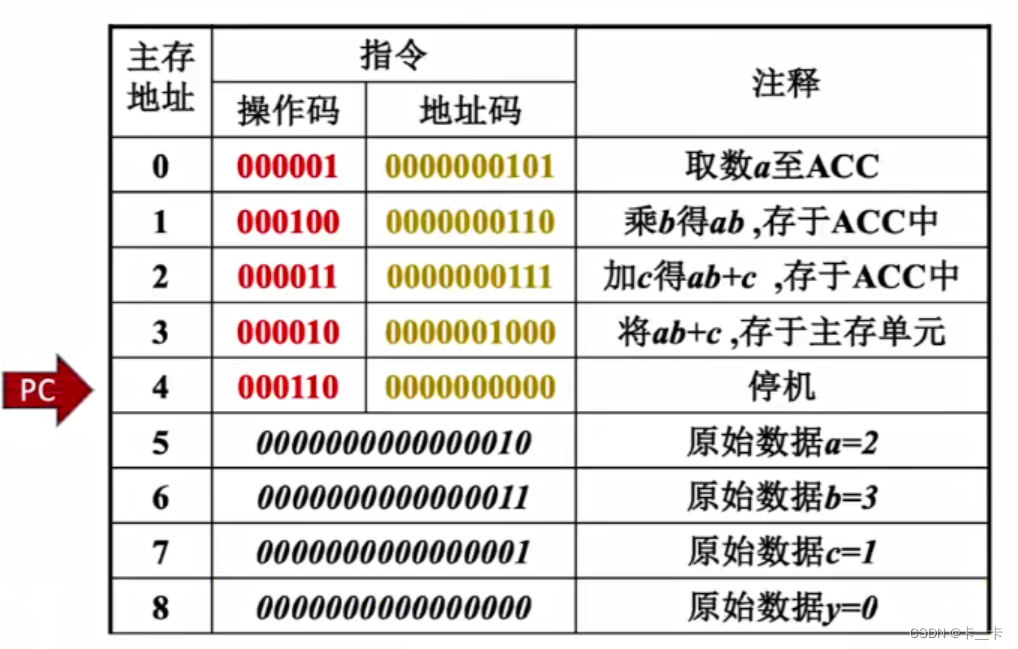

2.举例

int a=2,b=3,c=1,y=0;

void main(){

y=a*b+c;

}

编译后装入主存

在存储体中:

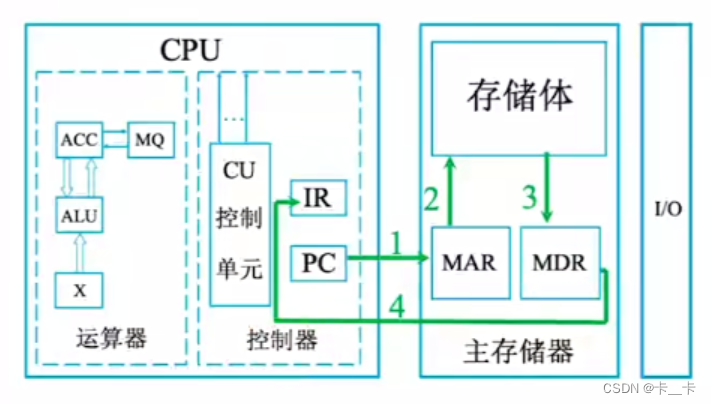

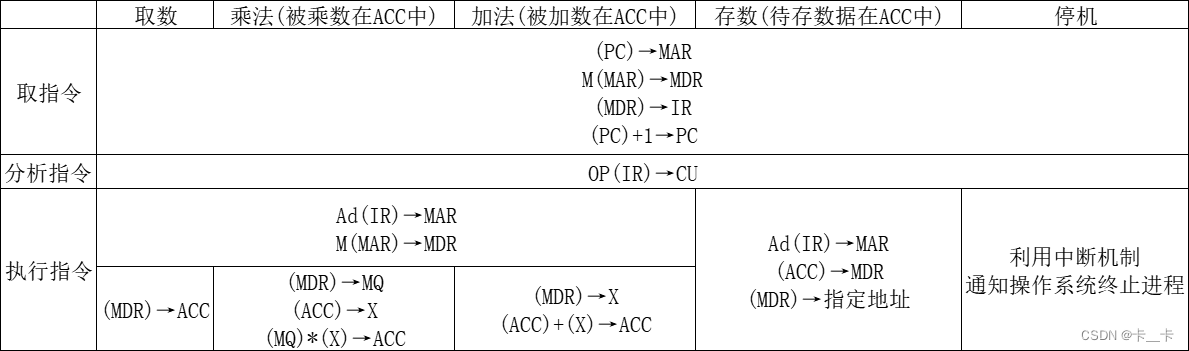

起初:PC指向第一条指令,(PC)=0

①PC指向的内容通过地址总线传送到MAR,使得(MAR)=0

即控制器向主存指明了现在要访问0号地址对应的数据,控制器通过控制总线说明此次要进行读操作。即(PC)→MAR

②③主存储器根据MAR记录的地址信息去存储体中找出0号地址对应的二进制数据,将数据放到MDR中。此时MDR中存放要执行的第一条指令。M(MAR)→MDR,(MDR)=00001 0000000101

注:

(MAR) 表示寄存器中的内容

M(MAR) →MDR 表示主存储器中MAR地址所指明的存储单元里的数据放到MDR中

④MDR中的指令通过数据总线放到IR,即(MDR)→IR,(IR)=00001 0000000101

【—以上为取指令阶段—】

取指令完成后(PC)+1→PC

⑤操作码00001被送到CU控制单元中,CU分析得知,这是“取数”指令,即OP(IR)→CU

注:OP(IR)表示IR中的操作码

【—以上为分析指令阶段—】

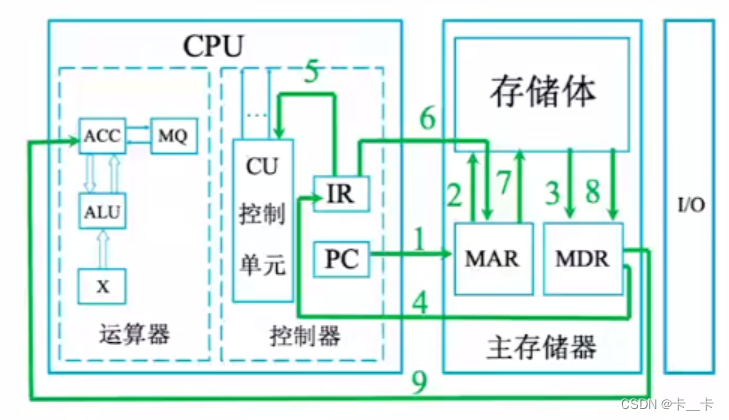

⑥将指令的地址码(0000000101)送到MAR。即Ad(IR)→MAR,使(MAR)=5

注:Ad(IR)表示IR中的地址码

⑦⑧主存储器根据MAR指明的地址在存储体中找到5号单元的数据放入MDR,即M(MAR)→MDR,使(MDR)=0000000000000010=2

⑨在控制单元的指挥下,MDR的数据被放到ACC中,使得ACC中存放了a的值2,即(MDR)→ACC。此时(ACC)=2,(PC)=1

【—以上为取数阶段—】

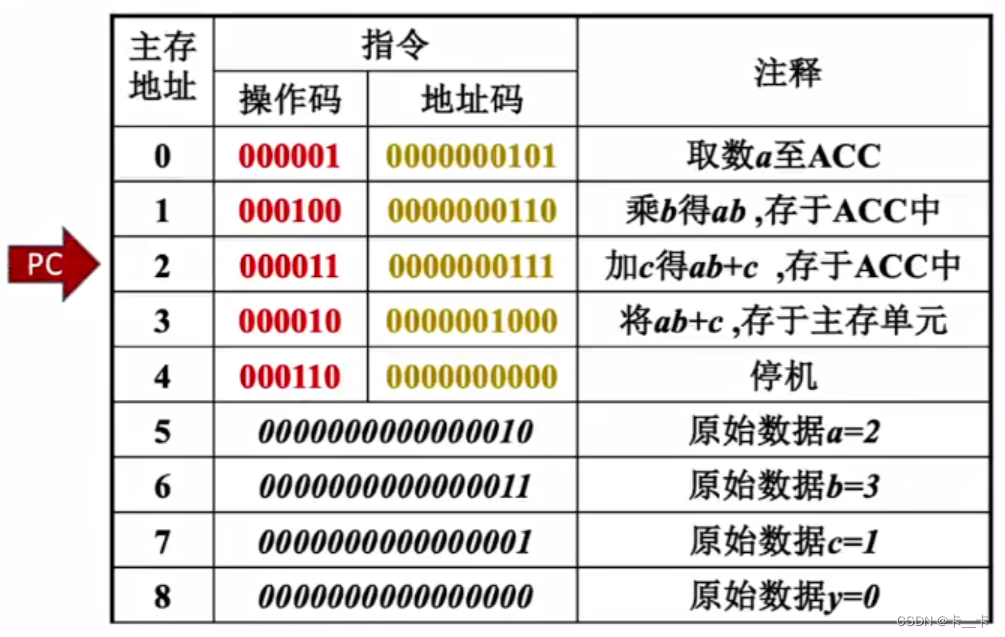

同理

①(PC)→MAR

②③M(MAR)→MDR

④(MDR)→IR,(PC)+1→PC

⑤OP(IR)→CU,得知是乘法指令

【⑥-⑪是乘法指令操作】

⑥Ad(IR)→MAR,此时(MAR)=6

⑦⑧M(MAR)→MDR,此时(MDR)=0000000000000011=3

⑨(MDR)→MQ,此时(MQ)=0000000000000011=3

⑩(ACC)→X,将被乘数a=2放入操作数寄存器中,即(X)=2

⑪CU通过控制线告诉ALU进行乘法运算,将计算结果6放入ACC(如果乘得的数值很大,需要MQ辅助存储),即(MQ)*(X)→ACC。此时(ACC)=6,(PC)=2

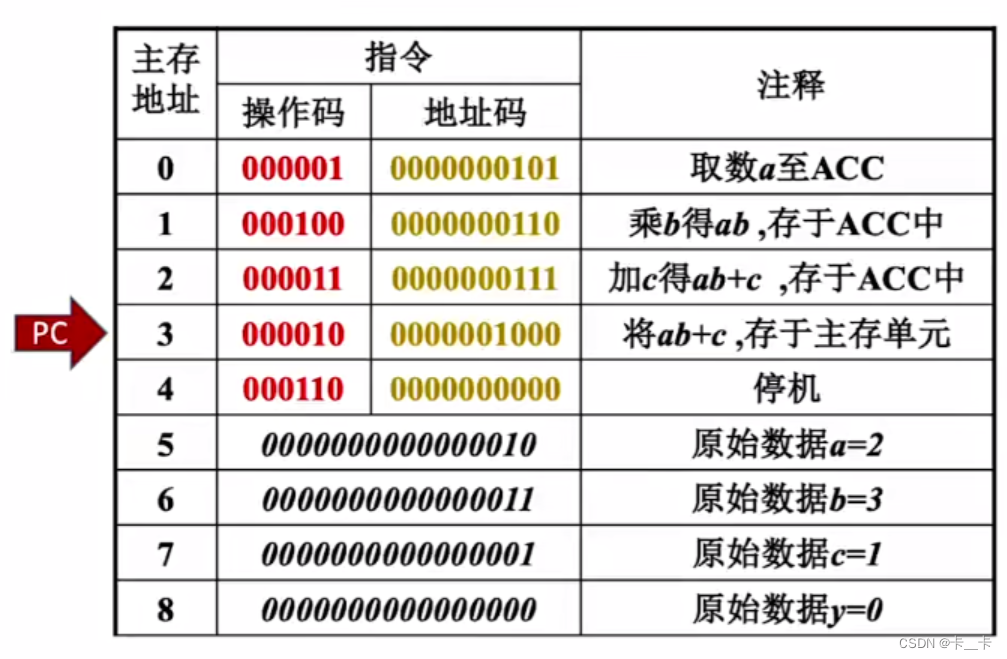

继续

PC=2

①(PC)→MAR

②M(MAR)→MDR

③MDR→IR,(PC)+1→PC

④OP(IR)→CU,得到加法指令

⑤Ad(IR)→MAR,此时(MAR)=7

⑥M(MAR)→MDR,此时(MDR)=1

⑦(MDR)→X,此时(X)=1

⑧(ACC)+(X)→ACC,此时(ACC)=6+1=7

PC=3

(PC)→MAR

M(MAR)→MDR

MDR→IR,(PC)+1→PC

OP(IR)→CU,得到存数指令

Ad(IR)→MAR,此时(MAR)=8

(ACC)→MDR,此时(MDR)=7

主存储器根据MAR的地址把MDR的数据放入相应的位置中,即(MDR)→地址为8的存储单元,使得y=7

PC=4

(PC)→MAR

M(MAR)→MDR

(MDR)→IR,(PC)+1→PC

OP(IR)→CU,得知是停机指令

利用中断机制通知操作系统终止进程

【总结】

四.计算机系统层次结构

M4:高级语言机器(执行高级语言)

M3:汇编语言机器(执行汇编语言)

M2:操作系统机器(向上提供广义指令)

M1:传统机器(执行机器语言指令)

M0:微程序机器(执行微指令)

五.计算机的性能指标

1.机器字长

计算机进行一次整数运算所能处理的二进制数据位数

2.数据通路带宽

数据总线一次所能并行传送信息的位数

3.主存容量

主存储器所能存储信息的最大容量

4.运算速度

(1)吞吐量:系统在单位时间内处理请求的数量

(2)响应时间:从用户向计算机发送一个请求,到系统对该请求做出相应并获得所需结果的等待时间

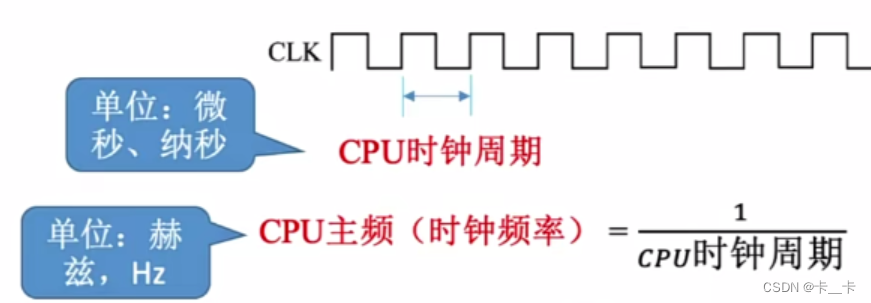

(3)主频(CPU时钟频率):机器内部主时钟频率/CPU内数字脉冲信号振荡的频率,单位Hz。主频越高,完成指令的一个执行步骤所用的时间越短,指令执行的速度越快

(4)CPU时钟周期:主频的倒数,是CPU中最小的时间单位,执行指令的每个动作至少需要1个时钟周期

(5)CPI(Clock Cycle Per Instruction):执行一条指令所需的时钟周期数

(6)IPS(Instructions Per Second):每秒执行多少条指令

(7)CPU执行时间:一个程序所花费的时间

(8)MIPS(Million Instruction Per Second):每秒执行多少百万条指令

(9)FLOPS(Floating-point Operations Per Second):每秒执行多少次浮点运算

(10)MFLOPS(Mega Floating-point Operation Per Second):每秒执行多少百万次浮点运算

(11)GFLOPS(Giga):每秒执行多少十亿次浮点运算

(12)TFLOPS(Tera):每秒执行多少万亿次浮点运算

5.相关公式(不考虑单位时)

(1)CPU执行时间=时钟周期数×时钟周期=时钟周期数/时钟频率

(2)时钟周期数=CPI×指令条数=1/时钟频率

(3)1=时钟频率×CPI×指令条数

(4)CPU执行时间=CPI×指令条数×时钟周期

(5)MIPS=指令数/CPU执行时间=指令数/(时钟周期数×时钟周期)=指令数/(CPI×指令数×时钟周期)=1/(CPI×时钟周期)=时钟频率/CPI

(6)执行一条指令需要的时间=CPI×CPU时钟周期

(7)CPI×IPS=时钟频率(主频)

注:单位换算

MIPS=指令条数/(执行时间×106)

MFLOPS=浮点操作次数/(执行时间×106)

6.基准程序

用来进行性能评价的一组程序,能够很好地反应机器在运行实际负载时的性能,可以通过在不同机器上运行相同的基准程序来比较在不同机器上的运行时间,从而测评其性能。

![[Python+Django]Web学生信息管理系统数据库设计及系统实现](https://img-blog.csdnimg.cn/b215a17c6c594ff98baac085dc3ba12a.png)

![[激光原理与应用-63]:激光器-光学-探测光、泵浦光和种子光三种光的区别](https://img-blog.csdnimg.cn/img_convert/c4dfd2c7cbbee4df88d949be656ed4d3.png)