0.什么是Modelsim?

Modelsim是一个支持多语言的仿真环境,比如我知道的Verilog和VHDL语言都可以在里边使用,这俩都是硬件描述语言;

即就是个软件,你可以用Verilog语言来写代码,然后编译,仿真出波形.....

软件图标长这样:

1.什么专业学习它,以及它可以干什么?

我知道的:计算机科学与技术本科阶段是要学的,然后体系结构的硕士也可以学习,IC设计类专业那就更要学(另外如果是萌新要了解IC的话,可以看这个知乎链接);

B站上陈硕大佬讲了几节课,也可以看看,新手勿进,B站链接;

2.你应该怎么学习?

西安交大的这个36页的讲义值得一看;

南京大学的这个实验指导书更是值得一看,比前者更全;

牛客有大量练习Verilog的题目,从入门到进阶都是不错,请点击链接;

要想有更深入理解,看书是必要的,推荐一下《Verilog HDL高级数字设计》一书;

如果英语不错,请看ModelSim User’s Manual;

再往后,就请联系学校老师,看能不能进入实验室做些什么,一来可以精进技能打打比赛,二来为将来升学就业打下基础,切忌闭门造车;

3.Modelsim软件下载:

点击百度网盘链接下载;

下好后,移动到某个僻静的位置,解压,双击exe,一路next即可,如果弹出是否创建快捷方式,同意即可。具体可以看这个知乎链接,讲的不错。

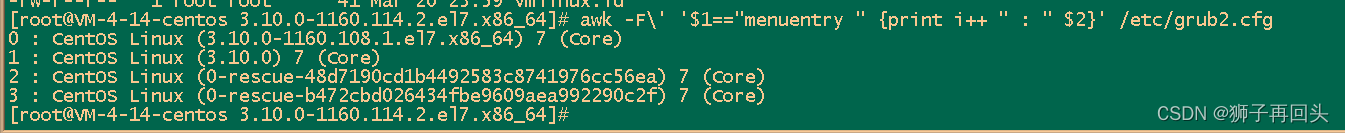

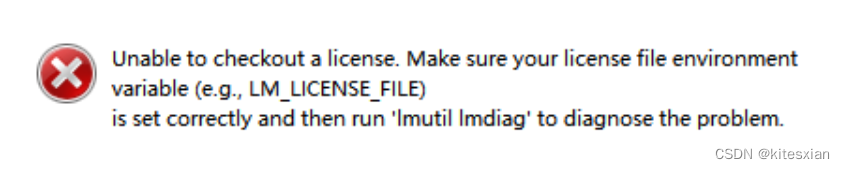

如果“一切顺利”的话,你大概会遇到这么一个问题:

解决方法一:

那个知乎链接中说的开头复制粘粘破解文件那一步,那两个mg开头的文件先不要复制粘粘,等到变量名修改完之后再替换。在系统环境变量中把变量名MGLS_LICENSE_FILE改成LM_LICENSE_FILE

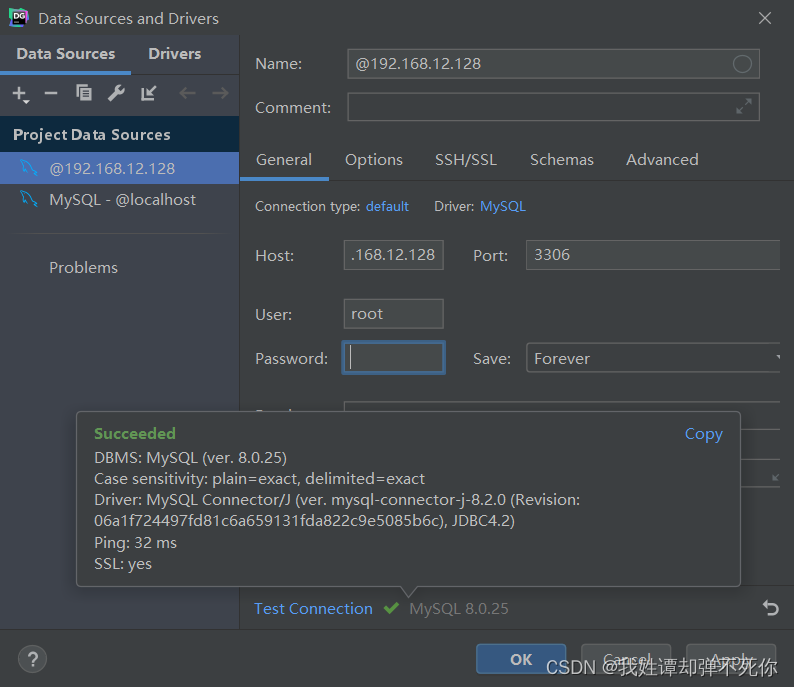

法一不行的话,请看法二:

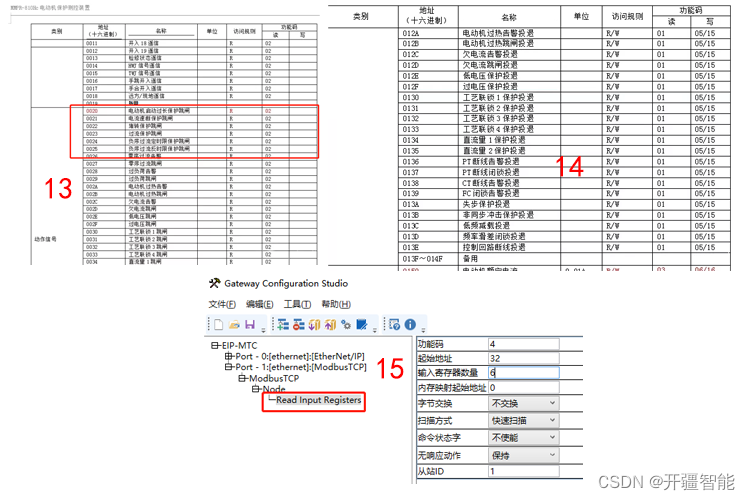

链接,即:环境变量有问题,你看下你的环境变量的值是不是下图这样子,变量名以LM开头,它的值以LICENSE.TXT结尾。如果不是,请更改你的环境变量;

![]()

法二都不行,你就别折腾电脑了,去买个正版......

4.实现一个与门:

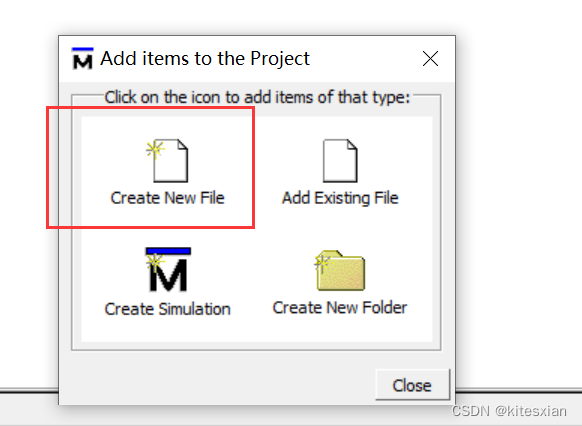

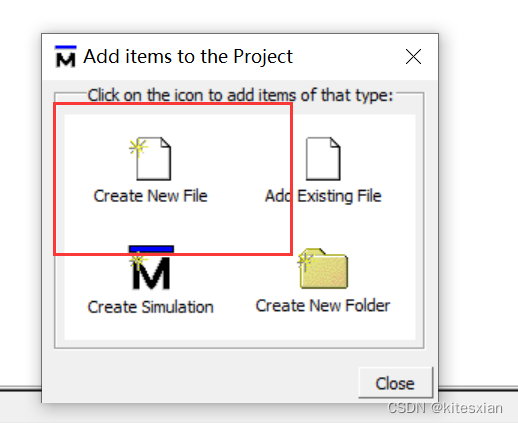

New-File-Project,依次点击;

再来一个:

然后close;

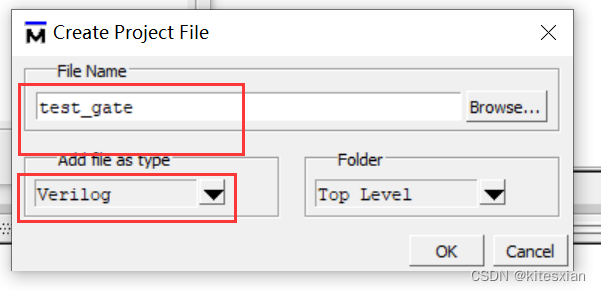

此时你得到了两个文件,都是问号,你双击编辑它,或者右键然后Edit也可以;

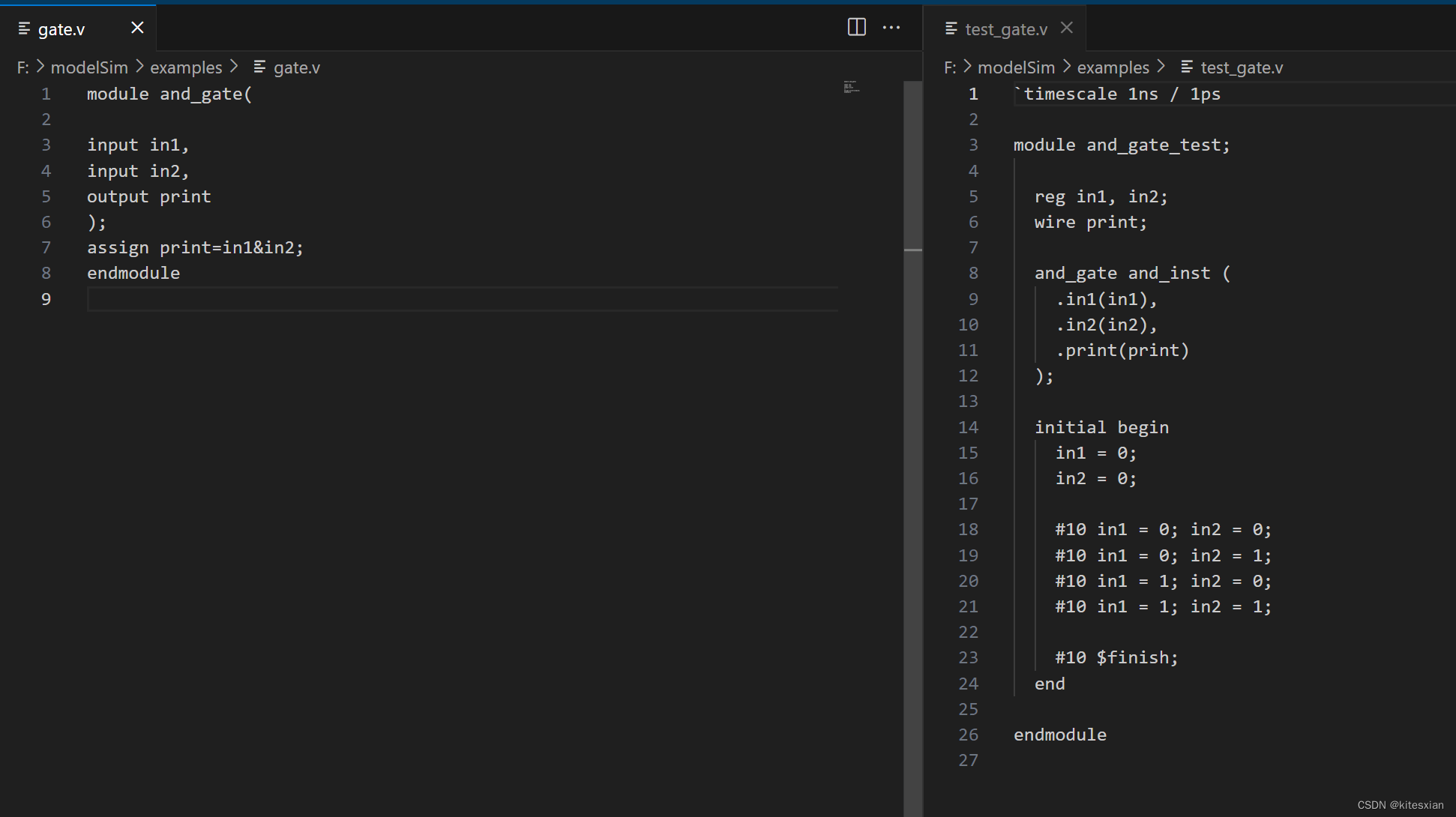

源代码在下边;

【注】:我是在vscode中编辑代码的,你可以直接在Modelsim中写代码;

源代码:

module and_gate(

input in1,

input in2,

output print

);

assign print=in1&in2;

endmodule

`timescale 1ns / 1ns

module and_gate_test;

reg in1, in2;

wire print;

and_gate and_inst (

.in1(in1),

.in2(in2),

.print(print)

);

initial begin

in1 = 0;

in2 = 0;

#10 in1 = 0; in2 = 0;

#10 in1 = 0; in2 = 1;

#10 in1 = 1; in2 = 0;

#10 in1 = 1; in2 = 1;

#10 $stop;

end

endmodule

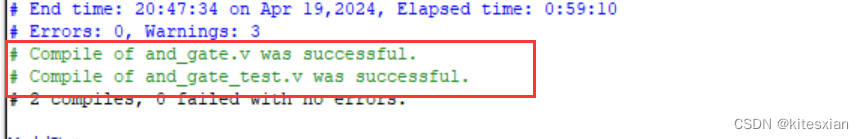

右键你写好的文件,然后像上图一样(Compile All),如果文件从问号变为了对号,说明编译成功了(你也可以看下边):

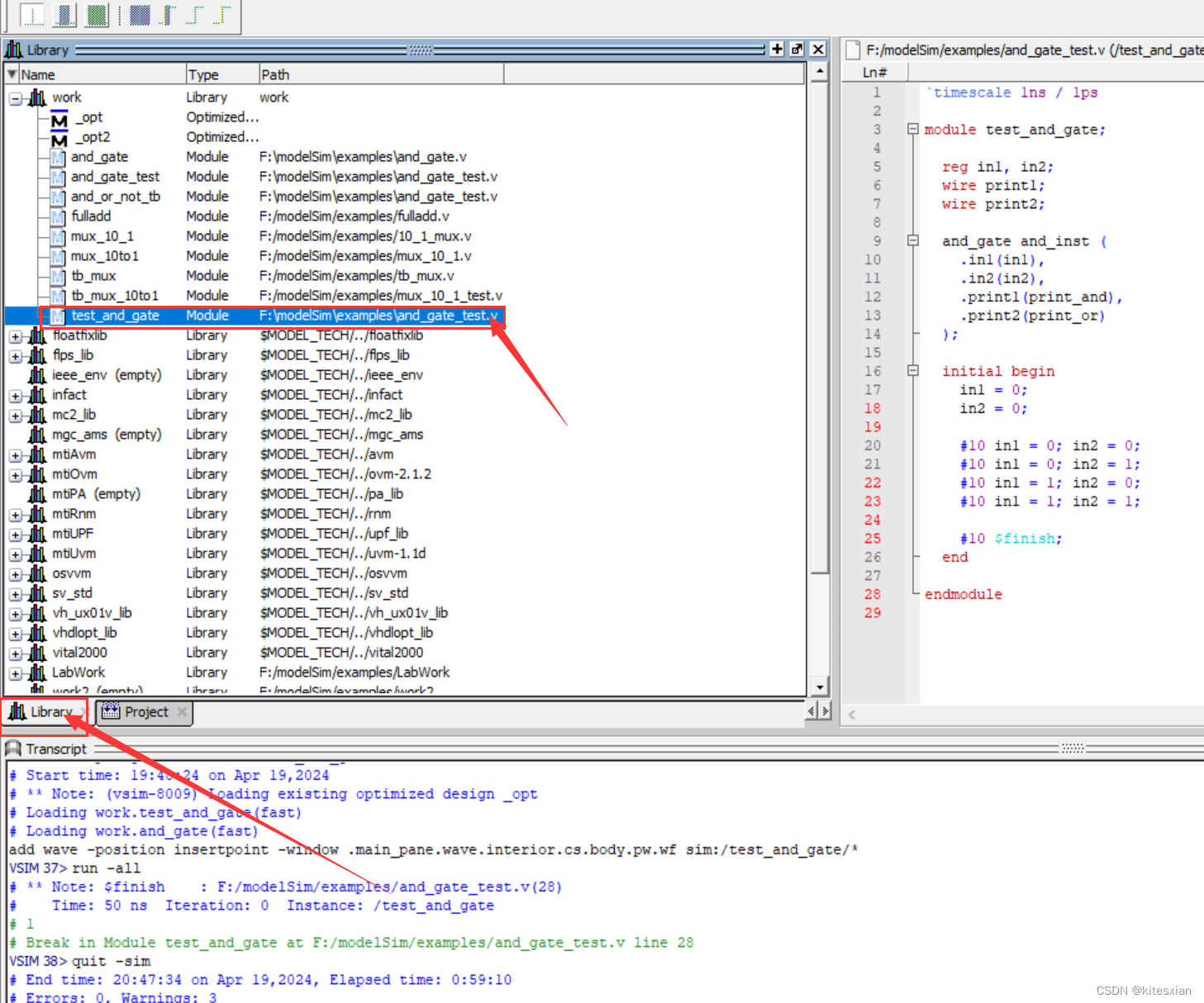

然后,点击底部的Library:

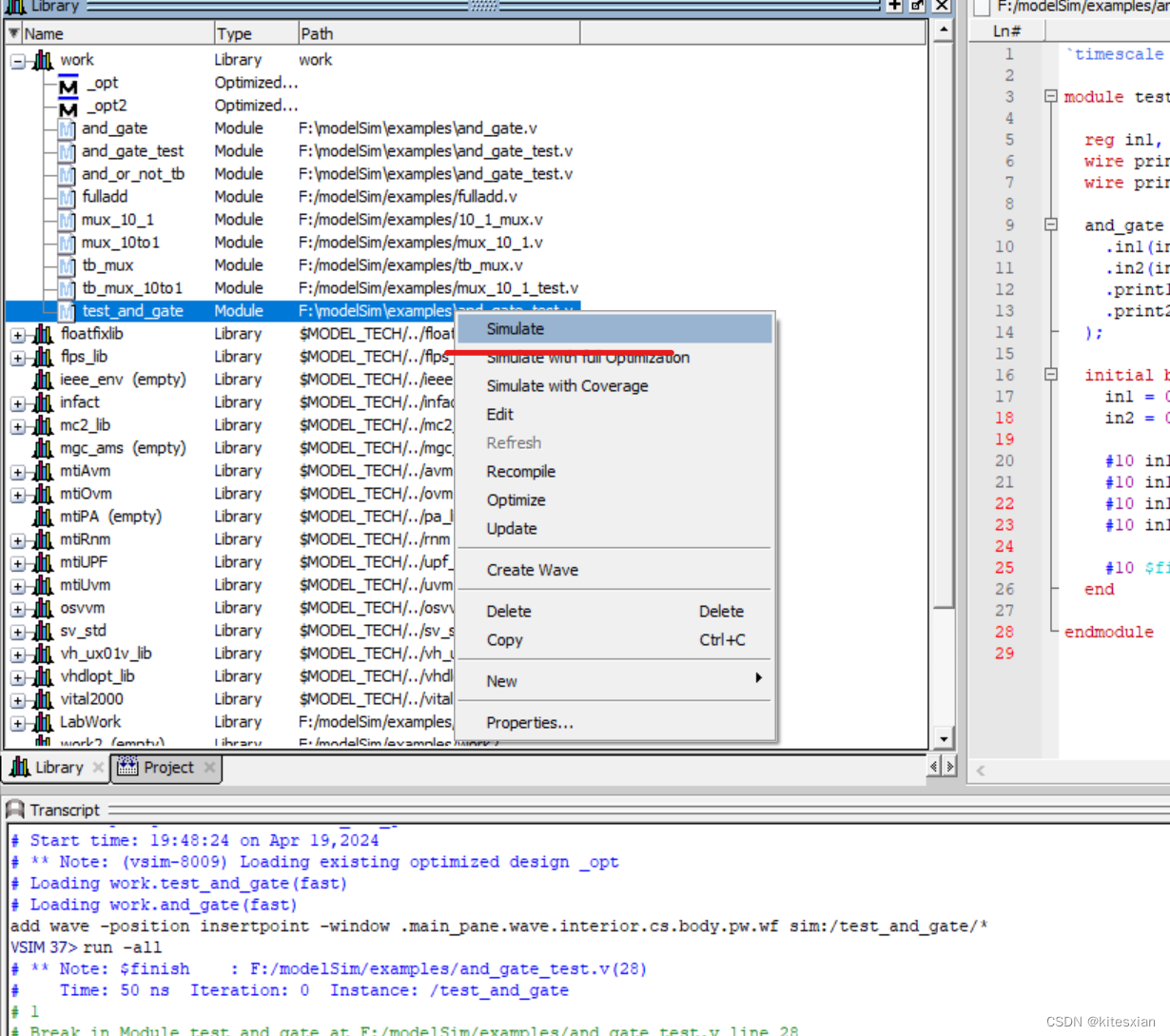

右键你的测试文件(有timescale的那个文件);

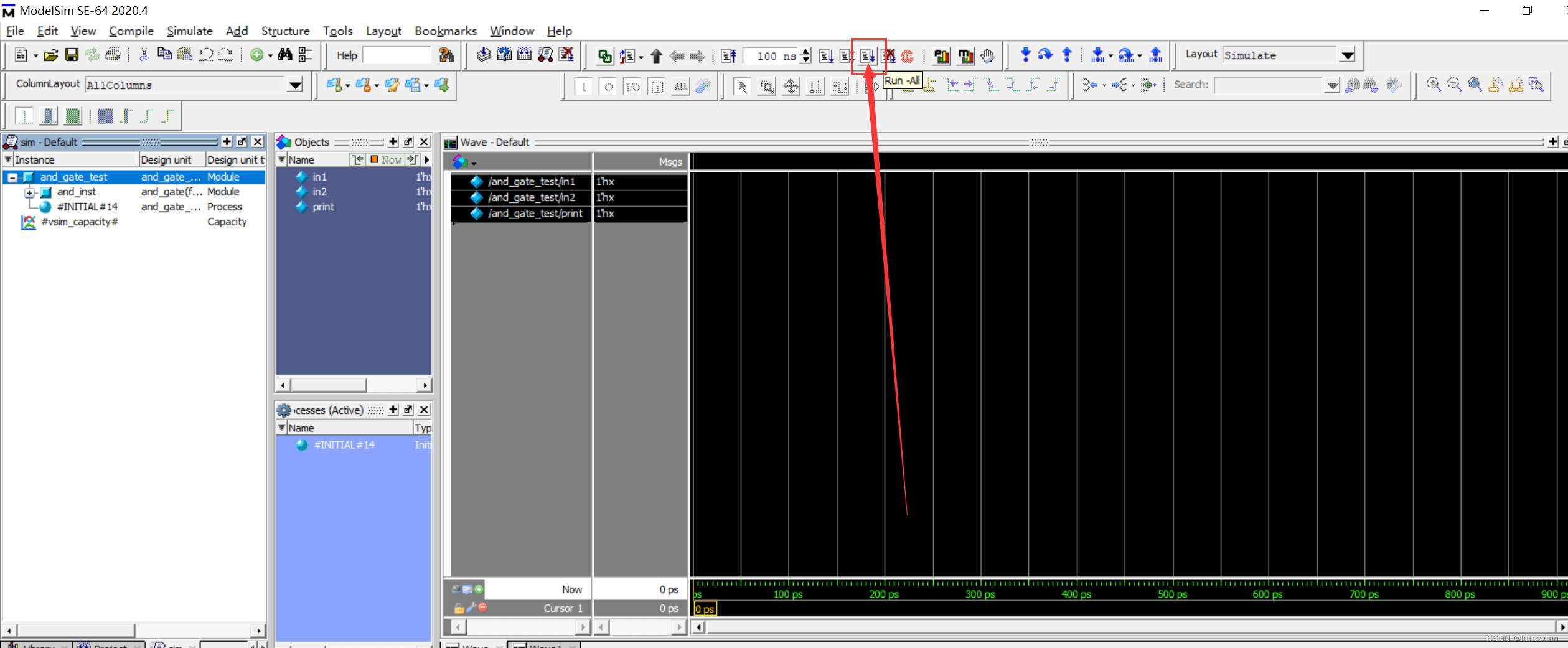

点击Simulate后会进入下图;

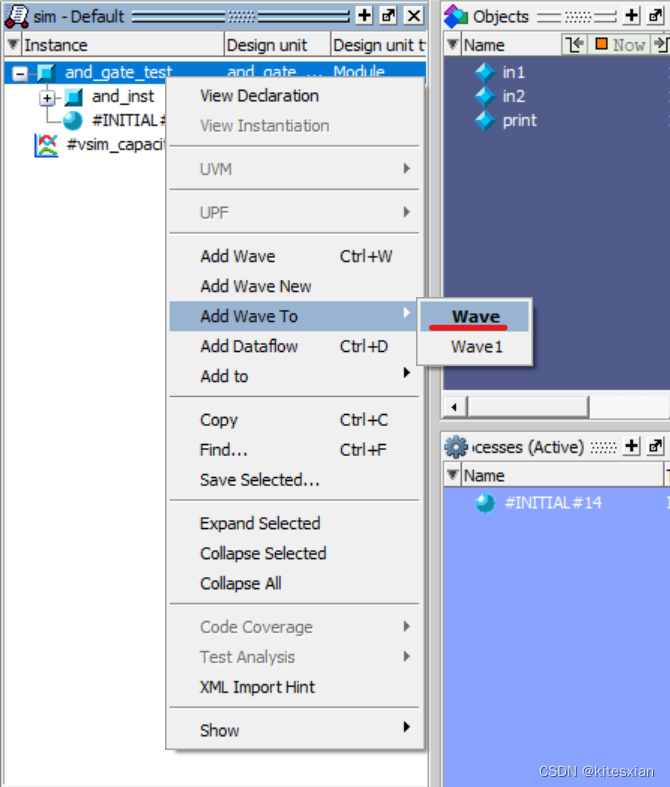

右键点击箭头所指文件:

【注】:如果出来弹窗问你是否要quit?点击否;

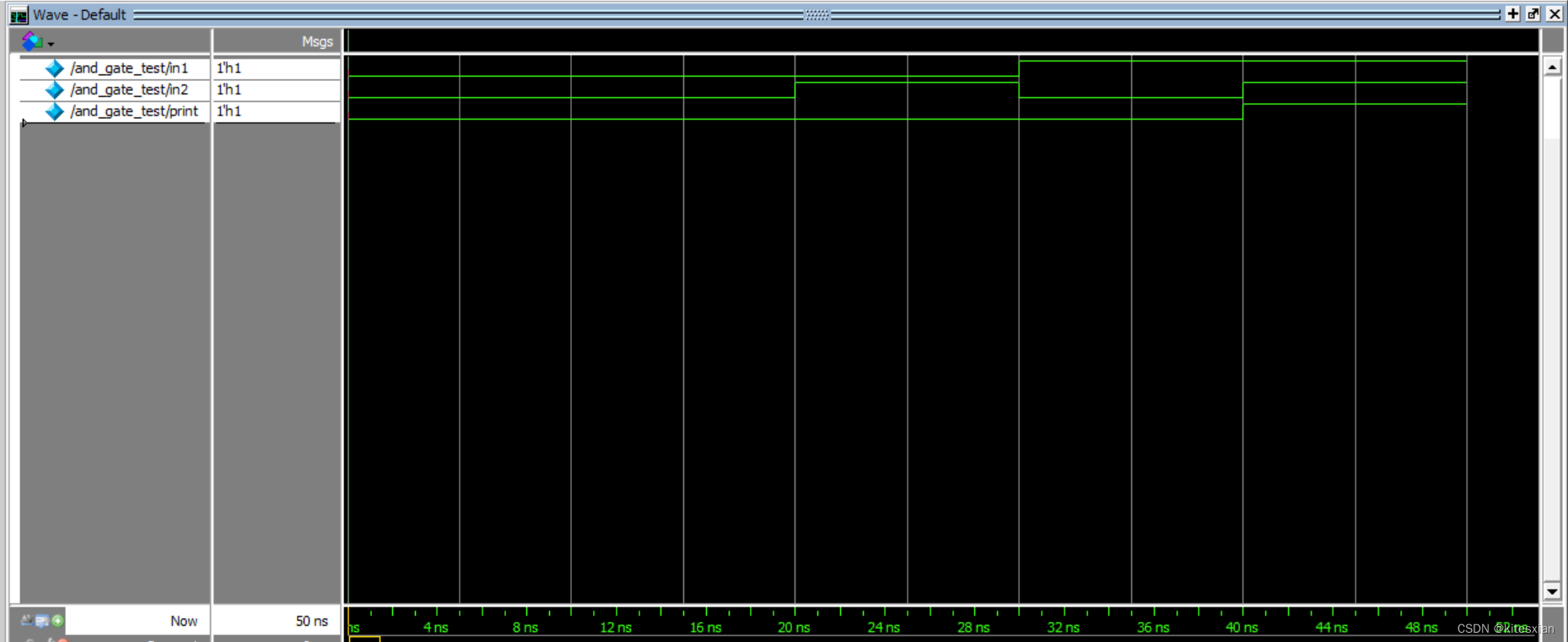

你应该可以看到波形了,与门是全为真结果为真,反之为假;

怎么退出仿真波形呢?

看到下面这个transcript了嘛?

输入quit -sim回车即可退出;

关闭仿真也可以点击菜单栏中的End Simulation而不去在命令行中输入quit -sim,如下:

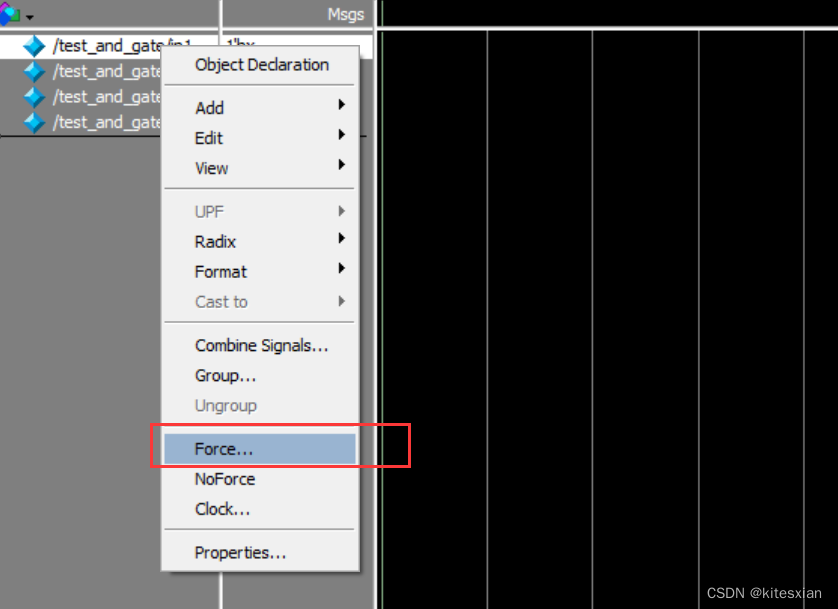

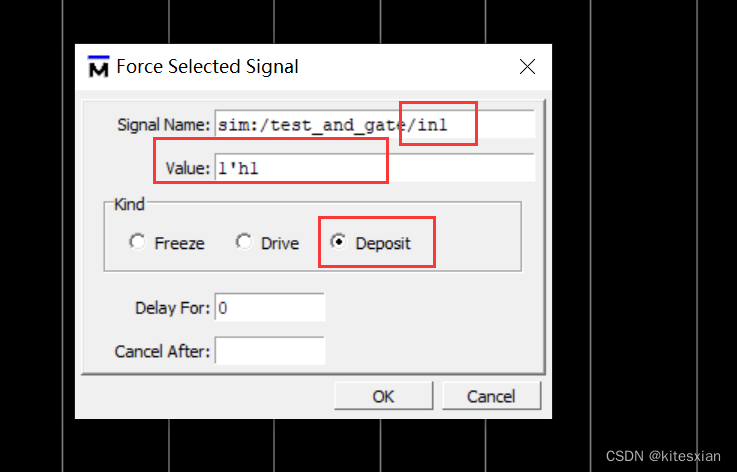

另外一个补充的点就是你可以直接对于变量赋值(在你右键Add Wave之后):

赋值后再点击Run;

赋值后再点击Run;

5.写在最后:

以上都基于我浅薄的理解,如有不对之处,请评论区指正,感谢。

6.参考链接:

链接1

链接2