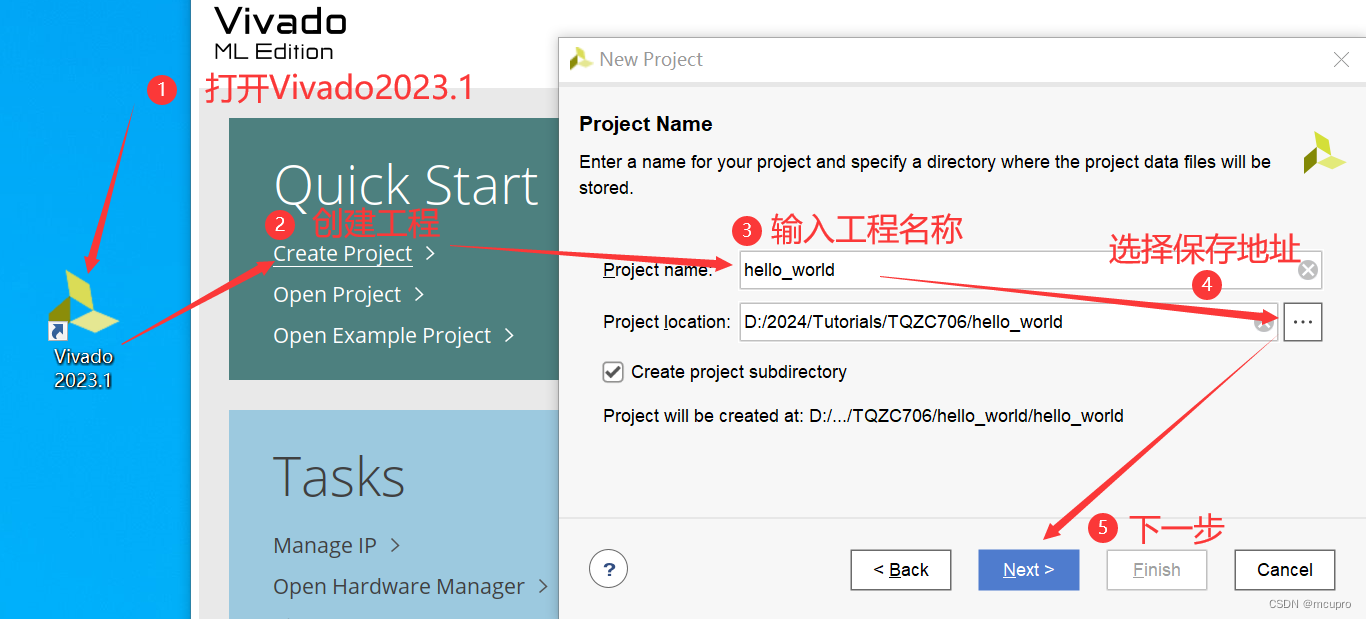

打开Vivado2023.1-->创建工程-->输入工程名称-->选择保存地址-->下一步

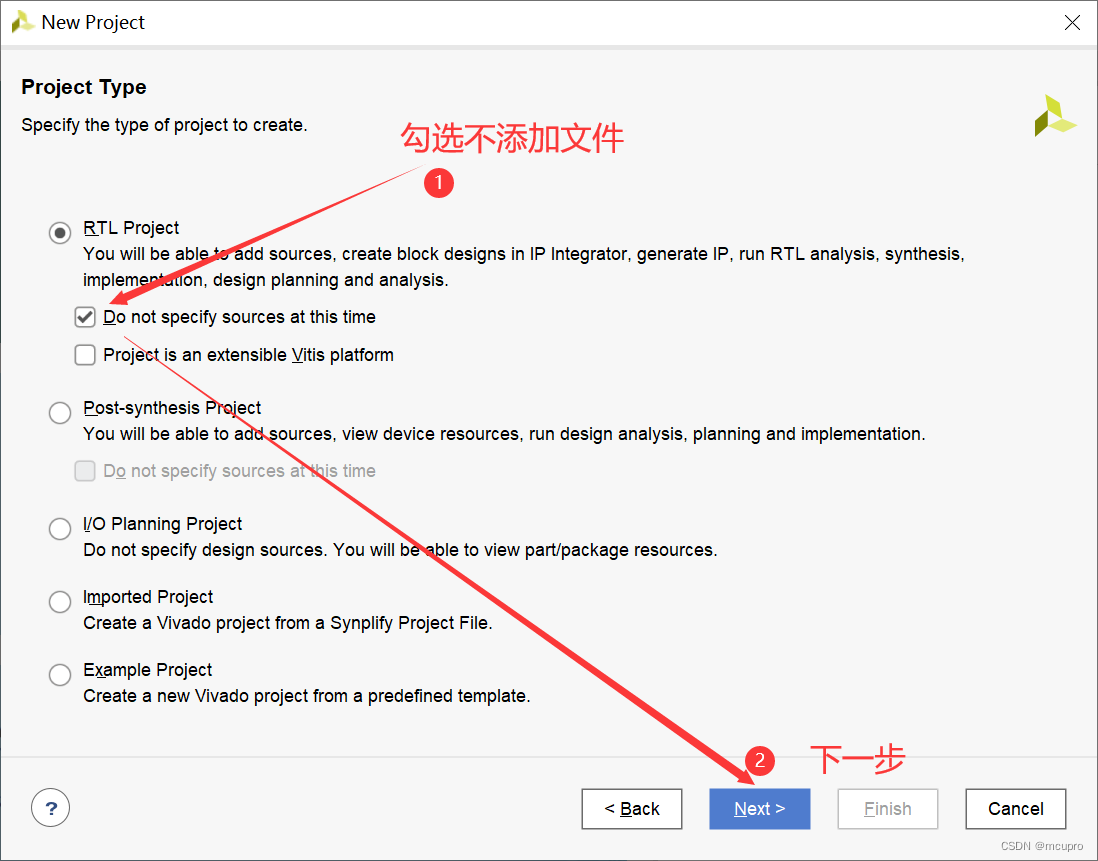

勾选不添加文件-->下一步

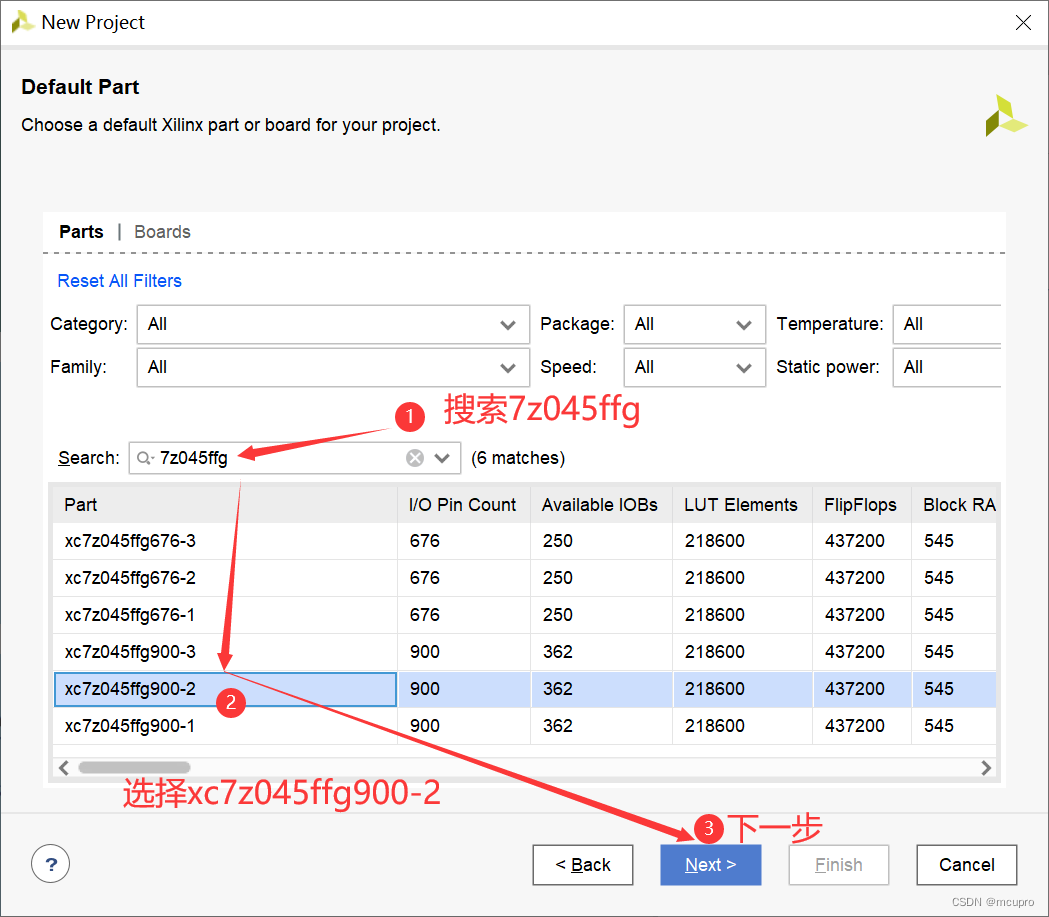

搜索7z045ffg-->选择xc7z045ffg900-2-->下一步,finish完成工程创建

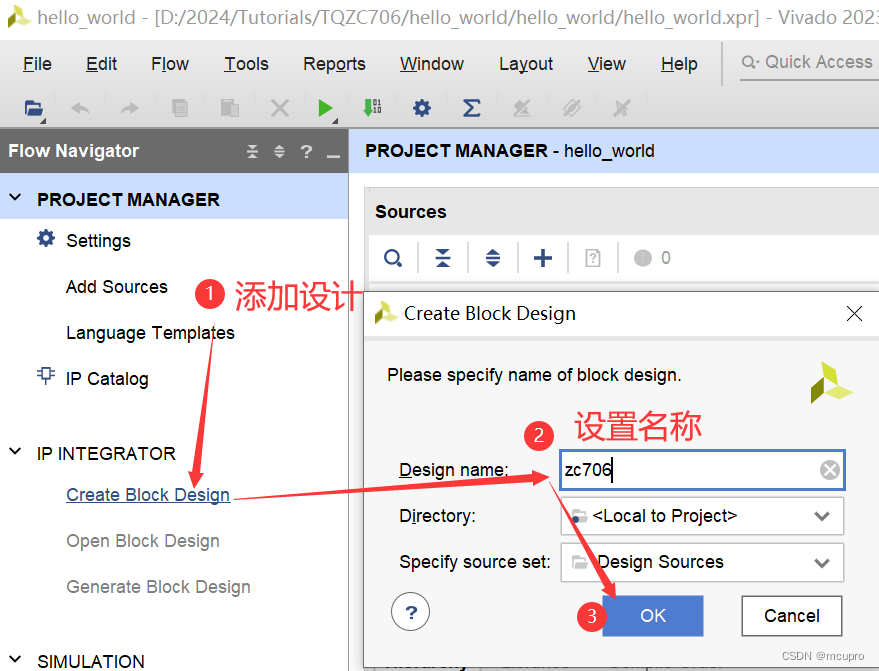

添加设计-->设置名称-->OK

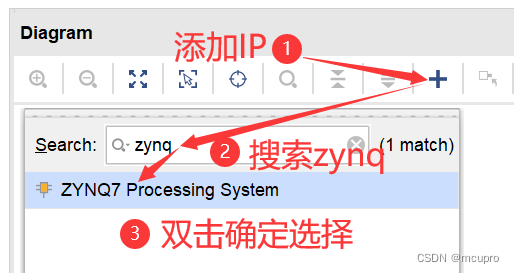

添加IP-->搜索zynq-->双击确定选择

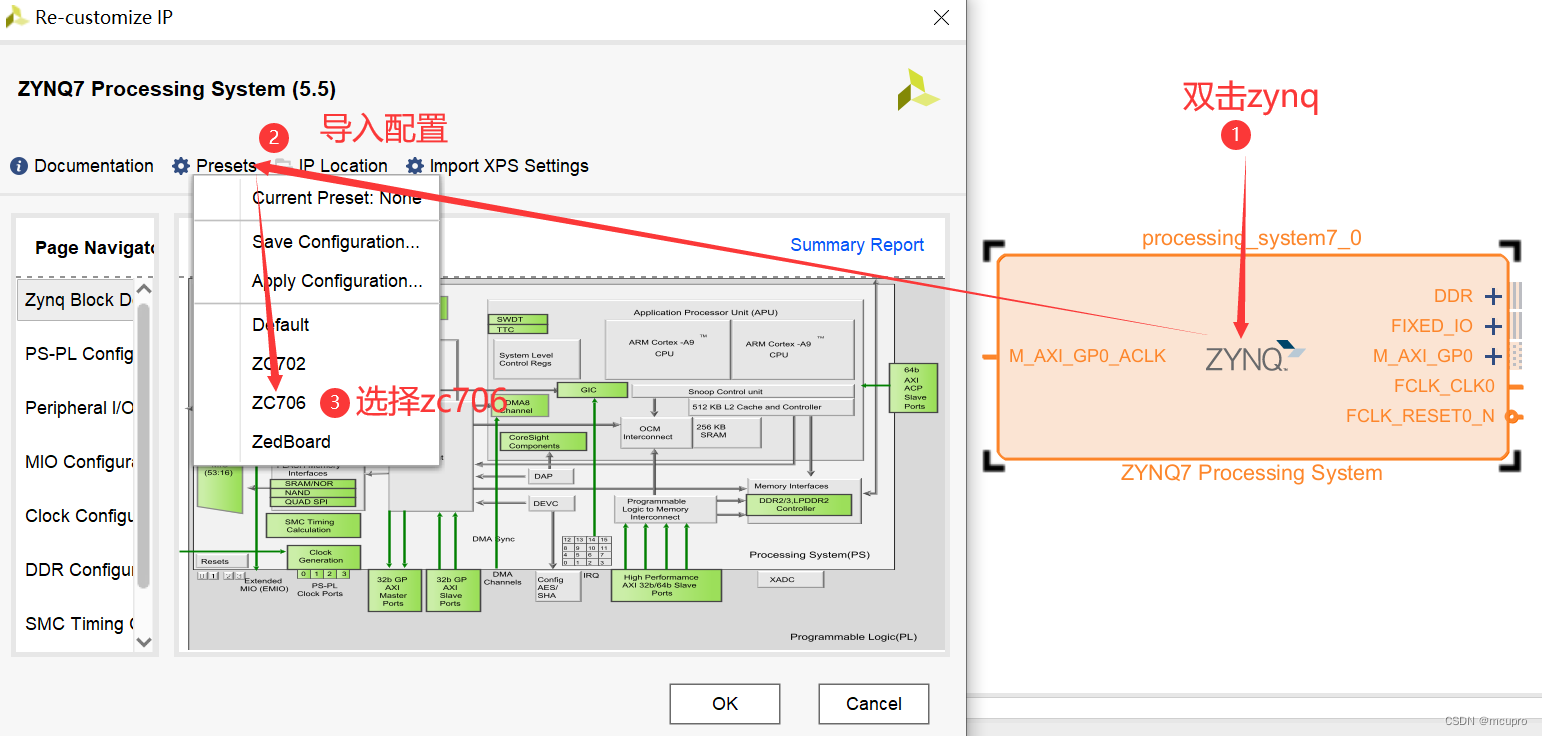

zynq是PS端的控制器,添加了zynq核后可以联动PS与PL共同工作。zynq中保存了PS的配置,单独使用PS端时也需要对其进行配置。本例程单独使用PS端通过串口打印信息,所以需要对zynq进行配置。我们的开发板完全兼容官方的zc706,配置可以使用官方的配置,进行一键导入。

双击zynq-->导入配置-->选择zc706-->OK

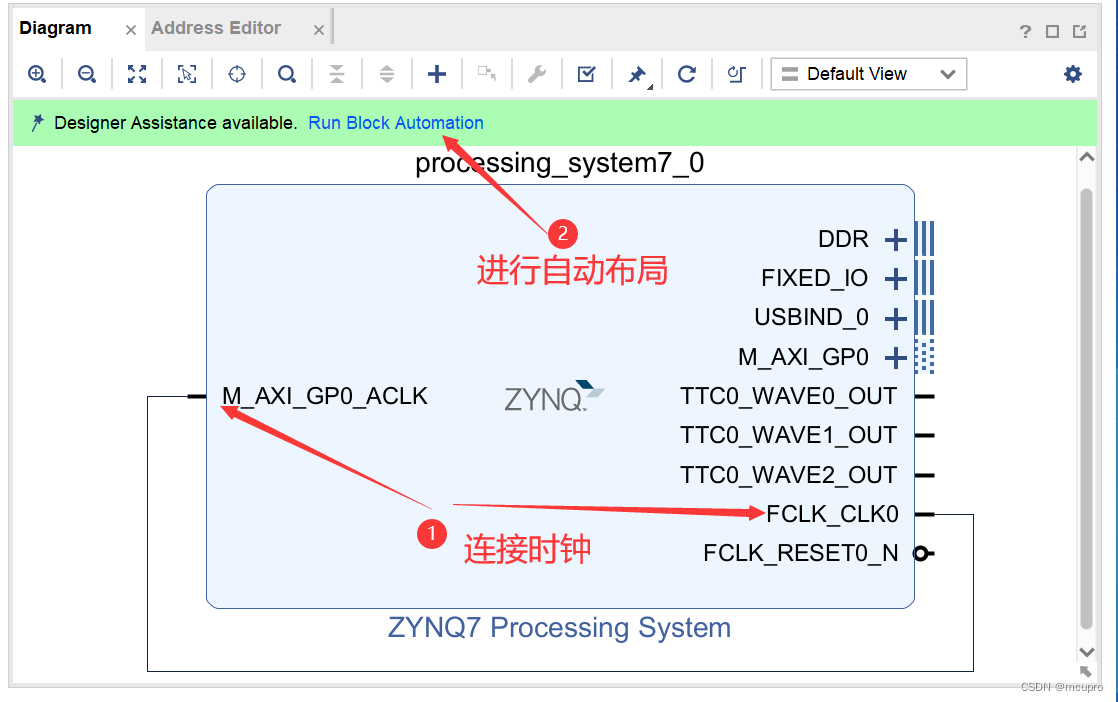

把模块的时钟首位相连,在进行自动布局-->OK

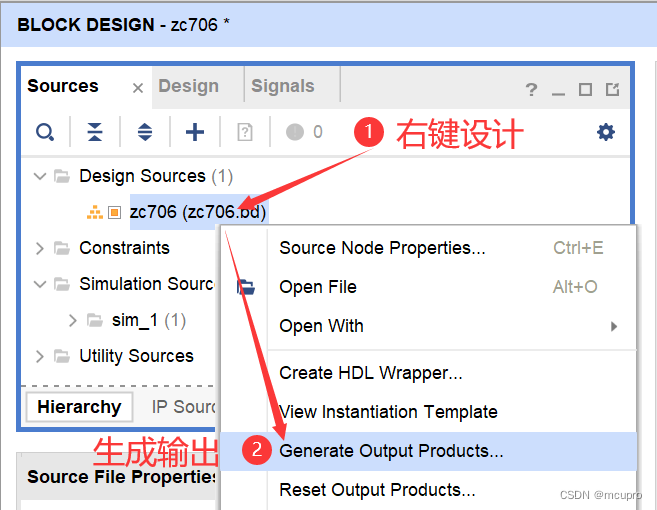

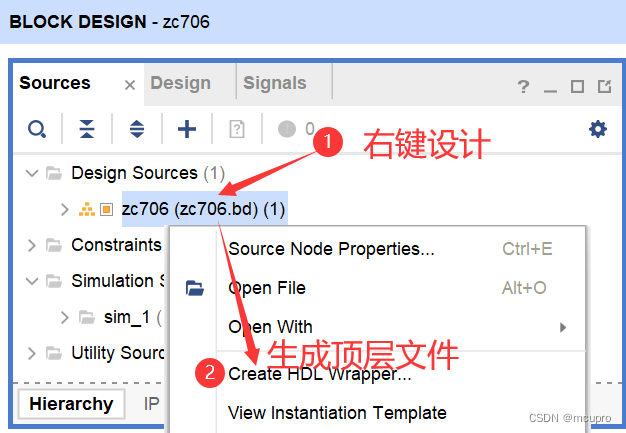

创建block design时产生的是bd文件,而vivado编译的是 .v 文件,所以需要把bd文件转换为 .v。通过下面这两步可以把bd转化为.v文件,generate output product 可以生成bd下一层的顶层,create HDL warpper可以生成bd上一层的顶层。

右键设计-->生产输出-->Generate

右键设计-->生成顶层

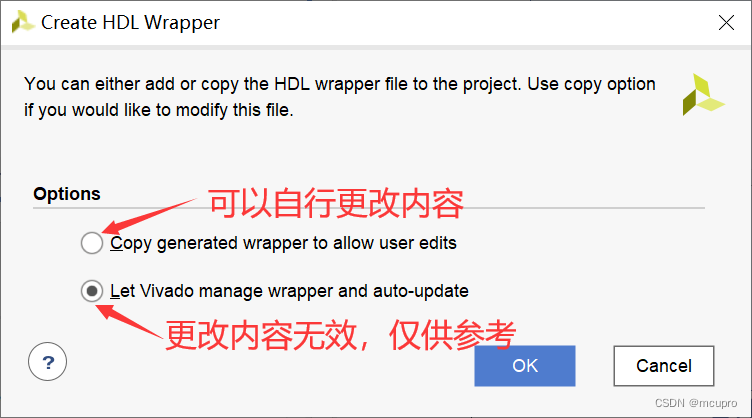

根据自己的需求进行选择,若需要对顶层进行更改,则选择copy...,若无需更改则选择Let...。选择Let时生成的顶层文件不可自行更改,仅供设计者进行查看,编译时不会编译此文件。

本历程无需更改,这里选择Let

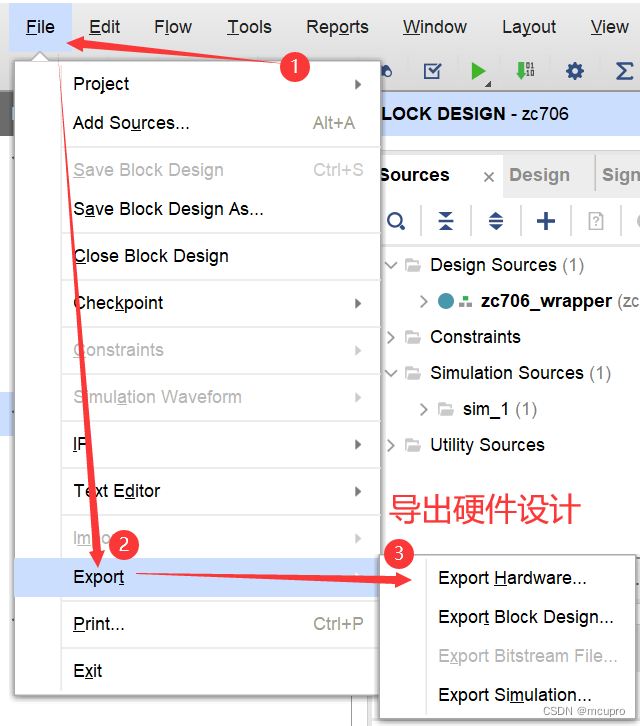

因为本例程只需要用到PS端,所以无需生成bit流,到处硬件设计即可

File-->Export-->Export...-->next-->next

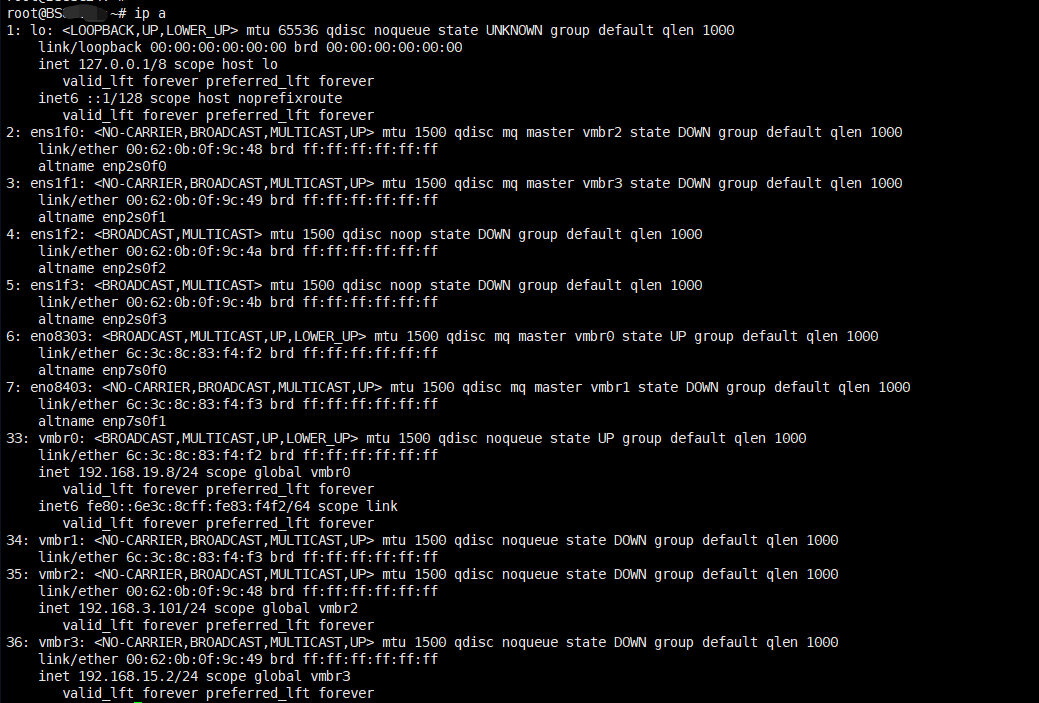

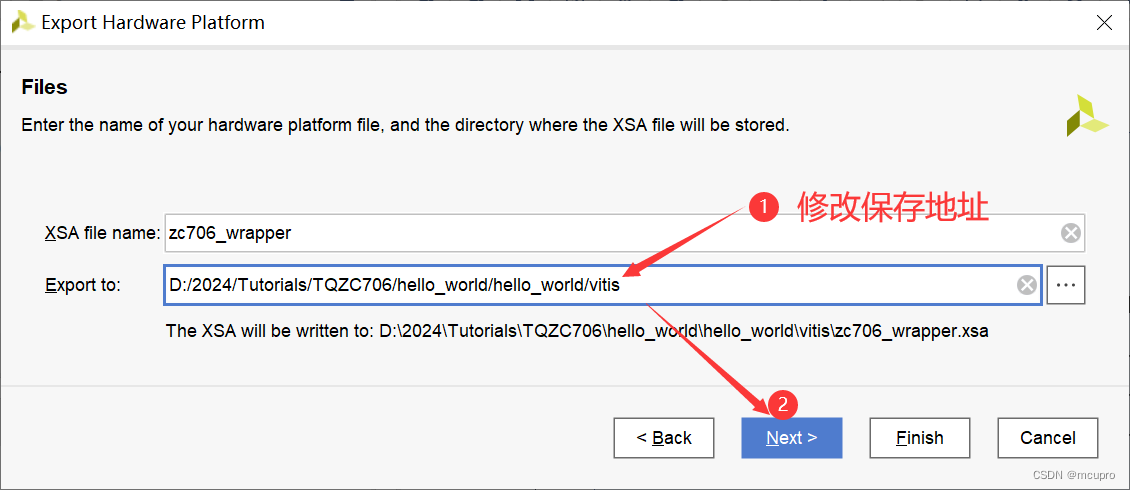

修改保存地址,我的建议是在项目目录下新建一个vitis文件夹,存放vitis产生的文件,可以直接在原来的地址后面添加 “/vitis”即可,方便又快捷

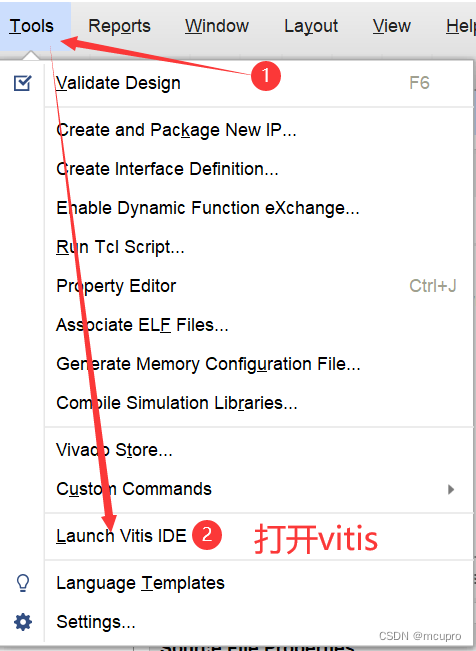

Tools-->Launch...,打开vitis

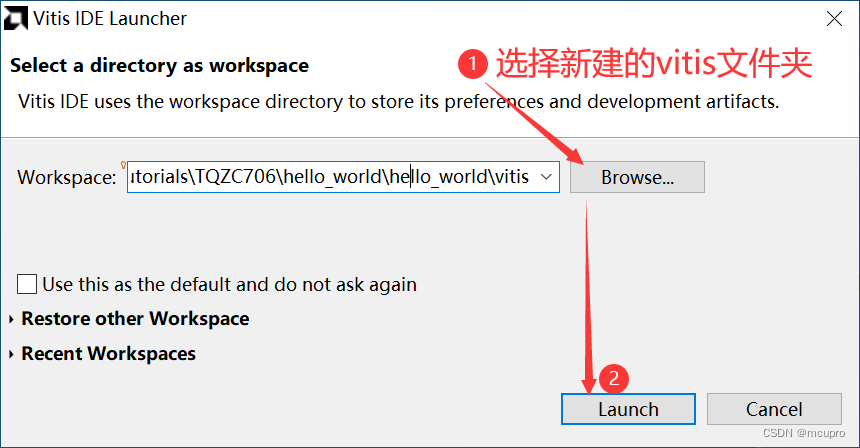

选择新建的vitis文件夹-->Launch-->若弹出窗口选NO

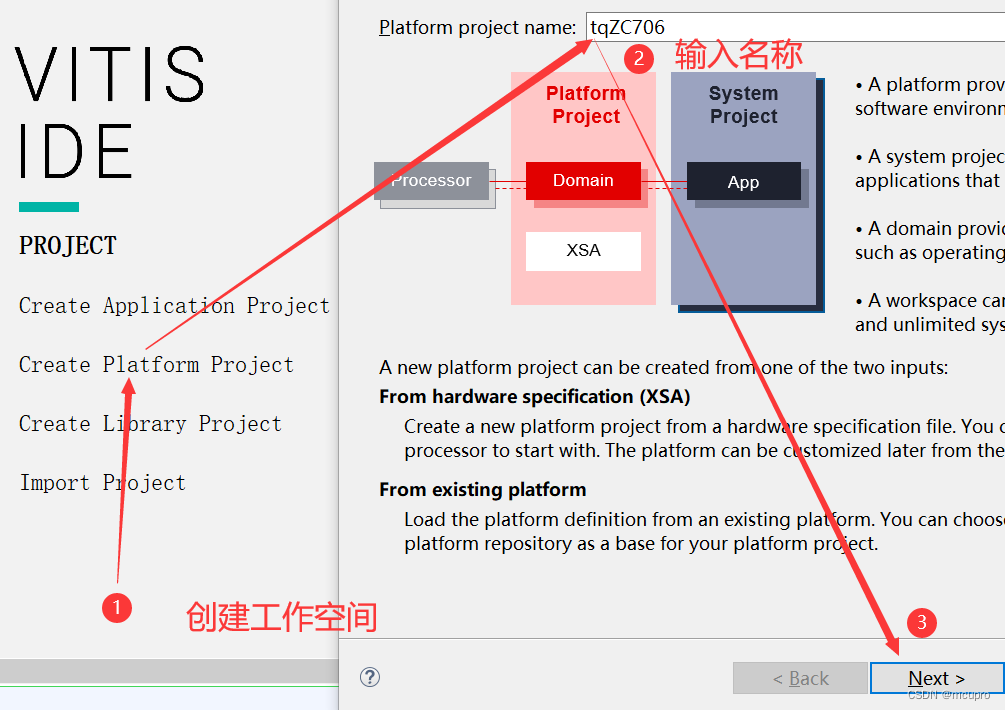

创建工作空间-->输入名称-->next

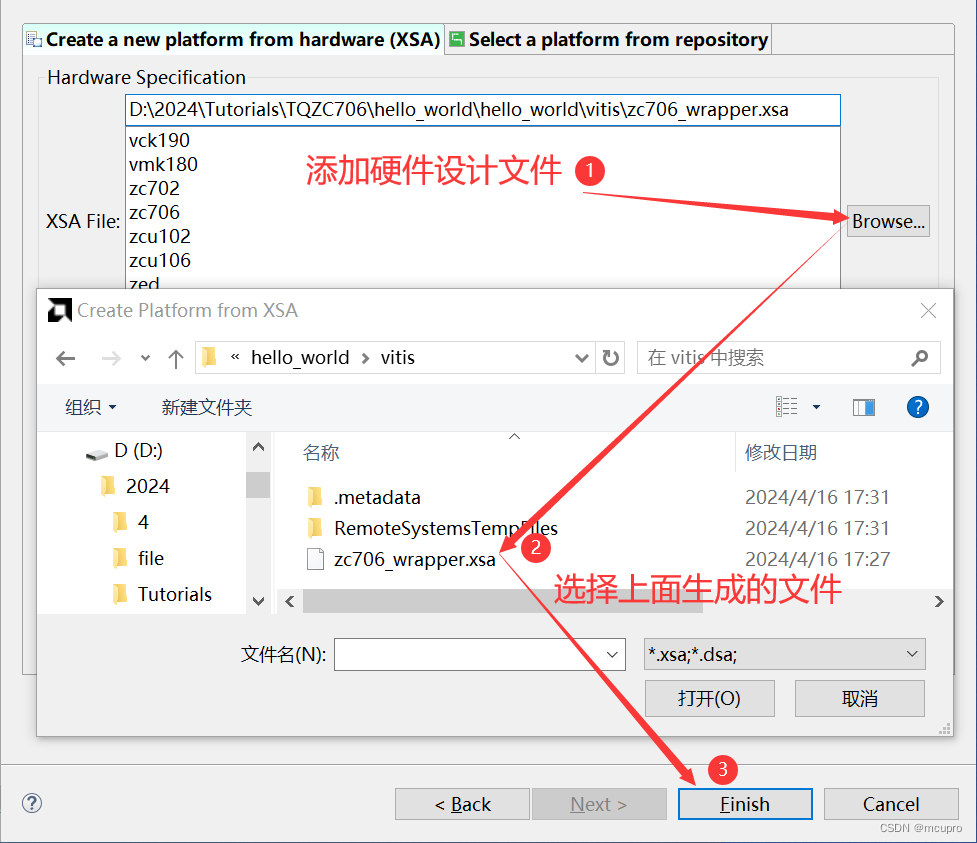

添加硬件设计文件-->选择上面生成的文件-->Finish

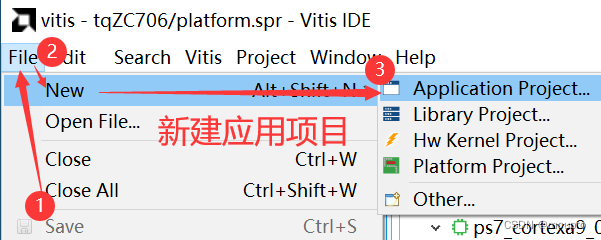

File-->New-->Application-->next-->next

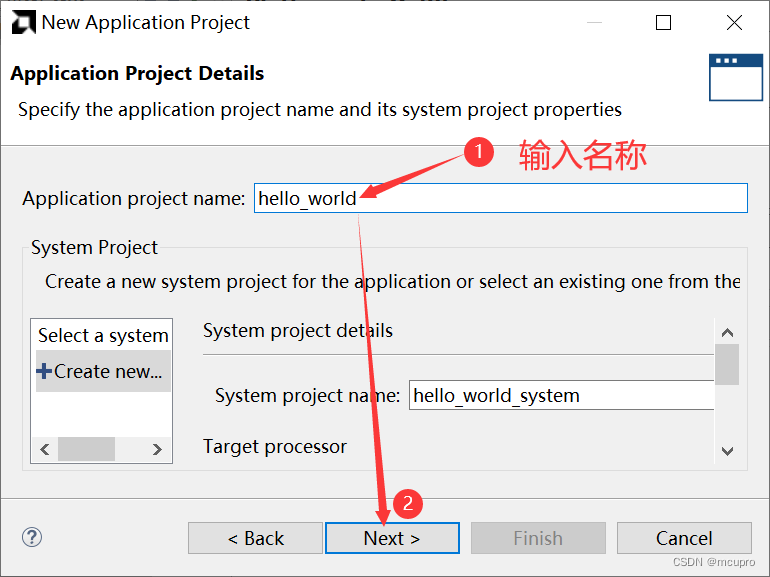

输入名称-->next-->next

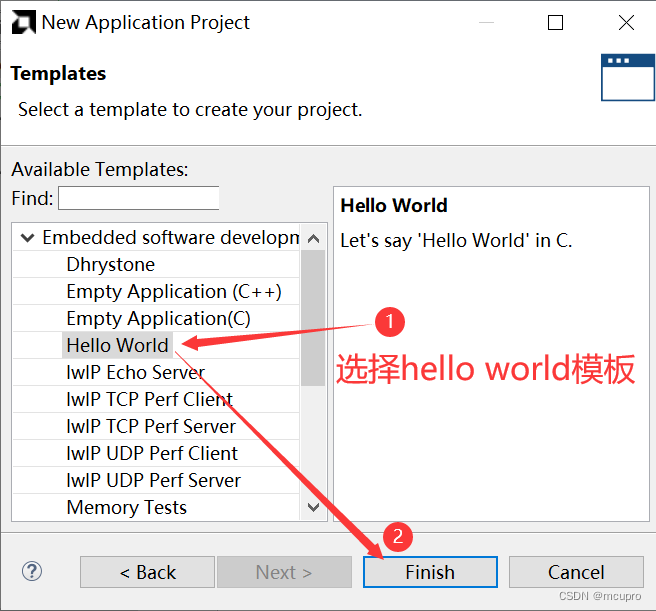

选择hello world目标-->Finish

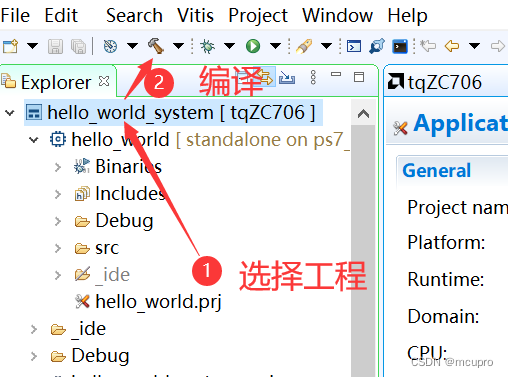

选择工程-->编译

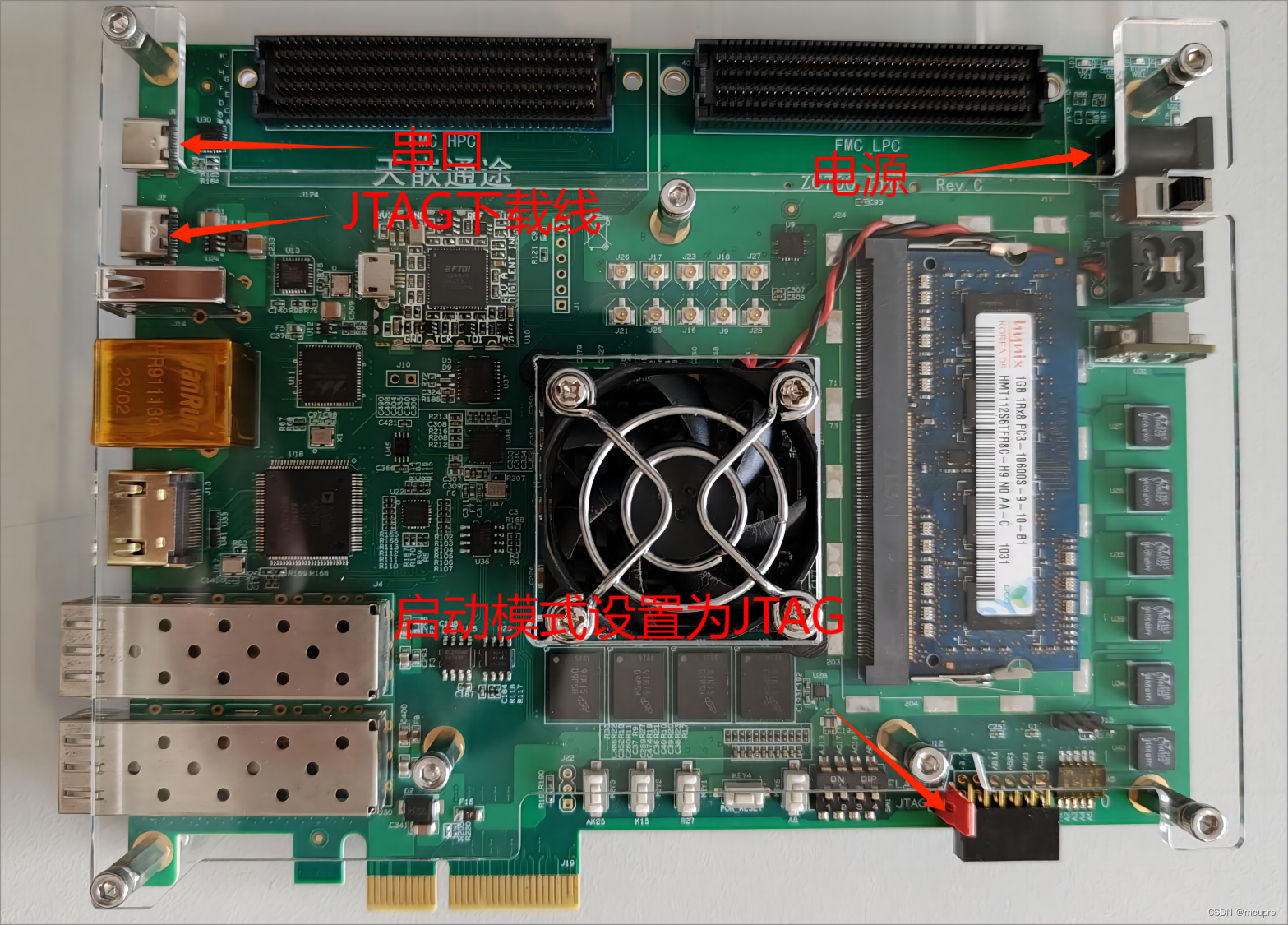

给开发板接上串口,JTAG,电源线,启动模式设置为JTAG,开启电源开关,打开串口软件,注意开发板串口接入电脑后会识别出两个串口,因为暂时不知道从那个串口输出,所以需要同时打开

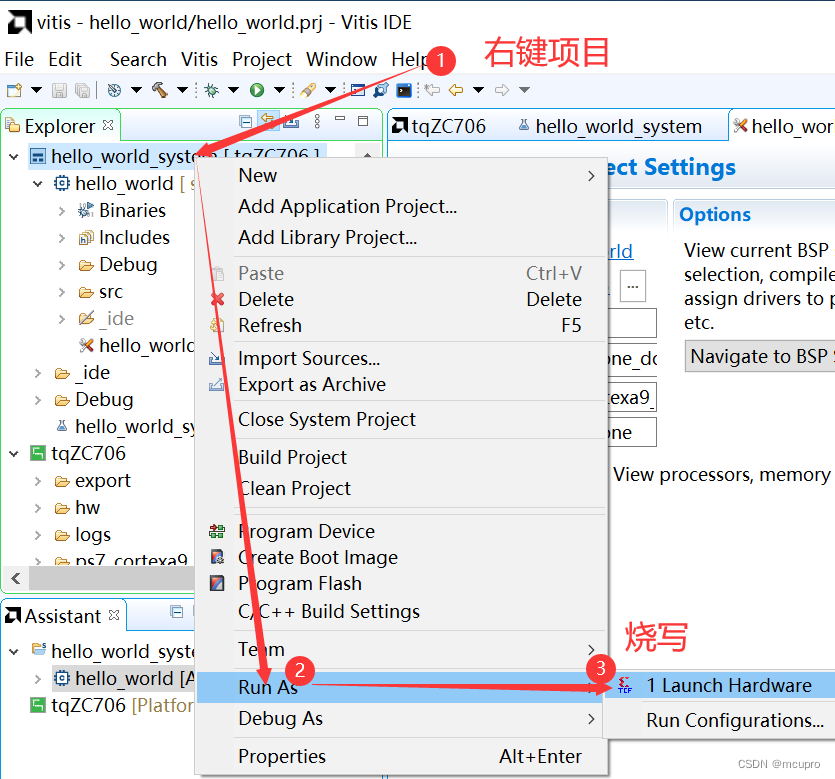

右键项目-->Run As-->1 Launch...,烧写程序

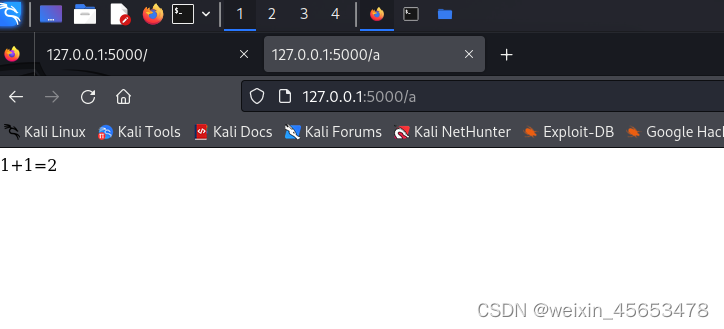

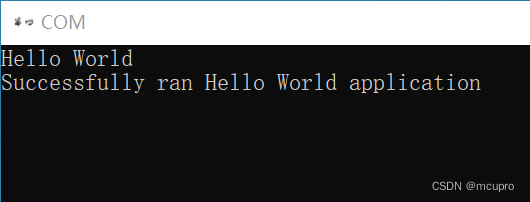

可以看到串口有输出

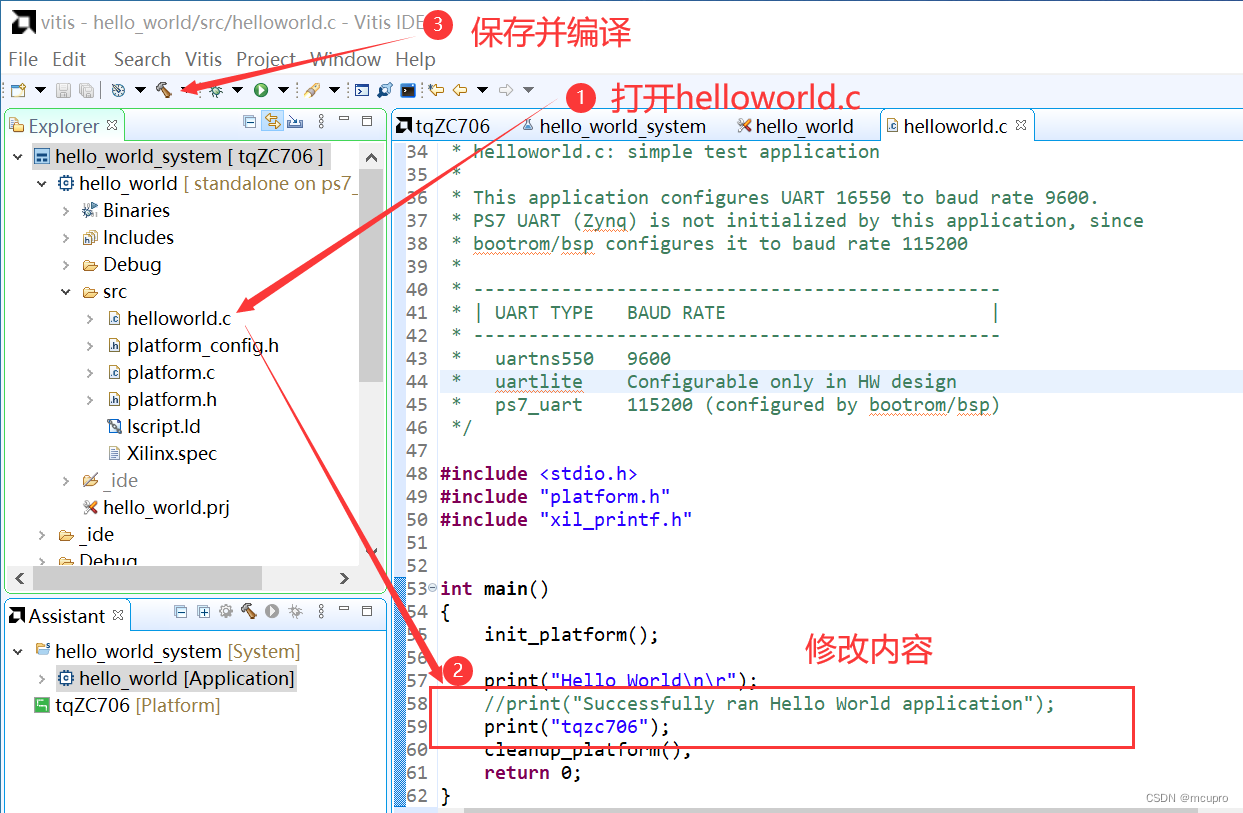

打开helloworld.c文件-->修改内容-->保存并编译

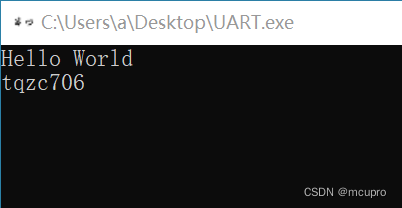

再次烧写,查看串口输出内容

工程项目链接

链接:https://pan.baidu.com/s/1unVbF3S0QJcwH3LdSbn-jg

提取码:yi8n