全部学习汇总: GreyZhang/g_TC275: happy hacking for TC275! (github.com)

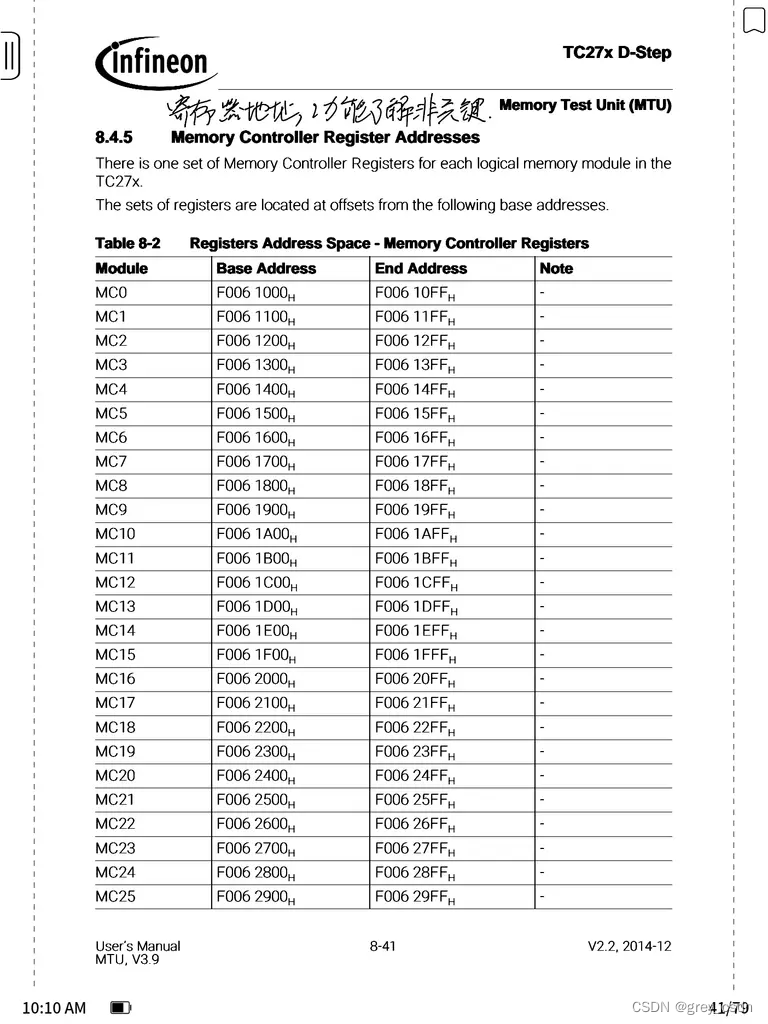

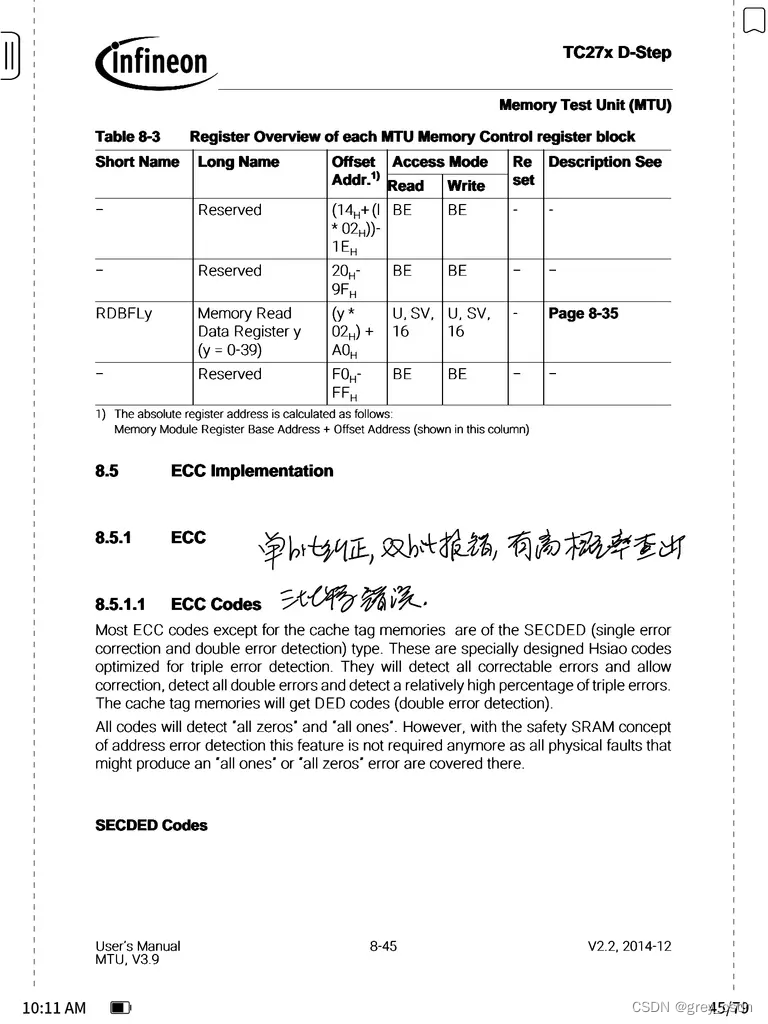

这一夜的信息全是寄存器地址信息,在了解功能的时候都是非关键信息。后续的内容整理中,这部分类似的信息我都会跳过。

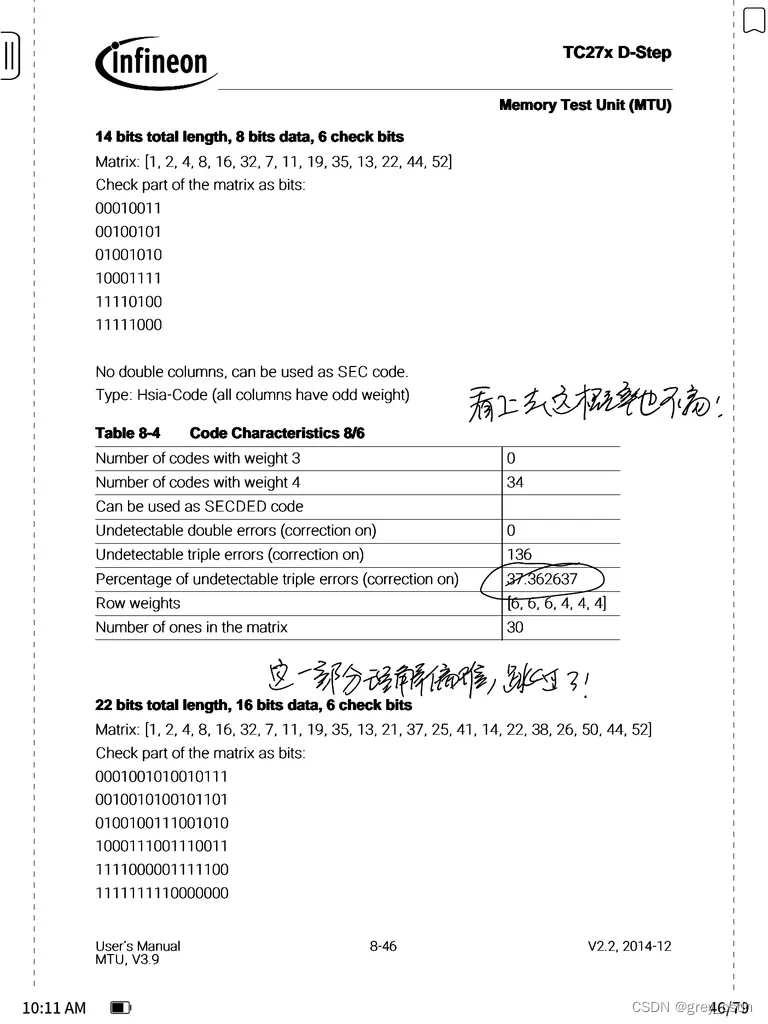

在这个系列的MCU中,ECC实现了单bit纠正、双bit报错,还有很高的概率检查出来3bit的错误。

- 从检测出来的百分比看,这个百分比也不是很高。前面居然描述了有很高的概率可以检测出来三重错误,或许是三bit错误。可能,解决这样的问题本身就是一个很难的技术吧。

- 关于ECC的实现机制实在是没看懂,这是第二次与这个技术描述相遇了,暂且还是跳过吧。

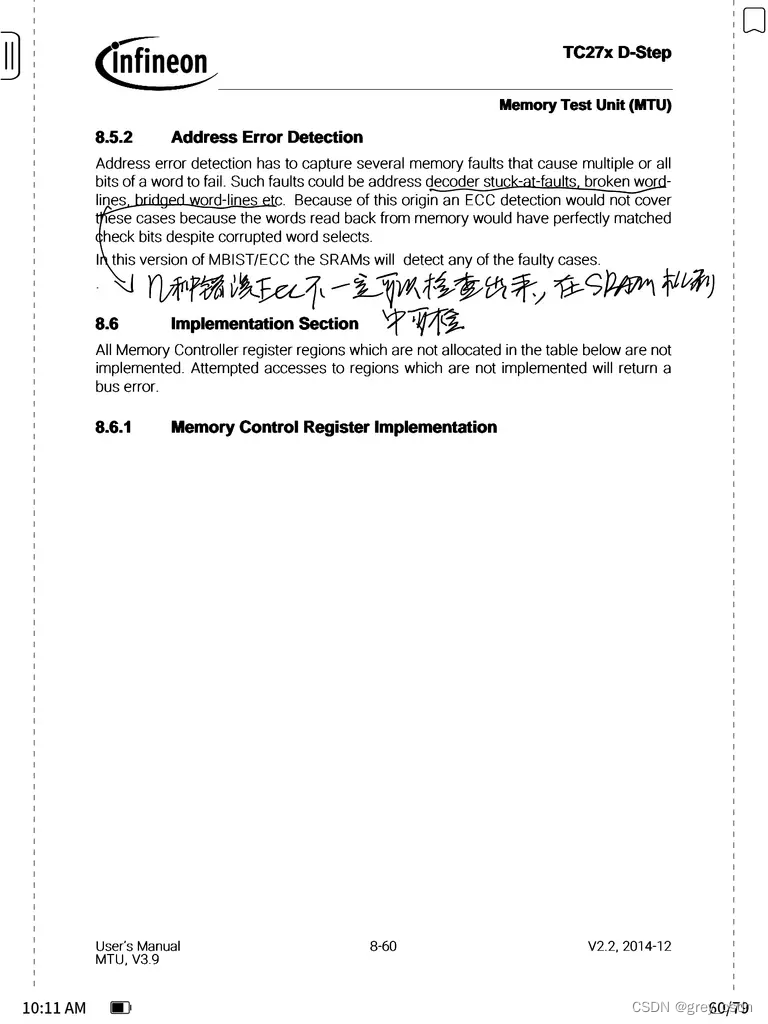

还有几种错误ECC不一定能够检查的出来,比如解码器卡主、word线损坏、桥word线损坏等。这些在SRAM的机制中可以进行检测发现。

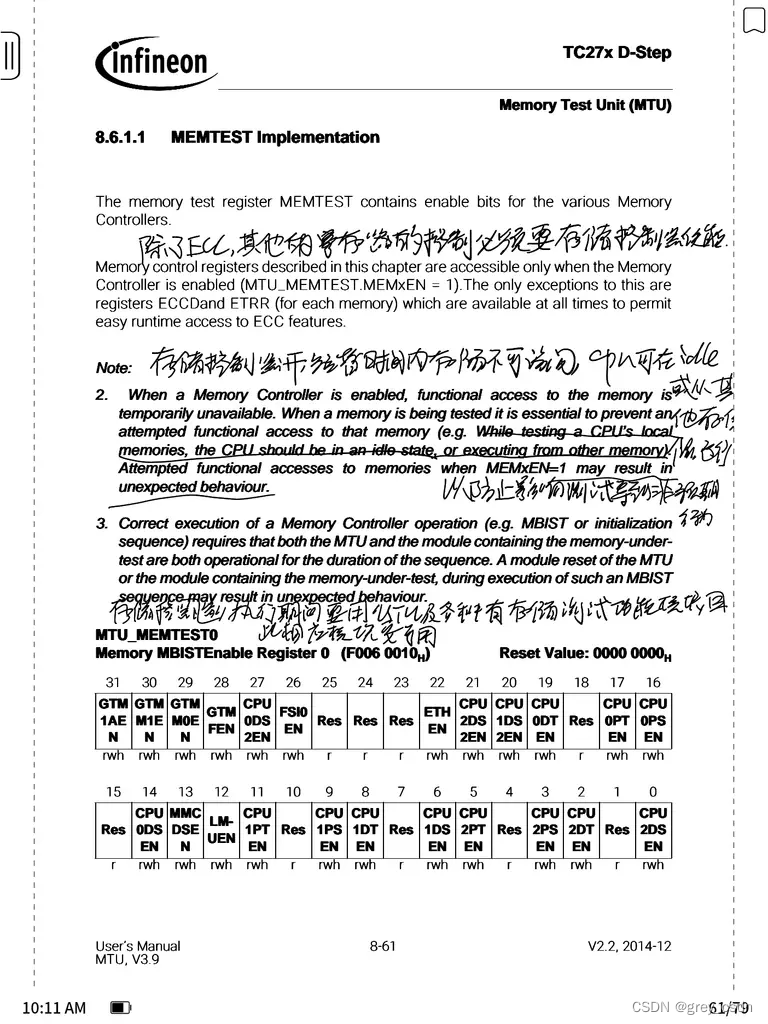

- 除了ECC相关的功能外,其他的寄存器的控制必须要先使能存储控制器。

- 存储控制器使能后,短暂时间内存储不可访问。CPU可以进入idle模式或者通过不属于这个存储控制器管理的存储启动,以免MTU初始化等对自检功能造成影响。如果在使能的时候访问存储,可能会导致不可预期的行为。

- 存储控制器在执行期间会用到MTU以及各种有存储测试功能的模块,因此需要相应的模块可用。

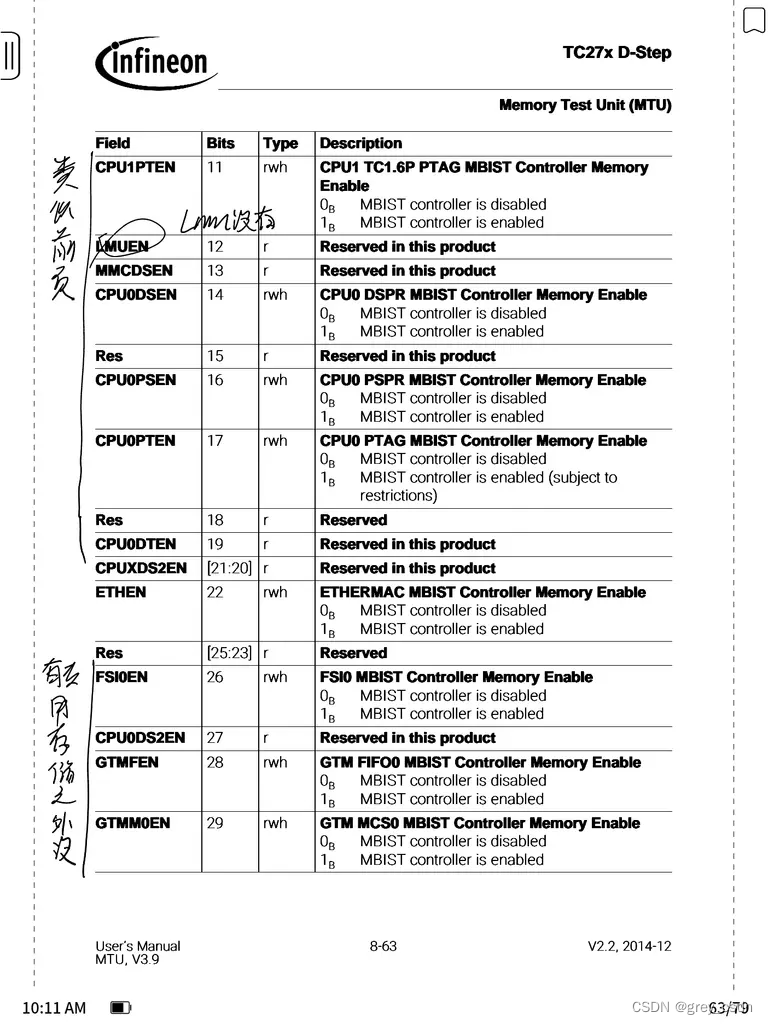

这里的使能按照数据TAG、PSPR、PTAG、DSPR等为每一个CPU进行了相应的细化拆分。

- 这一页的信息跟前吗的很多部分是类似的,但是需要注意的是LMU是没有专门的使能的。

- 有些有专用存储的外设,也有相应的专用使能位。

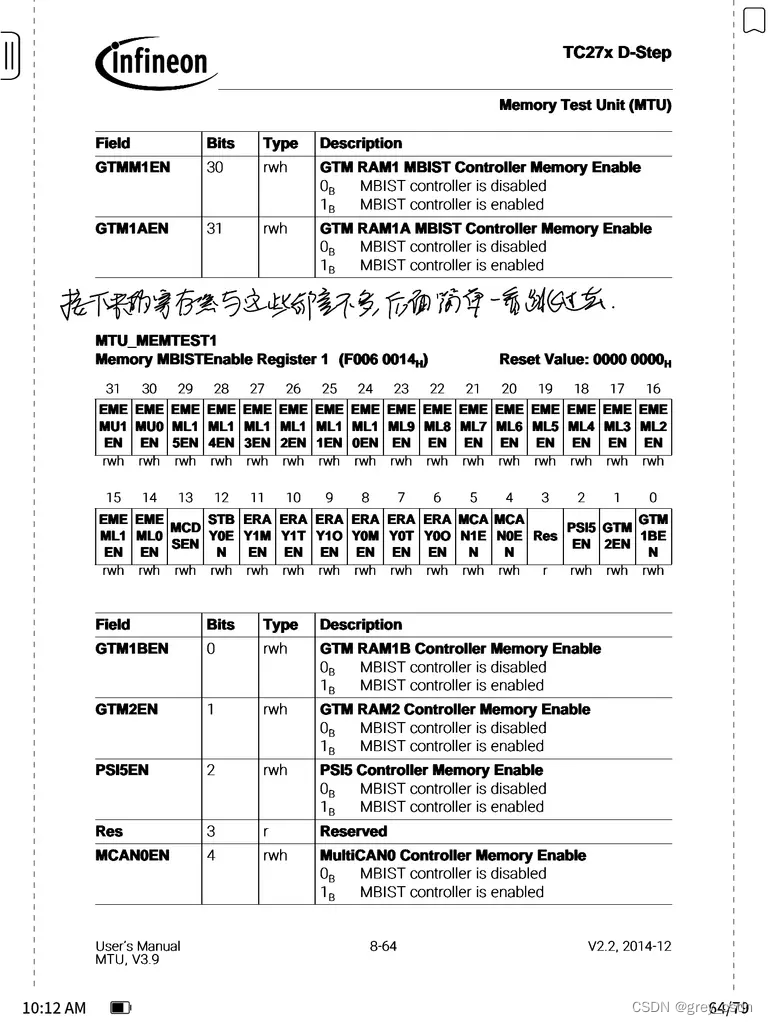

接下来的寄存器而极少与这些都差不多,后面简单看一下直接跳过整理。

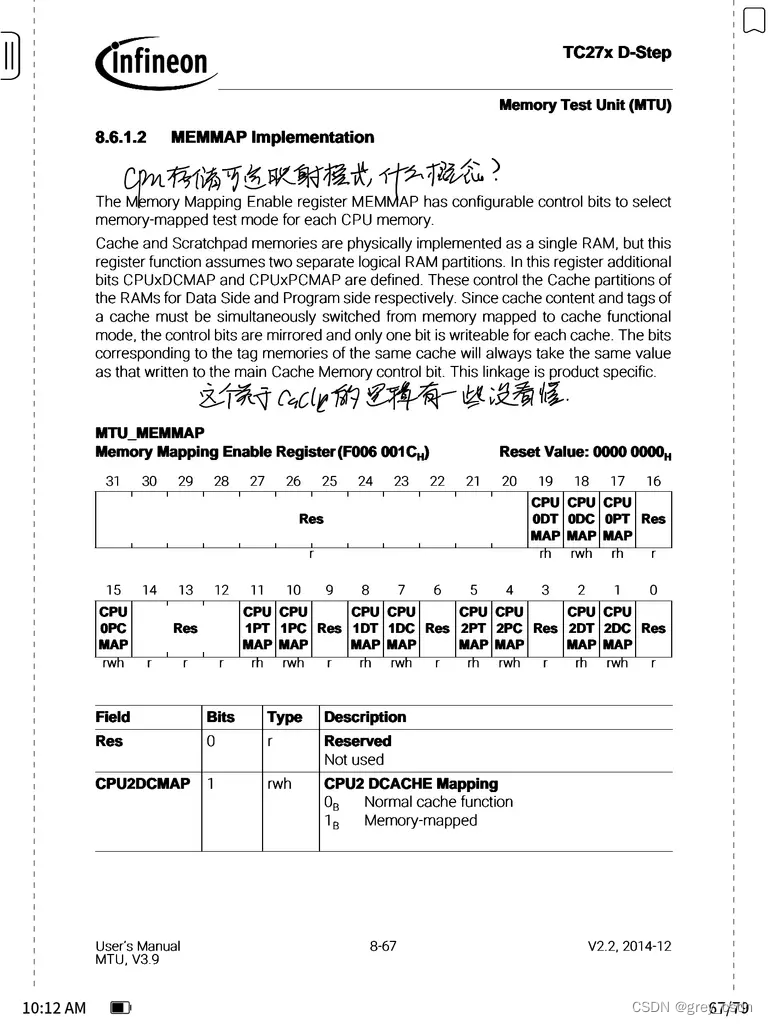

- 这里又出现了一个概念,CPU存储可选择映射模式。在这里专门出现,应该不会跟overlay或者MMU有什么关系,那么表达的是什么概念呢?

- 进一步的解释中,介绍了很多CaChe相关的设计,有些没看懂。

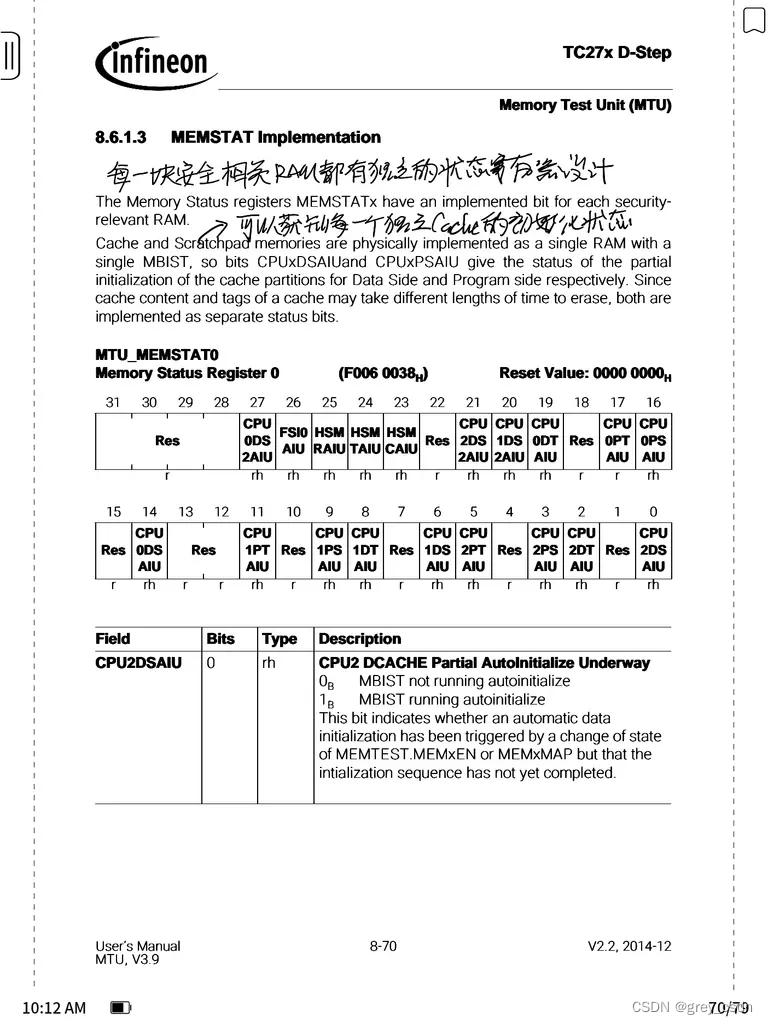

- 每一块安全相关的RAM都有独立的状态寄存器设计。

- 可以获知每一个独立CaChe的初始化状态。

这样,MTU的相关内容基本就看完了。看的过程有些仓促,效果也有一些模块。但是对这个模块的基本功能有了一点概念上的了解,后续如果再进行相关功能模块的使用或者调试的时候或许不至于太被动。