系统软件设计

4.1

引言

本章基于第二章的分析结论,进行系统软件设计。软件设计包括逻辑设计、嵌入

式软件设计和上位机软件设计。在逻辑设计中,对

ADC

模块、

Aurora

模块、

DDR3

SDRAM

模块和

PCIE

模块进行分析和设计,在

Vivado

软件提供的

IP

核的基础上进

行各模块的逻辑代码的编写,并解决各个模块之间数据连接的问题;嵌入式设计是对

系统和内核的移植,并在

Zynq

的

PS

内核实现系统的启动;在上位机设计中,首先

介绍驱动开发工具,再介绍上位机的整体设计。

4.2

逻辑软件设计

由于载卡的

FMC

接口数据与接入的子卡类型有关,根据接入的子卡类型选择

ADC

模块或

Aurora

模块,当选择

AD

子卡时,使能

ADC

模块,当选择光纤子卡时,

使能

Aurora

模块。对应的模块数据经

DDR3 SDRAM

缓存后,再由

PCIE

接口发送至

PC

机,数据流向如图

4.1

所示。

其中,

ADC

模块是

AD

子卡的驱动程序,可提供

1Gsa/s

的采样率,数据分辨率

为

12bit

;

Aurora

模块是光纤子卡的驱动程序,采用

Aurora

协议,

4

通道,单通道速

率为

10Gbps

,总速率为

40Gbps

;

PCIE

接口采用

PCIE2.0

协议,

x8

模式,单通道速

率为

5.0Gbps

,总速率为

40Gbps

;

DDR3 SDRAM

模块用来实现对

Aurora

数据或

ADC

数据进行缓存。

Vivado

软件内提供

Aurora

、

PCIE

和

MIG

的

IP

核,分别为

Aurora

协

议、

PCIE

协议和

DDR3 SDRAM

提供接口解决方案,下面对各个模块进行详细设计。

4.2.2

ADC

模块逻辑设计

AD

子卡的

ADC

芯片采样率最大为

1.6Gbps

。而在第二章指标分析中,

ADC

的

采样率不得低于

706.6Msa/s

,在本次设计中,设置

ADC

的采样率为

1Gsa/s

。

ADC

芯

片工作在双边沿采样的模式,这样采样率可以是采样时钟的两倍。需要产生

500MHz

的差分时钟信号,用

Zynq

芯片内部的

MMCM

资源可产生

500MHz

的单端时钟,再

利用

Xilinx

提供的

OBUFDS

原语把单端时钟转换成差分时钟输出。

由于

ADC

工作在双边沿采样,需要拉高

ADC

芯片的

DES

引脚;信号耦合方式

是交流耦合,需要设置

VCMO

引脚为低电平。在双边沿工作模式下,

ADC

芯片可以

选择多路复用模式,多路复用模式可以实现数据线的复用,多路复用模式的时序图如

图

4.2

所示

[25]

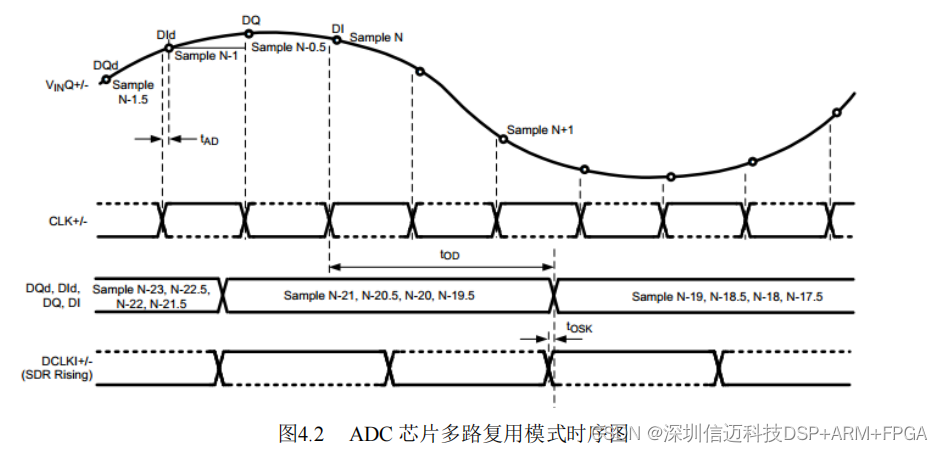

。

图中,

CLK+/-

是采样时钟信号,

DQd

,

Did

,

DQ

,

DI

是

ADC

的数据线,

DCLKI+/-

是通道

I

的数据同步输出时钟。由图可知,

ADC

工作在双边沿采样模式,多路复用模

式时,完成

4

次转换后,数据依次轮流输出至

DQd

,

Did

,

DQ

,

DI

。同时在

DCLK+/-

上输出一个转换时钟二分频的信号,这里为

250MHz

。

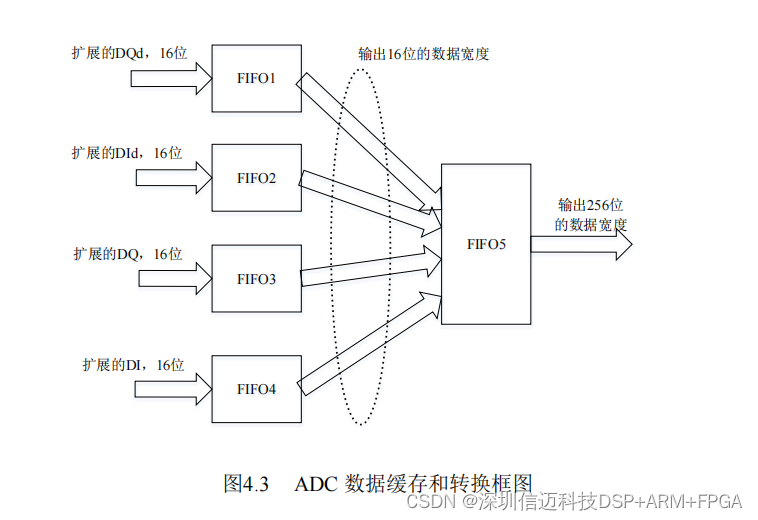

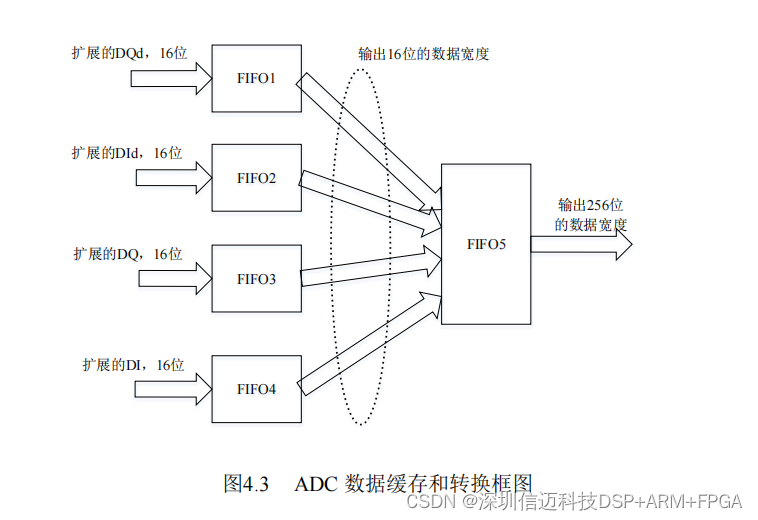

由于数据位宽是

12bit

,但是

DDR3 SDRAM

模块的

FIFO

宽度为

256bit

,两者不

成整数倍关系。这里解决办法是把各个数据通道的

12bit

扩展成

16bit

,然后分别保存

至小的

FIFO

里,再用一个

FIFO

输出

256bit

的数据宽度。数据流缓存框图如图

4.3

所

示。其中,

FIFO1~FIFO4

是读写位宽都为

16bit

的同步

FIFO

,

FIFO

时钟为

ADC 芯片

出来的

DCLK+/-

时钟,经差分转单端后的时钟,

4

个

FIFO

输出的数据写入至

FIFO5

里面,

FIFO5

是写数据位宽为

64bit

,读数据位宽为

256bit

的异步

FIFO

,可以直接与

DDR3 SDRAM

模块连接。

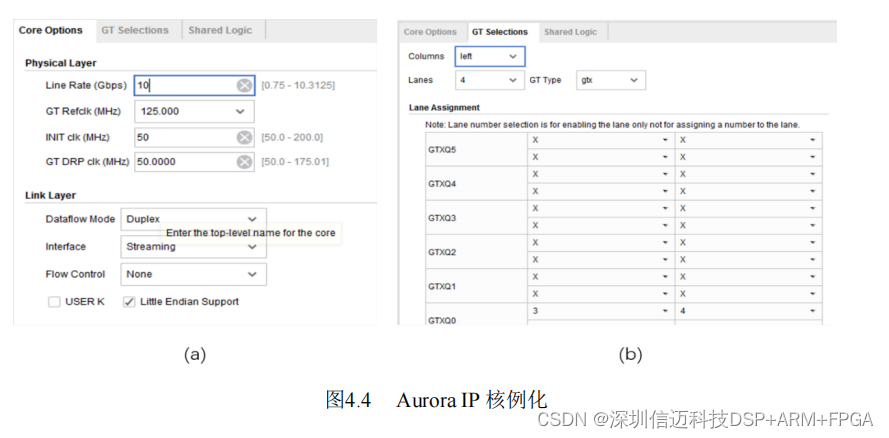

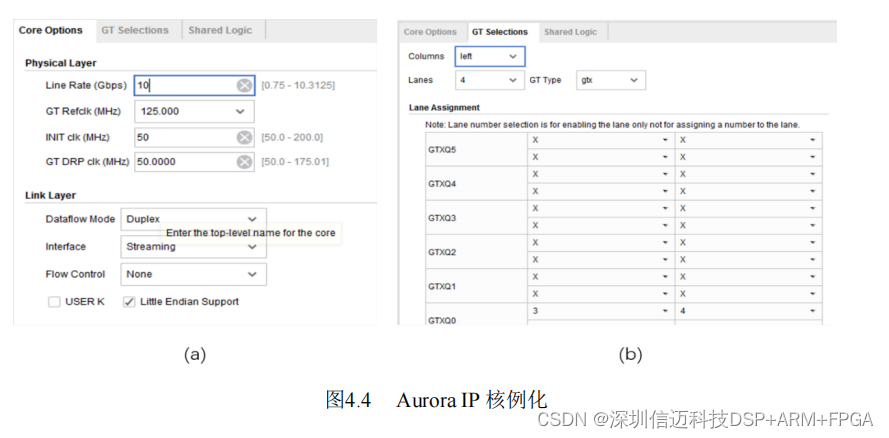

光纤接口采用

Aurora

协议,有

4

个通道,单通道速率为

10Gbps

,总速率为

40Gbps

。

光纤接口的数据传输时基于

Vivado

软件提供的

Aurora

协议的

IP

核实现,该

IP

核有

8B/10B

和

64B/66B

两种,分别对应相应的编码方式。本设计采用

64B/66B

编码,增

加了带宽利用率。核例化过程如图

4.4

所示。

例化核时,首先指定传输速率,这里设置为

10Gbps

。根据硬件电路设计,这里

的参考时钟设置为

125MHz

,传输采用全双工流模式,方便设计和使用。然后指定通

道在芯片上的映射关系。

例化后的核如图

4.5

所示。

![[嵌入式系统-33]:RT-Thread -18- 新手指南:三种不同的版本、三阶段学习路径](https://img-blog.csdnimg.cn/direct/8f13e2ae00a346afaf1720ea4c921455.png)

![Python算法题集_实现 Trie [前缀树]](https://img-blog.csdnimg.cn/direct/5a897d6e99aa4f639286febc56714d68.png#pic_left)