介绍

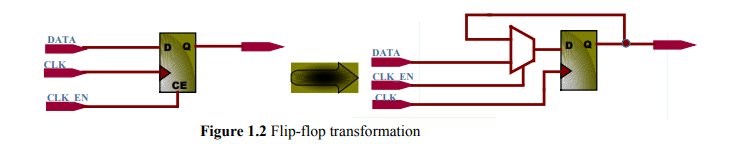

重定时(Retiming)是一个智能过程,通过组合延迟路径向后和/或向前移动和平衡寄存器以获得最佳定时,同时保持电路的功能行为。重定时算法可以在不考虑互连延迟的情 况下,在同一边沿上由一个时钟对电路进行定时时找到时钟周期的最佳解决方案。触发器可以从组合组件 的每个输入边移动到组件的每个输出边。这样的举动可以减少与触发器相关的关键路径延迟。但是,它每 次只能移动一个组合组件,因此该算法提供的时序改进非常有限。对于每种特定的 FPGA 架构技术,互连 延迟和打包规则也有许多限制。 当今的 FPGA 综合工具开发的当前重定时算法正在努力解决和增强这些限 制以获得更好的定时性能。

流水线(Pipelining)是另一种优化技术,涉及将逻辑划分为多个阶段,以便第一阶段可以开始处理新输入,而最后一个 阶段正在完成先前的输入。这确保了更好的吞吐量和更快的电路性能。对于流水线,一些综合工具实际上 可能会在从主要输入到主要输出引脚的周期或延迟路径中引入更多寄存器,从而为设计增加时钟延迟周期。

FPGA综合工具如何实现和利用重定时功能?

重定时和流水线是强大的技术,广泛应用于当今的 FPGA 综合工具中,以提高时序电路的时序性能。流水 线可以智能地用于平衡寄存器并将其从主 I/O 移动到分区逻辑中,而不会给原始设计引入任何额外的时钟 延迟。通过在重定时和流水线之间进行深思熟虑的集成过程,它可以证明是 FPGA 综合工具获得最佳时序 性能的一种非常有效和高效的技术。其中一些术语常用于重定时。

前向重定时是跨组合路径向前移动寄存器的过程。在图 1.0 中,前向重定时将 REG_IN 向前移动到任一组合运算符,具体取决于时序松弛和约束。

向后重定时正好与前向重定时相反,前向重定时是跨组合路径向后移动寄存器的过程。在图 1.0 中, REG_PL1 将根据时序松弛和约束向后移动到任一组合运算符。

在图 1.0 中,可以通过将 REG_PL1 和 REG_PL2 手动编码到 RTL 行为中来对电路进行流水线处理。将流水线寄存器手动编码为加法器或减法器运算符可能是可行的,但不适用于乘法器。

即使,如果它们都可以手工编码,让工具自动执行这项工作仍然会更有效率。第一种场景,如果重定时引擎只能进行前向重定时;原来的电路可以改善 5 ns(从 15 到 10 ns)。第二种情况,如果重定时引擎能够向前和向后移动寄存器,则时序可以改进 10 ns(从 15 ns 到 5 ns)。关键在于,根据重定时引擎的能力,最终的时序结果可能相当可观。

对于一个好的重定时引擎,图 1.0 中的原始电路将转换为图 1.1 中的电路。在确保原始 I/O 行为的同时, 时序改进了 10 ns(15 至 5 ns)。人们甚至可以对图 1.1 进行进一步改进。这可以通过在其中一个操作 员内部而不是在它们之间进行切割来增强。

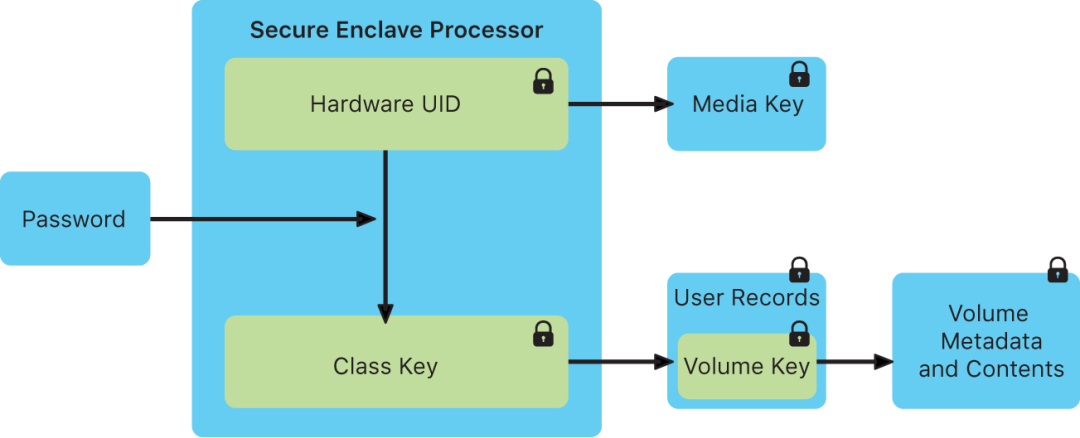

由于 FPGA 提供了这种寄存器丰富的架构,因此利用重定时技术来提高时序电路的时序性能更加合适和适 用。最近由 FPGA 综合工具实现的一些重定时技术提高了使更多时序电路元件符合重定时功能的能力。根 据某些 FPGA 综合工具的不同,一些当前不合格的用于重定时的时序电路可能会有所不同。通常,具有不 同时钟启用 (CE) 线的寄存器、具有不常见的设置/复位信号的寄存器或具有复杂控制信号的寄存器不符合 重定时条件。

由 Klaus Echl、Jean Christophe Madre、Peter Zepter 和 Christian Legl [2] 提出的称为多类重定时 的新方法的一些技术可以在当今的 FPGA 综合工具中非常有效地实现和实施。如图 1.2 所示,将不符合重 定时条件的寄存器转换为可以重定时的寄存器是正在考虑的技术之一。

在当今的大多数 FPGA 架构中,延迟路径可以来自组合电路等资源,这些资源基本上映射到 LUT(查找 表),也可以来自存储器、乘法器和任何非时序单元等专用资源。具有 K 输入和单个输出的查找表能够 实现任意定义的 K 输入布尔函数。大多数组合电路都是使用这些 LUT 功能实现的。通常为快速算术运算提供专用的快速先行进位逻辑。

FPGA 综合工具对由这些不同逻辑块组成的路径进行重定时的有效性和效率完全取决于其重定时算法。这就 是重定时挑战真正呈现给综合工具的地方。如前所述,最终结果可能非常重要,具体取决于重定时算法的 实施情况。

在 FPGA 综合工具中,可以仅使用 LUT 或基于进位逻辑的 LUT 或使用专用资源(例如块乘法器或专用 DSP 块)来实现算术运算符。

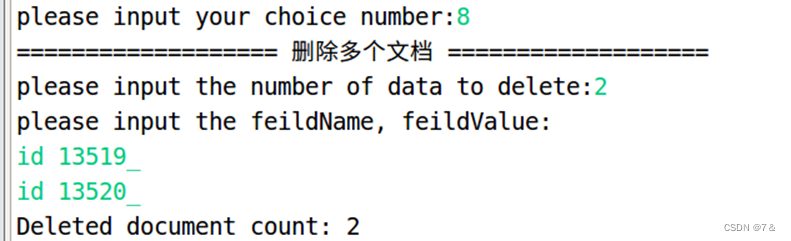

在图 1.3 中,假设 OPERATOR_1 映射到仅 LUT 逻辑,OPERATOR_2 映射到 LUT 和进位逻辑,OPERATOR_3 映射到指定的块乘法器。从这个简单的图示中,最有效的重定时位置是在 OPERATOR _2 和 OPERATOR _3 之间,这会将寄存器到寄存器的时序从 10 ns 减少到 5 ns。在第一种情况下,如果综合工具不具备跨运 算符重定时的功能,则该电路根本不会重定时。在第二种情况下,如果综合工具无法对任何由 LUT 和进位 逻辑实现的运算符进行重定时,则 OPERATOR _2 将被排除在重定时之外。重定时引擎必须针对每种特定技 术最大化和扩展其合格电路。重定时引擎必须具备的另一个重要特性是准确可靠的时序表征例程。否则, 重定时可能会恶化原始电路的性能。 如图 1.3 所示,理想的重定时会将寄存器到寄存器的时序提高 100%, 前提是输入和输出延迟约束均大于 5 ns。

在 FPGA 综合流程中集成重定时

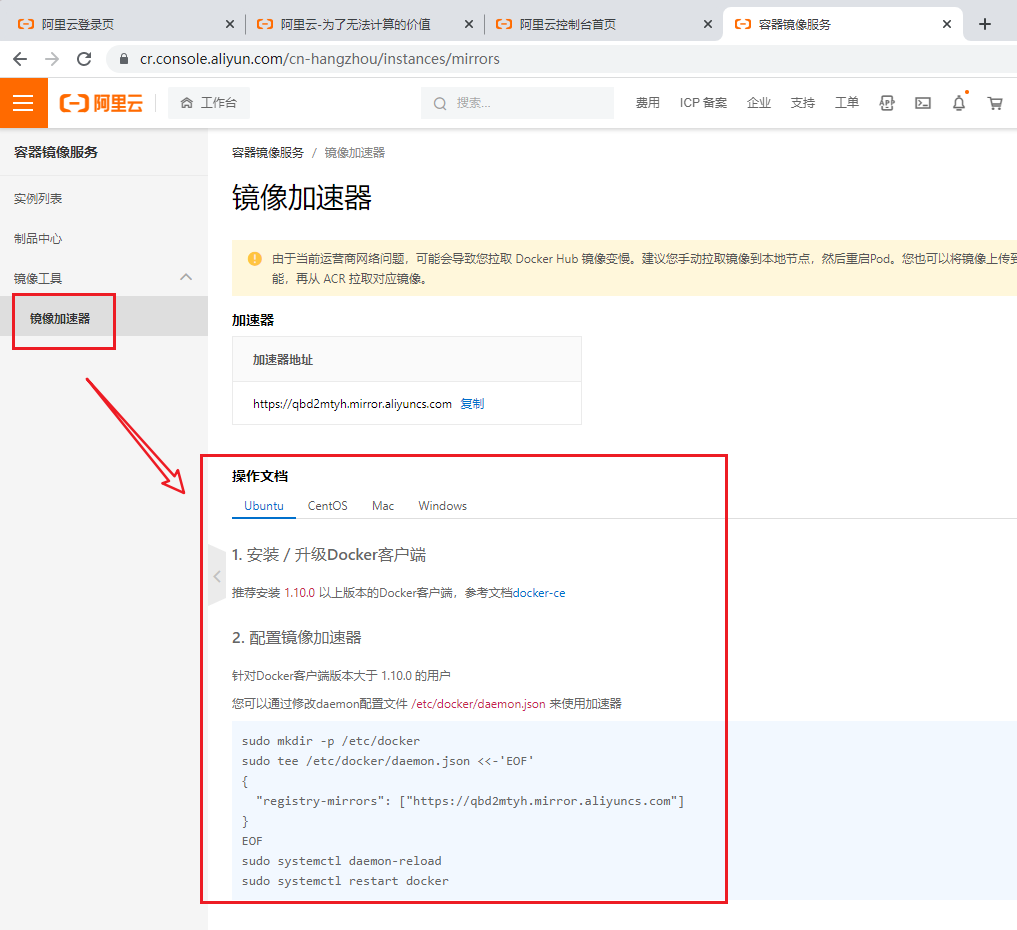

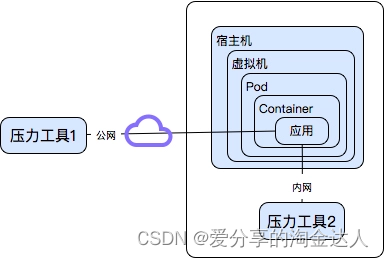

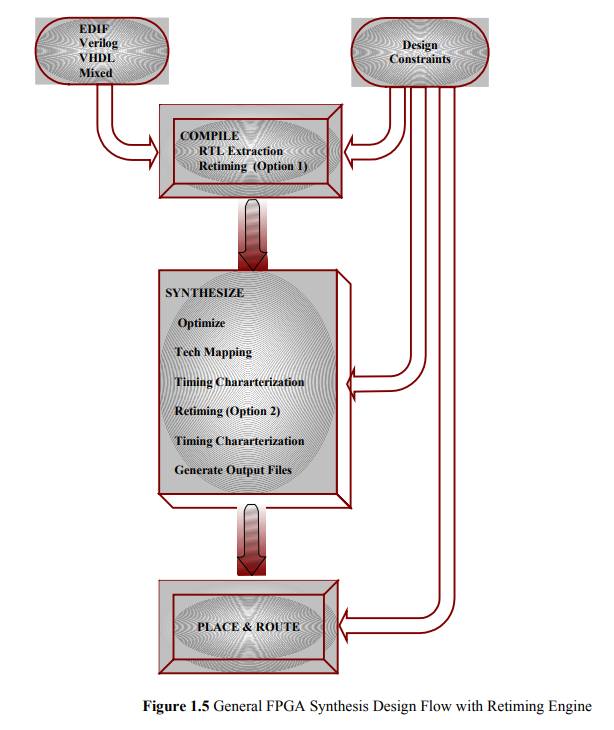

重定时引擎可以在不同阶段集成到 FPGA 综合工具中,具体取决于重定时算法的实现方式。从图 1.5 的选项 1 中,重定时是通过使用详细的网表执行的。一些综合工具已经使用此选项流程开发 和集成了它们的重定时引擎。由于每个 FPGA 供应商的专有映射和打包规则,对于 FPGA 架构技术 来说效率不是很高。使用这个精心设计的网表的另一大优势是时序特征可以通过设计到达映射阶段 的时序而发生相当大的变化。

另一方面,选项 2 在 FPGA 综合工具中很常见,因为重定时是在设计优化和映射之后执行的。重 定时引擎可以利用映射的网表并根据需要执行重定时。它可以在可能的情况下充分利用逻辑和物 理重定时算法。由于特定目标技术已经映射了网表,此阶段的时序表征要准确得多。

概括

重定时已被证明是在确保设计行为的同时提高时序性能的最有效和最可靠的技术之一。由于其寄存器丰富 的架构和其他通用特性,可以合理地得出结论,FPGA 设计可以从重定时例程中受益匪浅。

由于 FPGA 设计可能是技术特定的,重定时算法引擎面临着许多具有挑战性的任务。尽管存在所有这些具 有挑战性的障碍,重定时开发仍在继续非常有效地向前推进。

每个重定时算法都可以提供不同质量的结果,具体取决于它的开发和实现方式。 Mentor Graphics 的 Precision RTL Synthesis 和 Precision Physical Synthesis 工具具有显着先进的专利重定时引擎,该 引擎结合了寄存器复制、流水线和重定时(向后、向前、跨运算符和运算符之间)的优化技术,以帮助设 计人员实现更好的结果设计性能,对设计周期时间的影响最小。