什么是时钟,SoC为什么需要时钟

(1)时钟同步工作系统的同步节拍

(2)SoC内部有很多器件,譬如CPU、DRAM控制器、串口、GPIO等内部外设,这些东西要彼此协调工作,需要一个同步的时钟系统来指挥。这个就是SoC的时钟系统。

时钟一般如何获得?

(1)外部直接输入时钟信号,SoC有个引脚用来输入外部时钟信号:用的很少(有源晶振)

(2)外部晶振+内部时钟发生器产生时钟:大部分单片机(无源晶振)

(3)外部晶振+内部时钟发生器产生时钟+内部PLL倍频+内部分频器分频得到各种频率的时钟:S5PV210

为什么S5PV210使用第三种时钟?

(1)为什么不直接使用外部高频晶振产生高频信号给CPU?

主要因为芯片外部电路不适宜使用高频率,因为传导辐射比较难控制;高频晶振太贵了

(2)为什么要内部先高频然后再分频?

主要因为SoC内部有很多部件都需要时钟,而且各自需要的时钟频率是不同的,没办法统一供应。因此思路是PLL后先得到一个最高的频率(1GHz、1.2GHz),然后各外设都由自己的分频器来分频得到自己想要的时钟频率。

时钟和系统性能的关系、超频、稳定性

(1)一般SoC时钟频率都是人为编程控制的,频率的高低对系统性能的有很大的影响。

(2)S5PV210建议工作频率为800MHz~1.2GHz,一般我们都设置到1GHz主频。如果你设置到1.2GHz就叫超频。超频的时候系统性能会提升,但是发热也会增大,因此会影响系统稳定性。

时钟和外设编程的关联

每个外设工作都需要一定的时钟频率,这些时钟都是由时钟系统提供的。时钟系统可以通过编程控制工作模式,因此可以人为为每个外设指定时钟来源、时钟分频系统、从而制定这个外设的工作时钟。

时钟和功耗控制的关系

(1)SoC中各种设备工作时,时钟频率越高功耗越大,发热越大,越容易不稳定,需要外部的散热条件越苛刻。

(2)SoC内部有很多外设,这些外设不用的时候最好关掉(不关掉会一定程度浪费电),开关外设不是通过外设,而是通过时钟。。也就是说我们给某个外设断掉时钟,这个外设就不工作了。

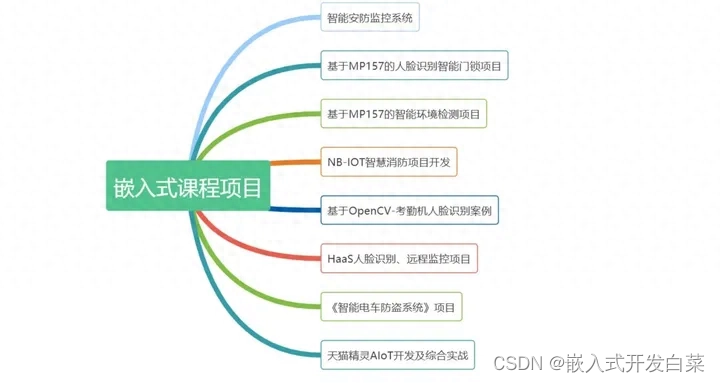

嵌入式物联网的学习之路非常漫长,不少人因为学习路线不对或者学习内容不够专业而错失高薪offer。不过别担心,我为大家整理了一份150多G的学习资源,基本上涵盖了嵌入式物联网学习的所有内容。点击这里扫码进群领资料,0元领取学习资源,让你的学习之路更加顺畅!记得点赞、关注、收藏、转发哦!