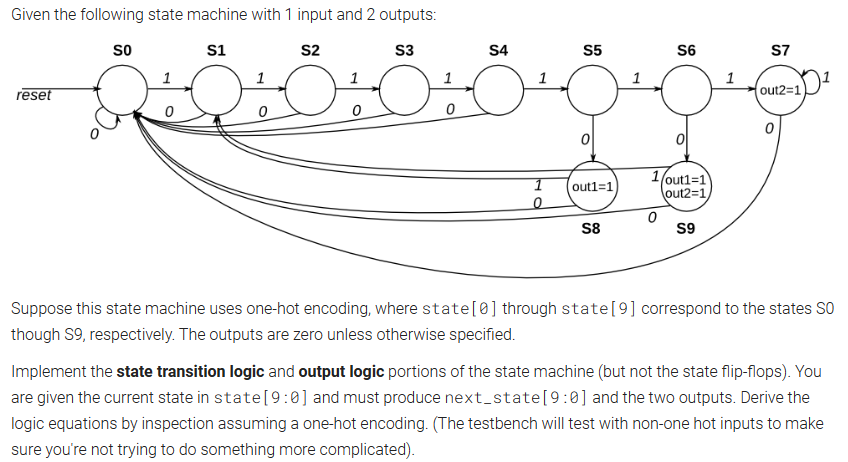

module top_module(

input in,

input [9:0] state,

output [9:0] next_state,

output out1,

output out2);

assign out1=(state[8]|state[9])?1:0;

assign out2=(state[9]|state[7])?1:0;

assign next_state[0]=(state[0]&(~in)) |(state[1]&(~in)) |(state[2]&(~in))

|(state[3]&(~in)) |(state[4]&(~in)) |(state[8]&(~in)) |(state[9]&(~in))|(state[7]&(~in));

assign next_state[1]=(state[0]&in) |(state[8]&in) |(state[9]&in);

assign next_state[2]=state[1]∈

assign next_state[3]=state[2]∈

assign next_state[4]=state[3]∈

assign next_state[5]=state[4]∈

assign next_state[6]=state[5]∈

assign next_state[7]=(state[6]&in)|(state[7]&in);

assign next_state[8]=state[5]&(~in);

assign next_state[9]=state[6]&(~in);

/* 不知道为啥不能这么写,大佬看到给点解答

parameter S0 = 10'b0000_0000_01,

S1 = 10'b0000_0000_10,

S2 = 10'b0000_0001_00,

S3 = 10'b0000_0010_00,

S4 = 10'b0000_0100_00,

S5 = 10'b0000_1000_00,

S6 = 10'b0001_0000_00,

S7 = 10'b0010_0000_00,

S8 = 10'b0100_0000_00,

S9 = 10'b1000_0000_00;

assign out1 = (state == S8 || state == S9);

assign out2 = (state == S7 || state == S9);

always@(*) begin

case(state)

S0:

if(in)

next_state <= S1;

else

next_state <= S0;

S1:

if(in)

next_state <= S2;

else

next_state <= S0;

S2:

if(in)

next_state <= S3;

else

next_state <= S0;

S3:

if(in)

next_state <= S4;

else

next_state <= S0;

S4:

if(in)

next_state <= S5;

else

next_state <= S0;

S5:

if(in)

next_state <= S6;

else

next_state <= S8;

S6:

if(in)

next_state <= S7;

else

next_state <= S9;

S7:

if(in)

next_state <= S7;

else

next_state <= S0;

S8:

if(in)

next_state <= S1;

else

next_state <= S0;

S9:

if(in)

next_state <= S1;

else

next_state <= S0;

default:

if(state == 0)

next_state <= state;

else

next_state <= S0;

endcase

end

*/

endmodule

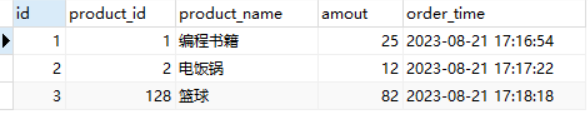

![[已解决]SpringBoot 返回日期时间格式不正确](https://img-blog.csdnimg.cn/d15bf979356c4f329826baf157440091.png)